# A4963GLPTR-T Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number A4963GLPTR-T-DG

Manufacturer Allegro MicroSystems

Manufacturer Product Number A4963GLPTR-T

Description IC MOTOR DRIVER 4.2V-50V 20TSSOP

Detailed Description Motor Driver Power MOSFET SPI 20-TSSOP-EP

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# **Purchase and inquiry**

| Manufacturer Product Number:                   | Manufacturer:                               |

|------------------------------------------------|---------------------------------------------|

| A4963GLPTR-T                                   | Allegro MicroSystems                        |

| Series:                                        | Product Status:                             |

| -                                              | Active                                      |

| Motor Type - Stepper:                          | Motor Type - AC, DC:                        |

|                                                | Brushless DC (BLDC)                         |

| Function:                                      | Output Configuration:                       |

| Controller - Commutation, Direction Management | Pre-Driver - Half Bridge (3)                |

| Interface:                                     | Technology:                                 |

| SPI                                            | Power MOSFET                                |

| Step Resolution:                               | Applications:                               |

|                                                | General Purpose                             |

| Current - Output:                              | Voltage - Supply:                           |

|                                                | 4.2V ~ 50V                                  |

| Voltage - Load:                                | Operating Temperature:                      |

|                                                | -25°C ~ 150°C (TA)                          |

| Mounting Type:                                 | Package / Case:                             |

| Surface Mount                                  | 20-TSSOP (0.173", 4.40mm Width) Exposed Pad |

| Supplier Device Package:                       | Base Product Number:                        |

| 20-TSSOP-EP                                    | A4963                                       |

|                                                |                                             |

# **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 2 (1 Year)                        |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

8542.39.0001

### Sensorless BLDC Controller

#### FEATURES AND BENEFITS

- Three-phase sensorless BLDC motor control FET driver

- Logic level P-N gate drive (P high-side, N low-side)

- 4.2 to 50 V supply range

- Simple block commutation for maximum torque

- · Sensorless (bemf sensing) startup and commutation

- Programmable operating modes:

- □ Integrated speed control

- □ PWM duty cycle control

- ☐ Current mode control

- Cross-conduction prevention

- Wide speed range capability

- Peak current limiting

- · Single low-frequency PWM control input

- Single open-drain fault output

- SPI-compatible interface providing:

- □ Configuration and control

- □ Programmable dead time

- □ Programmable phase advance

- □ Detailed diagnostic reporting

#### **APPLICATIONS**

- Pumps

- Fans

- Blowers

#### PACKAGE:

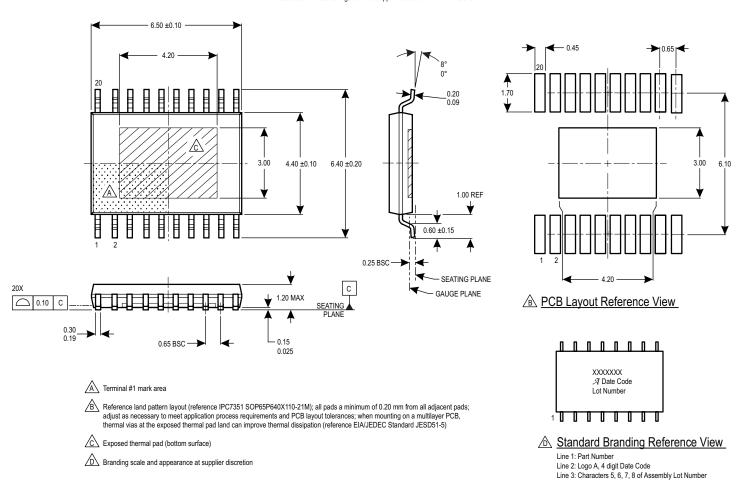

20-Pin eTSSOP with Exposed Thermal Pad (suffix LP)

#### DESCRIPTION

The A4963 is a three-phase, sensorless, brushless DC (BLDC) motor controller for use with external complementary P-channel and N-channel power MOSFETs.

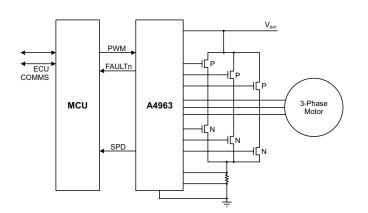

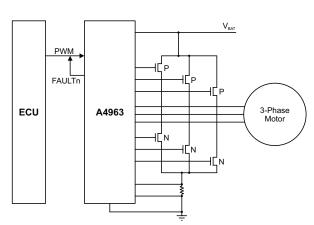

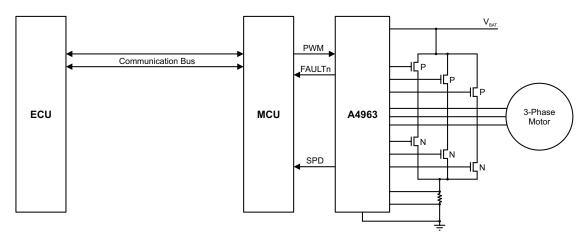

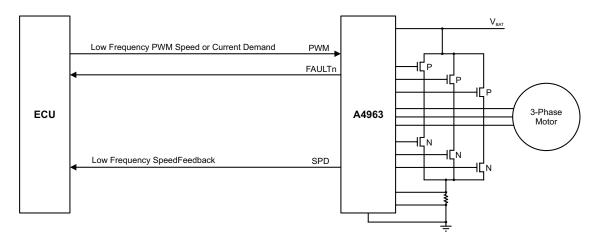

The A4963 can be used as a stand-alone controller communicating directly with an electronic control unit (ECU) or it can be used in a close-coupled system with a local microcontroller (MCU).

The motor is driven using block commutation (trapezoidal drive) where phase commutation is determined, without the need for independent position sensors, by monitoring the motor back-EMF (bemf). The sensorless startup scheme allows the A4963 to operate over a wide range of motor and load combinations.

Dedicated circuits allow the A4963 to operate over a wide range of motor speeds, from less than 100 rpm to in excess of 30,000 rpm, depending on the supply voltage and motor capability.

Several operational modes are available including duty-cycle (voltage) control, current (torque limit) control, and closed-loop speed control. Operating mode and control parameters can be altered through an SPI-compatible serial interface.

Motor operation is controlled by a programmable PWM input that can be used to define the motor operating state and provide the proportional input for the selected operating mode.

Integrated diagnostics provide indication of undervoltage, overtemperature, and power bridge faults and can protect the power switches under most short-circuit conditions. Faults are indicated by a single open-drain output than can be used to pull the PWM input low.

The A4963 is provided in a small, thermally enhanced 20-pin TSSOP with exposed thermal pad.

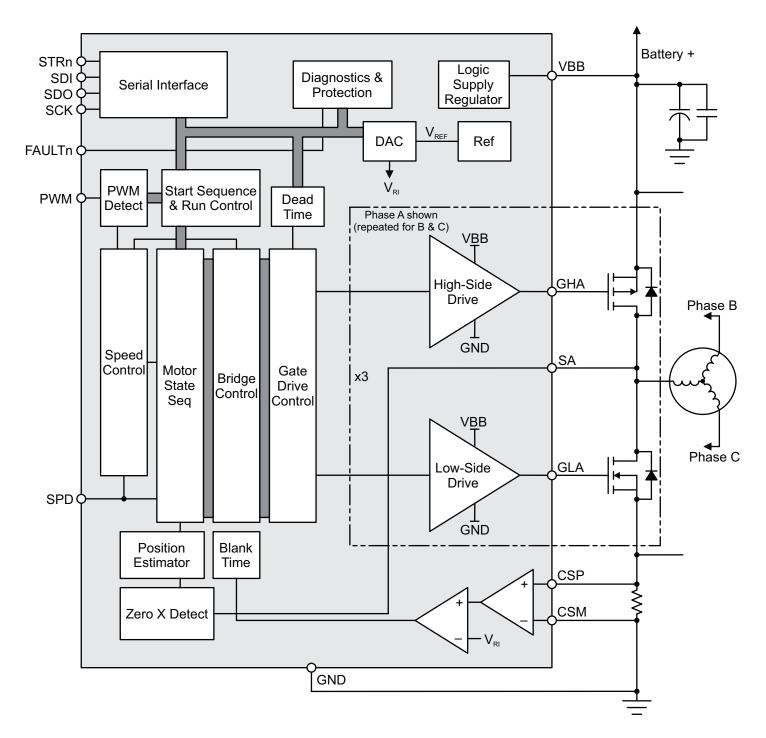

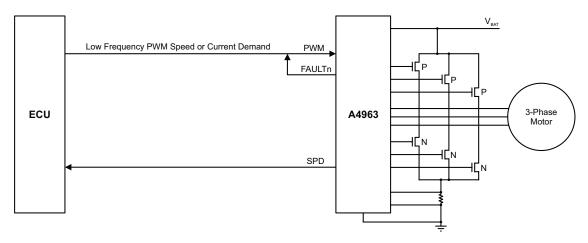

Typical Application - Functional Block Diagrams

# **Sensorless BLDC Controller**

#### **SELECTION GUIDE**

| Part Number Packing |                      | Package                                                                      |  |  |  |

|---------------------|----------------------|------------------------------------------------------------------------------|--|--|--|

| A4963GLPTR-T        | 4000 pieces per reel | 6.5 mm × 4.4 mm, 1.2 mm nominal height 20-pin TSSOP with exposed thermal pad |  |  |  |

#### **Table of Contents**

| Features and Benefits                  | 1  |

|----------------------------------------|----|

| Description                            | 1  |

| Applications                           | 1  |

| Package                                | 1  |

| Typical Application Diagrams           | 1  |

| Selection Guide                        | 2  |

| Absolute Maximum Ratings               | 3  |

| Thermal Characteristics                | 3  |

| Pinout Diagram and Terminal List Table | 4  |

| Functional Block Diagram               | 5  |

| Electrical Characteristics             | 6  |

| Timing Diagrams                        | 9  |

| Closed-Loop Control Diagrams           | 11 |

| Functional Description                 | 12 |

| Input and Output Terminal Functions    | 12 |

| Motor Drive System                     | 13 |

| Motor Control                          | 16 |

| Power Supplies                         | 21 |

| Gate Drive and Bridge PWM              | 21 |

| Current Limit                          | 24 |

| Diagnostics                         | 27 |

|-------------------------------------|----|

| FAULTn Output                       | 27 |

| Serial Diagnostic Output            | 27 |

| Fault Action                        | 27 |

| Fault Masks                         | 29 |

| Chip-Level Diagnostics              | 29 |

| Loss of Synchronization             | 30 |

| Serial Interface                    | 32 |

| Serial Registers Definition         | 32 |

| Configuration and Control Registers | 33 |

| Diagnostic Register                 | 34 |

| Serial Register Reference           | 35 |

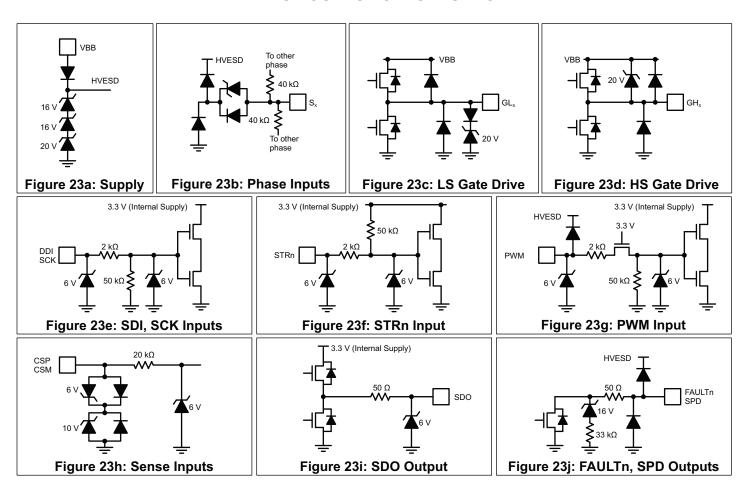

| Input/Output Structures             | 40 |

| Package Outline Drawing             | 41 |

# **Sensorless BLDC Controller**

#### **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Characteristic                          | Symbol              | Notes          | Rating                                           | Unit |

|-----------------------------------------|---------------------|----------------|--------------------------------------------------|------|

| Supply Voltage                          | $V_{BB}$            |                | -0.3 to 50                                       | V    |

| Battery-Compliant Inputs                |                     | PWM            | -0.3 to 50                                       | V    |

| Battery-Compliant Outputs               |                     | FAULTn, SPD    | -0.3 to 50                                       | V    |

| Logic Inputs                            |                     | STRn, SCK, SDI | -0.3 to 6.5                                      | V    |

| Logic Outputs                           |                     | SDO            | -0.3 to 6.5                                      | V    |

| Pins GHA, GHB, GHC                      |                     |                | V <sub>BB</sub> – 18 to<br>V <sub>BB</sub> + 0.3 | V    |

| Pins SA, SB, SC                         |                     |                | -4 to 51                                         | V    |

| Pins GLA, GLB, GLC                      |                     |                | -0.3 to 18                                       | V    |

| Sense Amplifier Inputs                  | V <sub>CSI</sub>    | CSP, CSM       | -4 to 6.5                                        | V    |

| Ambient Operating Temperature Range     | T <sub>A</sub>      |                | –25 to 150                                       | °C   |

| Maximum Continuous Junction Temperature | T <sub>J(max)</sub> |                | 165                                              | °C   |

| Storage Temperature Range               | T <sub>stg</sub>    |                | -55 to 150                                       | °C   |

<sup>\*</sup>With respect to GND

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol           | Test Conditions*                         | Value | Unit |

|----------------------------|------------------|------------------------------------------|-------|------|

| Package Thermal Resistance | R <sub>eJA</sub> | 4-layer PCB based on JEDEC standard      | 23*   | °C/W |

|                            |                  | 2-layer PCB with 3 in.2 copper each side | 44*   | °C/W |

|                            | R <sub>θJT</sub> |                                          | 2*    | °C/W |

$<sup>{}^*\!</sup>A \text{d} \text{d} \text{itional thermal information available on the Allegro website}.$

# **Sensorless BLDC Controller**

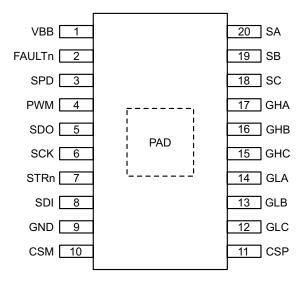

#### PINOUT DIAGRAM AND TERMINAL LIST TABLE

Package LP, 20-Pin eTSSOP with Exposed Thermal Pad

#### **Terminal List**

| Name   | Number | Function                        |  |

|--------|--------|---------------------------------|--|

| CSM    | 10     | Sense amp. negative input       |  |

| CSP    | 11     | Sense amp. positive input       |  |

| FAULTn | 2      | Fault output open drain         |  |

| GHA    | 17     | Phase A HS FET gate drive       |  |

| GHB    | 16     | Phase B HS FET gate drive       |  |

| GHC    | 15     | Phase C HS FET gate drive       |  |

| GLA    | 14     | Phase A LS FET gate drive       |  |

| GLB    | 13     | Phase B LS FET gate drive       |  |

| GLA    | 12     | Phase C LS FET gate drive       |  |

| GND    | 9      | Ground                          |  |

| PWM    | 4      | PWM input, pulled low for fault |  |

| Name | Number | Function                          |

|------|--------|-----------------------------------|

| SA   | 20     | Phase A motor phase               |

| SB   | 19     | Phase B motor phase               |

| SC   | 18     | Phase C motor phase               |

| SCK  | 6      | Serial clock                      |

| SDI  | 8      | Serial data input                 |

| SDO  | 5      | Serial data output                |

| SPD  | 3      | Speed output                      |

| STRn | 7      | Serial strobe (chip select) input |

| VBB  | 1      | Main supply                       |

| Pad  | _      | Connect to ground                 |

# **Sensorless BLDC Controller**

**Functional Block Diagram**

# **Sensorless BLDC Controller**

### ELECTRICAL CHARACTERISTICS: Valid at $T_A$ = 25°C, $V_{BB}$ = 4.2 to 28 V, unless noted otherwise

| Characteristics                                      | Symbol               | Test Conditions                                                                           | Min.                   | Тур. | Max.                   | Unit |

|------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------|------------------------|------|------------------------|------|

| SUPPLY AND REFERENCE                                 | ·                    | ,                                                                                         |                        |      |                        |      |

|                                                      |                      | Operating; outputs active                                                                 | 4.2                    | _    | 50                     | V    |

| VBB Functional Operating Range <sup>[1]</sup>        | V <sub>BB</sub>      | Operating; outputs disabled                                                               | 4.0                    | _    | 50                     | V    |

|                                                      |                      | No unsafe states                                                                          | 0                      | _    | 50                     | V    |

| VBB Quiescent Current                                | I <sub>BBQ</sub>     | PWM = inactive, V <sub>BB</sub> = 12 V                                                    | _                      | 12   | 18                     | mA   |

| System Clock Period                                  | tosc                 |                                                                                           | 47.5                   | 50   | 52.5                   | ns   |

| GATE OUTPUT DRIVE                                    | '                    |                                                                                           |                        |      |                        |      |

| Turn-On Time                                         | t <sub>r</sub>       | C <sub>LOAD</sub> = 500 pF, 20% to 80%, V <sub>BB</sub> = 12 V                            | _                      | 200  | _                      | ns   |

| Turn-Off Time                                        | t <sub>f</sub>       | C <sub>LOAD</sub> = 500 pF, 20% to 80%, V <sub>BB</sub> = 12 V                            | _                      | 200  | _                      | ns   |

|                                                      |                      | $T_J = 25^{\circ}\text{C}, I_{GHx} = -40 \text{ mA}^{[2]}$                                | 12                     | 17   | 26                     | Ω    |

| GHx Pull-Up On Resistance                            | R <sub>GHUP</sub>    | T <sub>J</sub> = 150°C, I <sub>GHx</sub> = -40 mA <sup>[2]</sup>                          | _                      | 26   | _                      | Ω    |

| GHx Pull-Up Current Limit                            | I <sub>GHLIMUP</sub> |                                                                                           | _                      | 300  | -                      | mA   |

|                                                      |                      | T <sub>J</sub> = 25°C, I <sub>GHx</sub> = 40 mA, V <sub>BB</sub> = 10 V                   | 23                     | 28   | 33                     | Ω    |

| GHx Pull-Down On Resistance                          | R <sub>GHDN</sub>    | T <sub>J</sub> = 150°C, I <sub>GHx</sub> = 40 mA, V <sub>BB</sub> = 10 V                  | _                      | 40   | _                      | Ω    |

| GHx Pull-Down Current Limit                          | I <sub>GHLIMDN</sub> |                                                                                           | _                      | 100  | _                      | mA   |

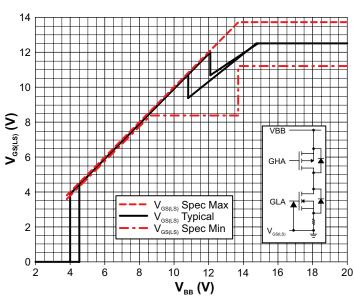

| GHx Output Voltage High (Off)                        | V <sub>GHH</sub>     | -10 μA < I <sub>GH</sub> < 10 μA                                                          | V <sub>BB</sub> - 0.2  | _    | _                      | V    |

| GHx Output Voltage Low (Active)                      | V <sub>GHL</sub>     | I <sub>GH</sub> = 10 mA, V <sub>BB</sub> = 14.5 V                                         | 0.9                    | _    | 2.6                    | V    |

|                                                      |                      | -10 μA < I <sub>GH</sub> < 10 μA, V <sub>BB</sub> ≥ 14.1 V                                | V <sub>BB</sub> – 14.1 | _    | V <sub>BB</sub> – 11.3 | V    |

|                                                      |                      | $-10 \mu A < I_{GH} < 10 \mu A$ , $9.6 \le V_{BB} < 14.1 V$                               | 0                      | _    | V <sub>BB</sub> - 9.4  | V    |

|                                                      |                      | -10 μA < I <sub>GH</sub> < 10 μA, V <sub>BB</sub> < 9.6 V                                 | 0                      | _    | 0.2                    | V    |

| 0                                                    | _                    | T <sub>J</sub> = 25°C, I <sub>GLx</sub> = -40 mA <sup>[2]</sup> , V <sub>BB</sub> = 10 V  | 17                     | 24   | 31                     | Ω    |

| GLx Pull-Up On Resistance                            | R <sub>GLUP</sub>    | T <sub>J</sub> = 150°C, I <sub>GLx</sub> = -40 mA <sup>[2]</sup> , V <sub>BB</sub> = 10 V | _                      | 38   | _                      | Ω    |

| GLx Pull-Up Current Limit                            | I <sub>GLLIMUP</sub> |                                                                                           | _                      | 140  | _                      | mA   |

| 0. 5.15 0. 5.11                                      |                      | T <sub>J</sub> = 25°C, I <sub>GLx</sub> = 40 mA                                           | 15                     | 20   | 25                     | Ω    |

| GLx Pull-Down On Resistance                          | R <sub>GLDN</sub>    | T <sub>J</sub> = 150°C, I <sub>GLx</sub> = 40 mA                                          | 30                     | 40   | 50                     | Ω    |

| GLx Pull-Down Current Limit                          | I <sub>GLLIMDN</sub> |                                                                                           | _                      | 160  | _                      | mA   |

|                                                      |                      | -10 μA < I <sub>GL</sub> < 10 μA, V <sub>BB</sub> < 8.6 V                                 | V <sub>BB</sub> - 0.2  | _    | V <sub>BB</sub>        | V    |

|                                                      |                      | -10 μA < I <sub>GL</sub> < 10 μA, 8.6 ≤ V <sub>BB</sub> < 13.7 V                          | 8.4                    | _    | V <sub>BB</sub>        | V    |

| GLx Output Voltage High (Active)                     | $V_{GLH}$            | -10 μA < I <sub>GL</sub> < 10 μA, V <sub>BB</sub> ≥ 13.7 V                                | 11.2                   | _    | 13.7                   | V    |

|                                                      |                      | I <sub>GL</sub> = -10 mA, V <sub>BB</sub> = 14.5 V                                        | 10.7                   | _    | 13.5                   | V    |

| GLx Output Voltage Low (Off)                         | V <sub>GLL</sub>     | -10 μA < I <sub>GL</sub> < 10 μA                                                          | _                      | _    | 0.2                    | V    |

| GHx Passive Pull-Down                                | R <sub>GHPD</sub>    | V <sub>BB</sub> = 0 V, V <sub>GH</sub> > -0.1 V                                           | _                      | 500  | _                      | kΩ   |

| GLx Passive Pull-Down                                | R <sub>GLPD</sub>    | V <sub>BB</sub> = 0 V, V <sub>GL</sub> < 0.1 V                                            | _                      | 500  | _                      | kΩ   |

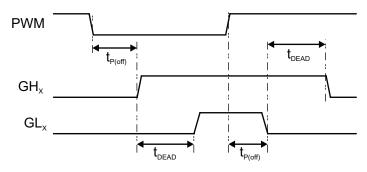

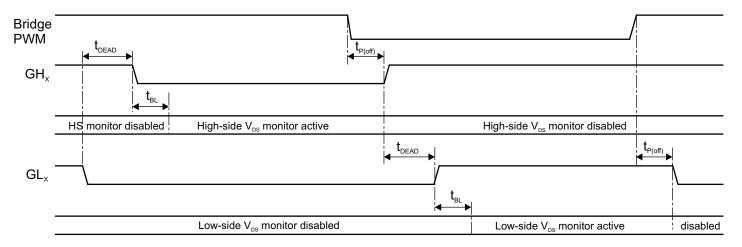

| Turn-Off Propagation Delay <sup>[3]</sup>            | t <sub>P(off)</sub>  | Input Change to unloaded Gate output change; Direct mode                                  | 200                    | 250  | 400                    | ns   |

| Turn-On Propagation Delay <sup>[3]</sup>             | t <sub>P(on)</sub>   | Input Change to unloaded Gate output change;<br>Direct mode                               | 200                    | 250  | 400                    | ns   |

| Dead Time (Turn-Off to Turn-On Delay) <sup>[3]</sup> | t <sub>DEAD</sub>    | Default power-up value                                                                    | 0.9                    | 1.0  | 1.1                    | μs   |

Continued on next page...

# **Sensorless BLDC Controller**

ELECTRICAL CHARACTERISTICS (continued): Valid at  $T_A$  = 25°C,  $V_{BB}$  = 4.2 to 28 V, unless noted otherwise

| Characteristics                             | Symbol            | Test Conditions                               | Min. | Тур. | Max. | Unit |

|---------------------------------------------|-------------------|-----------------------------------------------|------|------|------|------|

| LOGIC INPUTS AND OUTPUTS                    | ,                 |                                               | \\   |      |      | ,    |

| Input Low Voltage                           | V <sub>IL</sub>   |                                               | _    | _    | 0.8  | V    |

| Input High Voltage                          | V <sub>IH</sub>   |                                               | 2.0  | _    | _    | V    |

| Input Hysteresis                            | V <sub>Ihys</sub> |                                               | 150  | 550  | _    | mV   |

| Input Pull-Down Resistor (PWM, SDI, SCK)    | R <sub>PD</sub>   |                                               | 30   | 50   | 70   | kΩ   |

| Input Pull-Up Resistor (STRn)               | R <sub>PU</sub>   |                                               | 30   | 50   | 70   | kΩ   |

| Output Low Voltage (SDO)                    | V <sub>OL</sub>   | I <sub>OL</sub> = 1 mA                        | _    | 0.2  | 0.4  | V    |

| Output High Voltage (SDO)                   | V <sub>OH</sub>   | I <sub>OL</sub> = 1 mA <sup>[2]</sup>         | 2.4  | 3.0  | _    | V    |

| Output Leakage <sup>[2]</sup> (SDO)         | Io                | 0 V < V <sub>O</sub> < 3.3 V, STRn = 1        | -1   | _    | 1    | μΑ   |

| Output Low Voltage (FAULTn, SPD)            | V <sub>OL</sub>   | I <sub>OL</sub> = 4 mA, FAULTn active         | _    | 0.2  | 0.4  | V    |

| Outrout Commont Limit (FALILTS CDD)         |                   | 0 V < V <sub>O</sub> < 15 V, FAULTn active    | _    | 10   | 15   | mA   |

| Output Current Limit (FAULTn, SPD)          | I <sub>OLIM</sub> | 15 V ≤ V <sub>O</sub> < 50 V, FAULTn active   | _    | _    | 2    | mA   |

| Output Lands (2) (FALILE, OPP)              |                   | 0 V < V <sub>O</sub> < 12 V, FAULTn inactive  | -1   | _    | 1    | μΑ   |

| Output Leakage <sup>[2]</sup> (FAULTn, SPD) | Io                | 12 V ≤ V <sub>O</sub> < 50 V, FAULTn inactive | _    | _    | 1.7  | mA   |

| LOGIC I/O - TIMING PARAMETERS               |                   |                                               | ·    |      |      |      |

| PWM Duty Detect Frequency Range             | f <sub>PWD</sub>  |                                               | 5    | _    | 1000 | Hz   |

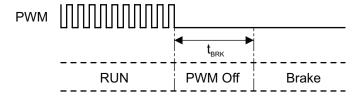

| PWM Brake Time                              | t <sub>BRK</sub>  |                                               | 500  | _    | _    | μs   |

| SERIAL INTERFACE – TIMING PAR               | AMETERS           |                                               | ·    | •    |      |      |

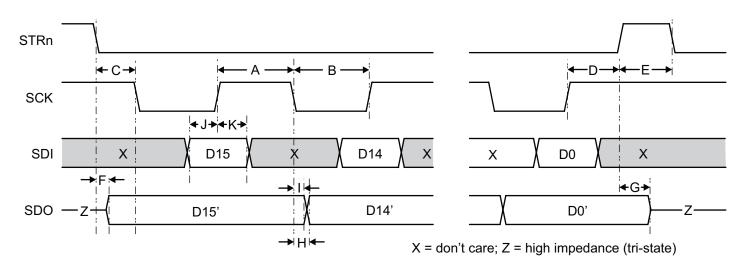

| Clock High Time                             | t <sub>SCKH</sub> | A in Figure 1                                 | 50   | _    | _    | ns   |

| Clock Low Time                              | t <sub>SCKL</sub> | B in Figure 1                                 | 50   | _    | _    | ns   |

| Strobe Lead Time                            | t <sub>STLD</sub> | C in Figure 1                                 | 30   | -    | _    | ns   |

| Strobe Lag Time                             | t <sub>STLG</sub> | D in Figure 1                                 | 30   | -    | _    | ns   |

| Strobe High Time                            | t <sub>STRH</sub> | E in Figure 1                                 | 300  | _    | _    | ns   |

| Data Out Enable Time                        | t <sub>SDOE</sub> | F in Figure 1                                 | _    | _    | 40   | ns   |

| Data Out Disable Time                       | t <sub>SDOD</sub> | G in Figure 1                                 | _    | _    | 30   | ns   |

| Data Out Valid Time from Clock Falling      | t <sub>SDOV</sub> | H in Figure 1                                 | -    | _    | 40   | ns   |

| Data Out Hold Time from Clock<br>Falling    | t <sub>SDOH</sub> | I in Figure 1                                 | 5    | _    | _    | ns   |

| Data In Setup Time to Clock Rising          | t <sub>SDIS</sub> | J in Figure 1                                 | 15   | _    | _    | ns   |

| Data In Hold Time from Clock Rising         | t <sub>SDIH</sub> | K in Figure 1                                 | 10   | _    | _    | ns   |

| MOTOR STARTUP PARAMETERS                    |                   |                                               | ·    |      |      |      |

| Hold Duty Cycle                             | D <sub>H</sub>    | Default power-up value                        | 35.5 | 37.5 | 39.5 | %    |

| Hold Time                                   | t <sub>HOLD</sub> | Default power-up value                        | 15.2 | 16   | 16.8 | ms   |

| Start Speed                                 | f <sub>ST</sub>   | Default power-up value                        | 7.6  | 8    | 8.4  | Hz   |

| Start Duty Cycle                            | D <sub>ST</sub>   | Default power-up value                        | 47.5 | 50   | 52.5 | %    |

Continued on next page...

# **Sensorless BLDC Controller**

#### ELECTRICAL CHARACTERISTICS (continued): Valid at T<sub>A</sub>= 25°C, V<sub>BB</sub> = 4.2 to 28 V, unless noted otherwise

| Characteristics                                      | Symbol              | Test Conditions                                 | Min.   | Тур.   | Max.   | Unit |

|------------------------------------------------------|---------------------|-------------------------------------------------|--------|--------|--------|------|

| MOTOR RUN PARAMETERS                                 |                     |                                                 |        |        |        |      |

| Phase Advance (in Electrical Degrees)                | $\theta_{ADV}$      | Default power-up value                          | 14     | 15     | 16     | 0    |

| Position Control Proportional Gain                   | K <sub>CP</sub>     | Default power-up value                          | _      | 1      | _      | _    |

| Position Control Integral Gain                       | K <sub>Cl</sub>     | Default power-up value                          | _      | 1      | _      | _    |

| Speed Control Proportional Gain                      | K <sub>SP</sub>     | Default power-up value                          | _      | 1      | _      | _    |

| Speed Control Integral Gain                          | K <sub>SI</sub>     | Default power-up value                          | _      | 1      | _      | _    |

| Maximum Control Speed                                | f <sub>MX</sub>     | Default power-up value                          | 3112.9 | 3276.7 | 3440.5 | Hz   |

| Speed Error                                          | Ef <sub>CCMX</sub>  |                                                 | -5     | _      | 5      | %    |

| CURRENT LIMITING                                     |                     |                                                 | '      |        |        |      |

| Current Limit Threshold Voltage<br>Range             | V <sub>ILIM</sub>   | $V_{ILIM} = V_{CSP} - V_{CSM}$                  | 12.5   | _      | 200    | mV   |

| Current Limit Threshold Voltage                      | V <sub>ILIM</sub>   | Default power-up value                          | _      | 200    | _      | mV   |

| Current Limit Threshold Voltage Error <sup>[7]</sup> | E <sub>ILIM</sub>   | V <sub>ILIM</sub> = 200 mV                      | -5%    | _      | 5%     | %FS  |

| Fixed Off-Time                                       | t <sub>PW</sub>     | Default power-up value                          | 47.9   | 50.4   | 52.9   | μs   |

| Blank Time                                           | t <sub>BL</sub>     | Default power-up value                          | 3.04   | 3.2    | 3.36   | μs   |

| PROTECTION                                           |                     |                                                 | '      |        |        |      |

| VBB Undervoltage Lockout                             | V <sub>BBON</sub>   | V <sub>BB</sub> rising                          | 4.2    | 4.4    | 4.6    | V    |

| VBB Officer voltage Lockout                          | V <sub>BBOFF</sub>  | V <sub>BB</sub> falling                         | 3.8    | 4.0    | 4.2    | V    |

| VBB POR Voltage                                      | $V_{BBR}$           | V <sub>BB</sub> falling                         | _      | 3.2    | 3.5    | V    |

| VBB POR Voltage Hysteresis                           | $V_{\rm BBRHys}$    |                                                 | _      | 100    | _      | mV   |

| VDS Threshold                                        | V <sub>DST</sub>    | Default power-up value                          | 1325   | 1550   | 1705   | mV   |

| VDS Throshold May High Side                          | \/                  | V <sub>BB</sub> ≥ 6 V                           | _      | _      | 1705   | mV   |

| VDS Threshold Max, High Side                         | V <sub>DST</sub>    | 5 V ≤ V <sub>BB</sub> < 6 V                     | _      | _      | 500    | mV   |

| VDS Threshold Max, Low Side                          | V <sub>DST</sub>    | V <sub>BB</sub> ≥ 4.2 V                         | _      | _      | 1705   | mV   |

| VDS Threshold Offset <sup>[4][5]</sup>               |                     | V <sub>DST</sub> ≥ 1 V                          | _      | ±100   | -      | mV   |

| VDS Threshold Offset (1916)                          | V <sub>DSTO</sub>   | V <sub>DST</sub> ≤ 1 V                          | -150   | ±50    | 150    | mV   |

| Temperature Warning Threshold                        | T <sub>JWH</sub>    | Temperature increasing                          | 125    | 135    | 145    | °C   |

| Temperature Warning Hysteresis                       | T <sub>JWHhys</sub> |                                                 |        | 15     | _      | °C   |

| Overtemperature Threshold                            | T <sub>JF</sub>     | Temperature increasing                          | 170    | 175    | 180    | °C   |

| Overtemperature Hysteresis                           | T <sub>JHyst</sub>  | Recovery = T <sub>JF</sub> - T <sub>JHyst</sub> | _      | 15     | _      | °C   |

<sup>[1]</sup> Function is correct but parameters are not guaranteed above or below the general limits (6-28 V). [2] For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device terminal.

<sup>[3]</sup> See Figure 2 for gate drive output timing.

<sup>[4]</sup> As V<sub>SX</sub> decreases, high-side fault occurs if (V<sub>BAT</sub> - V<sub>SX</sub>) > (V<sub>DST</sub> + V<sub>DSTO</sub>).

[5] As V<sub>SX</sub> increases, low-side fault occurs if (V<sub>SX</sub>) > (V<sub>DST</sub> + V<sub>DSTO</sub>).

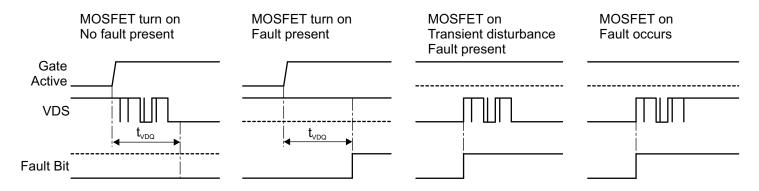

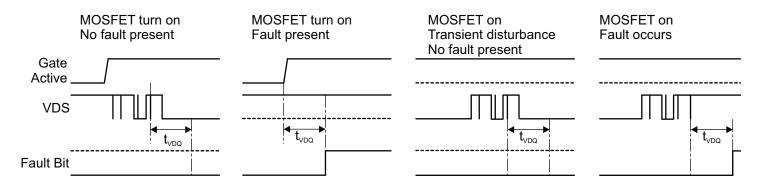

[6] See Figures 4 and 5 for V<sub>DS</sub> monitor timing.

[7] Current limit threshold voltage error is the difference between the target threshold voltage and the actual threshold voltage, referred to maximum full-scale (100%) current:  $E_{ILIM} = 100 \times (V_{ILIMActual} - V_{ILIM})/200\% (V_{ILIM} in mV)$ .

# **Sensorless BLDC Controller**

Figure 1: Serial Interface Timing

Figure 2: Gate Drive Timing

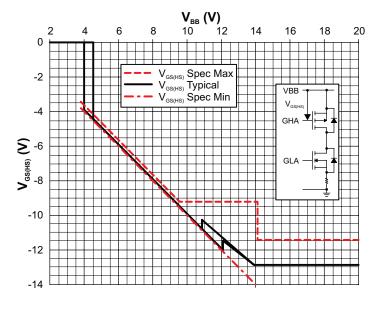

Figure 3: Typical Low-Side Gate Drive vs. V<sub>BB</sub>

Figure 4: Typical High-Side Gate Drive vs. V<sub>BB</sub>

# **Sensorless BLDC Controller**

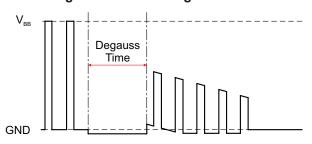

### **VDS Fault Monitor Timing Diagrams**

Figure 5: VDS Fault Monitor – Blank Mode Timing (VDQ = 1)

Figure 6: VDS Fault Monitor – Blank Mode Timing (VDQ = 1)

Figure 7: VDS Fault Monitor – Debounce Mode Timing (VDQ = 0)

# **Sensorless BLDC Controller**

#### **Closed-Loop Control Diagrams**

Figure 8: Local Closed-Loop Control with High Level ECU Communications

Figure 9: Remote Closed-Loop Control

Figure 10: Remote Single-Wire Command with Integrated Closed-Loop Control

### **Sensorless BLDC Controller**

#### **FUNCTIONAL DESCRIPTION**

The A4963 is a three-phase, sensorless, brushless DC (BLDC) motor controller for use with external complementary P-channel and N-channel power MOSFETs. The motor is driven using block commutation (trapezoidal drive), where phase commutation is determined by a proprietary, motor back-emf (bemf) sensing technique. The motor bemf is sensed to determine the rotor position without the need for independent position sensors. An integrated sensorless startup scheme allows a wide range of motor and load combinations.

Motor current is provided by six external power MOSFETs arranged as a three-phase bridge with three N-channel low-side MOSFETs and three P-channel high-side MOSFETS. The A4963 provides six high current gate drives, three high-side and three low-side, capable of driving a wide range of MOSFETs. The maximum MOSFET drive voltage is internally limited under all supply conditions to protect the MOSFET from excessive gate-source voltage without the need for an external clamp circuit. The minimum MOSFET drive voltage is determined by the supply voltage allowing operation at very low voltage by using logic-level MOSFETs.

Three basic operational modes are available: open-loop speed (voltage) control, closed-loop torque (current) control, and closed-loop speed control. Operating mode and control parameters can be altered through an SPI-compatible serial interface.

Motor operation is controlled by a single, low-frequency PWM input that determines the motor operating state and provides proportional input for the selected operating mode.

Startup (inrush) current and peak motor current are limited by an integrated fixed off-time PWM current limiter. The maximum current limit is set by a single external sense resistor, and the active current limit can be modified through the serial interface.

Integrated diagnostics provide indication of undervoltage, overtemperature, and power bridge faults and can be configured to protect the power FETs under most short-circuit conditions. A single FAULT flag is provided, and detailed diagnostics are available through the serial interface.

Specific functions are described more fully in following sections.

#### **Input and Output Terminal Functions**

**VBB:** Main power supply for internal regulators and charge pump. The main power supply should be connected to VBB through a reverse voltage protection circuit and should be decoupled with ceramic capacitors connected close to the supply and ground terminals.

**GND:** Analog reference, Digital and power ground. Connect to supply ground—see layout recommendations.

**GHA**, **GHB**, **GHC**: High-side, gate drive outputs for external P-channel MOSFETs.

**SA, SB, SC:** Motor phase connections. These terminals sense the voltages switched across the load.

**GLA**, **GLB**, **GLC**: Low-side, gate drive outputs for external N-channel MOSFETs.

**CSP**, **CSM**: Differential current sense amplifier inputs. Connect directly to each end of the sense resistor using separate PCB traces.

**PWM:** Programmable PWM input to control the motor operating mode and the proportional duty cycle input for the selected control mode. Can be shorted to ground or VBB without damage.

**SPD:** Open-drain speed output indicator. Output frequency is programmable. It can be the commutation frequency (TACHO) or the electrical cycle frequency (FG). Can be shorted to ground or VBB without damage.

**FAULTn:** Open-drain active-low fault indicator. Can be connected to PWM input to provide single wire interface to a controlling ECU. Can be shorted to ground or VBB without damage.

**SDI:** Serial data input. 16-bit serial word input msb first.

**SDO:** Serial data output. High impedance when STRn is high. Outputs bit 15 of the diagnostic register, the fault flag, as soon as STRn goes low.

**SCK:** Serial clock. Data is latched in from SDI on the rising edge of CLK. There must be 16-rising edges per write and SCK must be held high when STRn changes.

**STRn:** Serial data strobe and serial access enable. When STRn is high, any activity on SCK or SDI is ignored and SDO is high impedance, allowing multiple SDI slaves to have common SDI, SCK, and SDO connections.

### **Sensorless BLDC Controller**

#### **Motor Drive System**

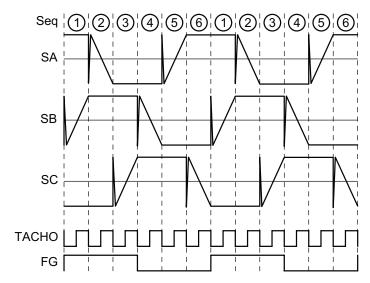

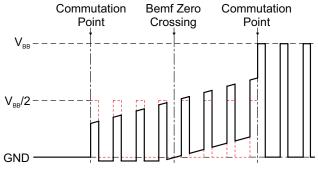

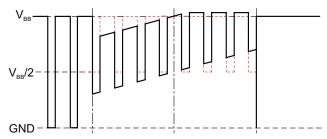

The motor drive system consists of three half-bridge gate drive outputs, each driving one leg of an external 3-phase MOSFET power bridge. The state of the gate drive outputs is determined by a state sequencer with six possible states. These states are shown in Table 1 and change in a set sequence. The effect of these states on the motor phase voltage is illustrated in Figure 11. This sequence creates a moving magnetic field in the poles of the stator, against which the permanent magnets in the rotor can react to produce torque at the motor output shaft.

The point at which the state of the gate outputs change is defined as the commutation point and must occur each time the magnetic poles of the rotor reach a specific point in relation to the poles of the stator. This point is determined by a closed-loop commutation controller consisting of a position estimator and commutation timer. This controller uses the output of a complete self-contained bemf sensing scheme to determine the actual position of the motor and adjust the estimated position and commutation frequency to synchronize with the rotor poles in the motor.

The motor speed can be determined by monitoring the SPD output. There are two options for the signal available at the SPD terminal selected via the serial interface. The default is a signal, defined as FG, at the frequency of the complete electrical cycle (the 6-state sequence in Table 1). FG goes high on entering state 1 and goes low on entering state 4. The alternative is a square wave signal, defined as TACHO, at the commutation frequency with the falling edge synchronized to the commutation point. FG and TACHO are shown in Figure 11.

Figure 11: Motor Phase State Sequence

In the A4963, motor speed is always defined as the frequency of the electrical cycle,  $f_S$ . This is the same frequency as the FG signal, if selected, on the SPD output.

The actual mechanical speed of the motor,  $\omega$ , will depend on the number of pole pairs,  $N_{PP}$ , and is determined by:

$$\omega = \frac{60 \times f_s}{N_{PP}}$$

where  $f_S$  is in Hz and  $\omega$  is in rpm (mechanical revolutions per minute).

**Table 1: Control and Phase Sequence**

|     | Contr | ol Bits |      | State | M  | lotor Phas | se |     |     | Gate Driv | e Outputs | ;   |     | Mode  |

|-----|-------|---------|------|-------|----|------------|----|-----|-----|-----------|-----------|-----|-----|-------|

| RUN | BRK   | DIR=1   | DIR0 | State | SA | SB         | sc | GHA | GLA | GHB       | GLB       | GHC | GLC | Wode  |

| 1   | 0     |         |      | 1     | HI | Z          | LO | ON  | OFF | OFF       | OFF       | OFF | ON  |       |

| 1   | 0     | ]       |      | 2     | Z  | HI         | LO | OFF | OFF | ON        | OFF       | OFF | ON  |       |

| 1   | 0     |         |      | 3     | LO | HI         | Z  | OFF | ON  | ON        | OFF       | OFF | OFF | Dun   |

| 1   | 0     |         |      | 4     | LO | Z          | HI | OFF | ON  | OFF       | OFF       | ON  | OFF | Run   |

| 1   | 0     |         |      | 5     | Z  | LO         | HI | OFF | OFF | OFF       | ON        | ON  | OFF |       |

| 1   | 0     | ] [     | V    | 6     | HI | LO         | Z  | ON  | OFF | OFF       | ON        | OFF | OFF |       |

| 0   | х     | х       | х    | х     | Z  | Z          | Z  | OFF | OFF | OFF       | OFF       | OFF | OFF | Coast |

| 1   | 1     | х       | х    | х     | LO | LO         | LO | OFF | ON  | OFF       | ON        | OFF | ON  | Brake |

$x \equiv don't care$ , HI  $\equiv high$ -side FET active, LO  $\equiv low$ -side FET active, Z  $\equiv high$  impedance, both FETs off

ON ≡ high-side output (GHx) low, low-side output (GLx) high

OFF  $\equiv$  high-side output (GHx) high, low-side output (GLx) low

### **Sensorless BLDC Controller**

#### **Rotor Position Sensing Using Motor bemf**

A key element of the controller is the back-emf zero crossing detector. Determining the rotor position using direct bemf sensing relies on the accurate comparison of the voltage on the undriven (tri-state) motor phase (indicated by Z in Table 1) to the voltage at the center tap of the motor, approximated using an internally generated reference voltage. The bemf zero crossing—the point where the voltage of the undriven motor winding crosses the reference voltage—occurs when a pole of the rotor is in alignment with a pole of the stator and is used as a positional reference for the commutation controller.

The internally generated zero crossing reference voltage follows the bridge drive voltage levels to allow bemf crossing detection during both PWM-on and PWM-off states. The comparator adds hysteresis to the reference voltage in order to reduce the effect of low-level noise on the comparison. The effects of large signal noise, such as switching transients, are removed by digital filtering.

When the motor is running at a constant speed, with no phase advance, this zero crossing should occur approximately halfway through one commutation period. The commutation controller compares the expected zero crossing point to the detected zero crossing point and adjusts the phase and frequency of the position estimator and commutation timer to minimize the difference between the expected and actual crossing points over a number of commutation periods.

The controller also allows the commutated magnetic field of the stator to be out of phase with the rotor. The expected zero crossing point is adjusted to be later in the commutation period, and the controller modifies the commutation timing to minimize the difference between the estimated and measured bemf zero-crossing points. This is known as phase advance, and the amount of phase advance in electrical degrees is set (up to 28°) by the contents of the PA[3:0] variable.

In any electric motor, a force is produced by the interaction of rotor magnetic poles and stator magnetic field. The motor and the commutation system are designed such that a portion of this force is tangential to the rotor and will produce a rotational torque. Applying phase advance will have the effect of changing the direction of force vector relative to the rotor and will increase the tangential component of the force. This will increase the effectiveness of the torque produced by the stator field and permit a higher motor speed than for no phase advance at the same input demand.

The controller uses proportional and integral feedback (PI control) to provide a fast response with good long-term accuracy. The amount of proportional and integral feedback can be adjusted independently by setting the CP[3:0] and CI[3:0] variables respectively, through the serial interface. This allows the dynamic response to be tuned to different system conditions if required; however, the default values for CP and CI will achieve optimum results in most applications.

The control method used is tolerant to missing bemf zero crossing detections and will simply change the speed of the applied commutation sequence by an amount determined by the proportional gain of the control loop. This results in a much more stable system that does not lose synchronization due to impulse perturbations in the motor load torque. It also means that real loss of synchronization cannot be determined by missing bemf zero crossing detection and has to be determined in a different way.

In the extreme case, when a motor stalls due to excessive load on the output, there will be no bemf zero crossing detection, and the frequency of the commutation sequence will be reduced each commutation point to try and regain synchronization. If the resulting speed reduces below the low speed threshold, then the controller will enter the loss of synchronization state and either stop or attempt to restart the motor. The low speed threshold will be 25% of the start speed set by the value of the SS[3:0] variable.

In some cases, rather than a complete stall, it is also possible for the motor to vibrate at a whole fraction (subharmonic) of the commutation frequency produced by the controller. In this case, the controller will still detect the bemf zero crossing, but at a rate much higher than the motor is capable of running. If the resulting speed increases above the overspeed threshold, then the controller will enter the loss of synchronization state and either stop or attempt to restart the motor. The overspeed threshold is determined by the product of the maximum limit ratio and the maximum speed. The maximum limit ratio is set by the value of the SH[1:0] variable, and the maximum speed is by set the value of the SMX[2:0] variable.

The maximum speed, defined by SMX, determines the motor speed for 100% input when operating in the closed-loop speed control mode. However, it must still be set to a suitable level to provide an appropriate overspeed threshold for all other operating modes.

### **Sensorless BLDC Controller**

#### Startup

To correctly detect the zero crossing, the changing motor bemf on any phase must be detectable when that phase is not being driven. When the motor is running at a relatively constant speed, this is ensured by the commutation scheme used. However, during startup, the motor must be accelerated from rest in such a way that the bemf zero crossing can be detected. Initially, as the motor is started, there is no rotor position information from the bemf sensor circuits, and the motor must be driven using forced commutation.

To ensure that the motor startup and sensorless bemf capture is consistent, the start sequencer always forces the motor to a known hold position and for a programmable hold time by driving phase C low and applying a programmable duty cycle PWM signal to phase A. The hold time is defined by the contents of the HT[3:0] variable and the hold duty cycle by the contents of the HD[3:0] variable.

Following the hold time, the motor phases are commutated to the next state to force the motor to start in the required direction, and the PWM duty cycle is changed to the startup duty cycle set by the contents of the SD[3:0] variable. For the forwards direction when DIR = 0, phase C will be held low, and the startup duty cycle is applied to phase B. For the reverse direction when DIR = 1, phase B will be held low, and the startup duty cycle is applied to phase A. The duration of the first commutation period is determined by the start speed set by the value of the SS[3:0] variable. This value is also used as the starting speed for the closed-loop commutation controller and for the speed controller if selected.

At the end of the second commutation period, control is passed to the closed-loop commutation controller, and the start sequencer is reset. The SPD terminal will immediately output FG or TACHO as selected by the SPO variable.

During the start sequence, it is possible for the motor to be rotating out of synchronization with the commutated field, as sequenced by the A4963. In some cases, it is possible for the motor bemf produce a voltage that reinforces, rather than opposes, the supply voltage. If this occurs, then the slow decay

mode used during running will not be able to maintain control of the motor current during the PWM off-time, and the current may rise uncontrollably. To overcome this effect, the A4963 uses a mixed decay mode PWM during startup to keep the current under control. Mixed decay is where the bridge is first switched into fast decay mode then into slow decay after a portion of the PWM period. This applies a reverse voltage to the motor phase winding and counteracts the effect of the out-of-phase bemf voltage.

The portion of the PWM period during which fast decay is used is called percent fast decay (PFD). Two values of PFD—12.5% or 25%—can be selected by the PFD variable in configuration register 1. Mixed decay is applied automatically for the first sixteen full electrical cycles (96 commutation periods).

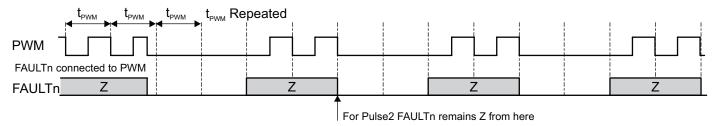

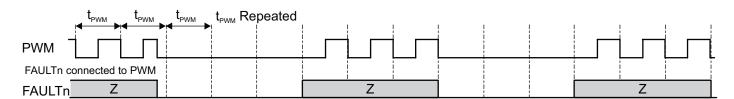

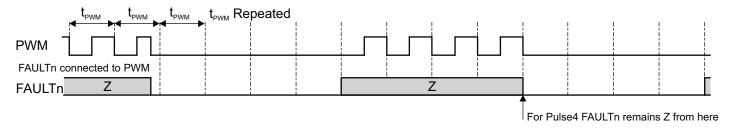

Following the start sequence, the commutation controller is expected to attain synchronization with the motor and stabilize at a running frequency to match the control input demand. If synchronization is not achieved, the commutation controller will either reduce the resulting motor frequency below the low-speed limit or increase it above the overspeed limit. If this happens, the A4963 will indicate a loss of synchronization condition by repeatedly pulling the FAULTn output active low for three PWM periods and inactive for three periods.

If a loss of synchronization occurs, the RUN and RSC bits are set to 1, and the PWM signal applied to the PWM input terminal is not 0% (or is not less than 25% for closed-loop speed control mode) then the FAULTn output will go active low for three PWM periods, inactive for three periods, then repeat this sequence before the start sequencer is reset and the start sequence initiated as shown in Figure 4. This cycle will continue until stopped by holding the PWM terminal in the inactive state or setting either RUN bit or the RSC bit to 0.

If a loss of synchronization occurs and RSC = 0, the FAULTn output will continue to indicate loss of synchronization until the PWM signal applied to the PWM input terminal is 0% (or <25% for closed-loop speed control mode) or the RUN bit is set to 0.

### **Sensorless BLDC Controller**

#### **Motor Control**

The running state, direction, and speed of the motor are controlled by a combination of commands through the serial interface and by the signal on the PWM terminal.

The serial interface provides three control bits: RUN, DIR, and BRK.

When RUN = 1, the A4963 is allowed to run the motor or to commence the startup sequence. When RUN = 0, all gate drive outputs go low, no commutation takes place, and the motor is allowed to coast. RUN = 0 overrides all other control inputs.

The DIR bit determines the direction of rotation. Forward is defined as DIR = 0, and the phase state sequence increments as defined in Table 1. Reverse is when DIR = 1, and the phase state sequence decrements. The BRK bit can be set to apply an electrodynamic brake which will decelerate a rotating motor. It will also provide some holding torque for a stationary motor. When RUN = 1, BRK = 1, and the PWM is inactive for longer than the PWM brake time, all low-side MOSFETs will be turned on, and all high-side MOSFETs turned off, effectively applying a short between the motor windings. This allows the reverse voltage generated by the rotation of the motor (motor bemf) to set up a current in the motor phase windings that will produce a braking torque. This braking torque will always oppose the direction of rotation of the motor. The strength of the braking or holding torque will depend on the motor parameters. No commutation takes place during braking, and no current control is available. Care must be taken to ensure that the braking current does not exceed the capability of the low-side MOSFETs.

There are three motor control methods included in the A4963. These are:

- open-loop speed (voltage) control

- closed-loop torque (current) control

- closed-loop speed control

In addition, the open-loop speed control can be regulated using direct or indirect PWM duty cycle control.

#### **PWM Control Input**

The PWM control input can be used to provide a proportional demand input to the A4963 for the selected control mode. It can be driven between ground and VBB and has hysteresis and a noise filter to improve noise performance.

The sense of the PWM input can be changed from active high to active low by changing the IPI variable in configuration regis-

ter 1. When IPI is 0, the default value, then the PWM input is active high. When IPI is 1, then the PWM input is inverted and active low. This applies to all operating modes and input modes.

In the direct open-loop speed control mode, when IPI is 0, the signal on the PWM terminal is applied directly to the power bridge. When IPI is 1 in direct mode, the the signal on the PWM terminal is inverted before being applied directly to the power bridge.

In indirect mode, a low-frequency signal between 5 Hz and 1 kHz is applied to the PWM terminal. The duty cycle of this signal is measured with an 8-bit counter system giving better than 0.5% resolution in duty cycle. When IPI is 0, the duty cycle is the ratio of the PWM high duration to the PWM period measured between falling edges of the PWM input signal. When IPI is 1, the duty cycle is the ratio of the PWM low duration to the PWM period measured between rising edges of the PWM input signal. The measured duty cycle is then used to set the bridge PWM duty cycle for the open-loop speed control mode or to provide the torque (current) reference or speed reference for the closed-loop control modes.

For systems where the operation of the A4963 is managed by a remote ECU using a single wire interface, it is also possible to connect the FAULTn terminal directly to the PWM terminal. This can be used to indicate to the ECU that a critical fault is present that has stopped the operation of the motor by the FAULTn output pulling the PWM input to ground continuously or with a variable-width pulse sequence.

#### **Direct Open-Loop Speed (Voltage) Control**

Direct access to the power bridge PWM control allows an external local microcontroller to provide application specific speed control and more advanced communications such as CAN bus or LIN bus. In this case, the microcontroller will be closely coupled to the A4963 and will vary the duty cycle of the PWM signal applied directly to the bridge in order to control the motor. The motor speed will be proportional to the duty cycle of this signal, but will also vary with the mechanical load and the supply voltage.

The A4963 will only provide current limiting using the internal closed-loop current regulator. The motor speed can be determined by monitoring the SPD output terminal. This output can be configured to provide a square wave at the commutation frequency or at the electrical cycle frequency.

The signal input to the PWM terminal must be at the required

### Sensorless BLDC Controller

PWM frequency for the motor and operating parameters. Typically, this will be between 10 and 20 kHz for most motors. For some very high-speed motors, this may have to be increased significantly.

When the PWM input is in the inactive state (low when IPI = 0, high when IPI = 1), the three-phase bridge is switched to one of three current decay recirculation modes depending on the value of the RM[2:0] variable. Slow decay synchronous recirculation can be high-side, low-side, or auto, which is a combination of the two controlled by the commutation state. The bridge can also be driven in fast decay mode without synchronous rectification. These modes are described further in the Gate Drive and Bridge PWM section below. During startup, mixed decay is always used as described in the Startup section above.

To avoid undesirable interaction between the external PWM signal applied to the PWM terminal and the internal current regulator PWM, it is necessary to set the internal PWM off-time, defined by the value of PW[4:0], to be longer than the external PWM period. This will ensure that the internal current regulator can only ever switch to PWM off and will avoid additional bridge switching and current ripple.

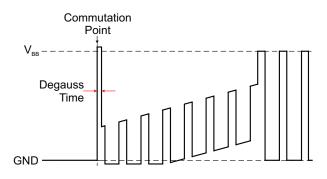

Figure 12: PWM Brake Timing - Direct Mode PWM

When operating in the direct mode, holding the PWM terminal inactive for longer than the PWM brake time ( $t_{BRK}$ ), as shown, for IPI = 0 in Figure 12, will force a brake condition if BRK = 1 and RUN = 1.

In most cases, when PWM terminal is held inactive, the motor current will decay to zero before the end of the brake time, and the motor will coast with no drive or brake torque present before the brake condition is enabled. Once the brake condition is enabled, all low-side MOSFETs in the bridge will be switched on to short the motor phase windings to each other. If the motor is still running at high speed, this will produce a very high braking current in the windings and in the MOSFETs. It is critical that the MOSFETs are selected to be able to handle this current without damage.

In cases where there is a high inertial load, and the motor cannot be allowed to coast to a stop, it is advisable to first reduce the motor speed by decreasing the demand to the A4963 by reducing the PWM input duty cycle. This will slow the motor faster than coasting but not as fast as a brake condition. Once the motor speed has be reduced to a safe level, then the brake condition can be applied.

Once enabled, the brake condition will be held until the PWM terminal is changed to its active state. At this point, if the motor operation is enabled, with RUN = 1 and BRK = 0, then the A4963 will initiate a start sequence. During the start sequence, the duty cycle of the signal on the PWM terminal is ignored, unless it is held inactive for longer than  $t_{\rm BRK}$ . If this happens, then the start sequence will terminate, and the brake condition will be enabled as above.

If the motor speed drops below the low speed threshold (25% of the start speed set by SS), then the A4963 will indicate the loss of synchronization condition by pulling the FAULTn output active low.

If the RUN and RSC bits are set to 1 and the PWM signal applied to the PWM input terminal is not 0%, then the start sequencer will reset and retry, and the FAULTn output will remain low until the completion of six full commutation periods following the hold time. This cycle will continue until stopped by holding the PWM terminal inactive or by setting RUN to 0 or RSC to 0.

If RSC = 0, the FAULTn output will continue to indicate loss of synchronization until the PWM signal applied to the PWM input terminal is 0% or RUN is set to 0.

#### Indirect Open-Loop Speed (Voltage) Control

In some motor control systems, the central ECU is used to provide application-specific speed control. In these systems, the ECU may be remote from the motor driver. It is therefore desirable in these systems to use a low-frequency PWM signal between the ECU and the motor controller to minimize EMC issues with the control signal. This is particularly relevant to systems where a brush DC motor is being replaced by a BLDC motor. The A4963 includes an indirect open-loop control option that will accept a low-frequency PWM input and provide all the detailed motor commutation and control independently from the ECU.

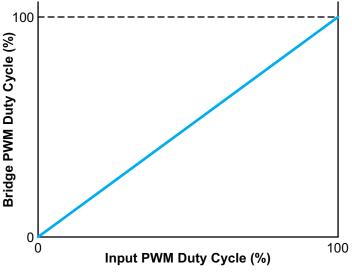

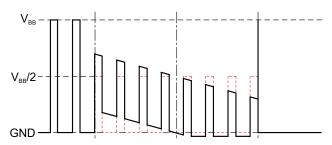

When operating in the indirect mode, the A4963 measures the duty cycle of the low-frequency signal (5 Hz to 1 kHz) applied to the PWM terminal and applies the same duty cycle to the power bridge at a higher fixed-frequency, as shown in Figure 13. The frequency of the PWM signal applied to the power

### **Sensorless BLDC Controller**

bridge is determined by the value of the PW[4:0] variable. The A4963 will also provide current limiting using the internal fixed off-time closed-loop current regulator synchronized with the bridge PWM control signal. The fixed off-time of the current control circuit will be the same as the programmed bridge PWM period defined by the value of PW[4:0]. This will ensure that the current control circuit does not cause excessive PWM switching and can only switch the bridge into the PWM-on state when 100% duty cycle is required and the motor torque is at the limit.

Figure 13: Bridge PWM vs. Input PWM

The A4963 does not limit the minimum or maximum duty cycle applied to the bridge. The PWM signal applied to the PWM terminal can have any value between 0 and 100%. At 100%, the motor will be running at full speed as determined by the load and the applied voltage. At very low duty cycles, there may not be sufficient current flowing in the motor to maintain sufficient speed for sensorless operation; however, the A4963 will not limit the minimum applied duty cycle to provide full flexibility for the speed control ECU to manage the motor operation. If the motor speed drops below the low speed threshold (25% of the start speed set by SS), then the A4963 will indicate the loss of synchronization condition by repeatedly pulling the FAULTn output active low for three PWM periods and inactive for three periods.

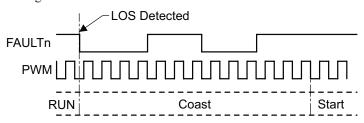

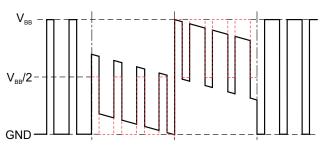

If a loss of synchronization occurs, the RUN and RSC bits are set to 1, and the PWM signal applied to the PWM input terminal is not 0%, then the FAULTn output will go active low for three PWM periods, inactive for three periods, then repeat this sequence before the start sequencer is reset and the start sequence initiated as shown in Figure 14. This cycle will continue until stopped by holding the PWM terminal inactive or

setting either the RUN bit or the RSC bit to 0.

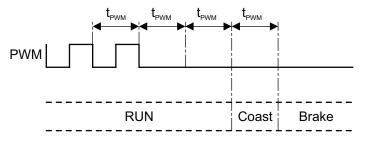

Figure 14: LOS Fault Reporting - Indirect Mode PWM

If a loss of synchronization occurs and RSC = 0, the FAULTn output will continue to indicate loss of synchronization until the PWM signal applied to the PWM input terminal is 0% or the RUN bit is set to 0. The A4963 is capable of measuring the duty cycle of any PWM signal from 5 Hz to 1 kHz. It can also accept slight variation in the PWM frequency from cycle to cycle. However, any variation will be translated to a duty cycle error. If the PWM signal remains in the inactive state for more than twice the length of time of the last measured period then the A4963 will put the bridge into the PWM-off state permanently and allow the motor current to decay. Holding the PWM signal inactive for a further PWM period, as shown in Figure 15, will force a brake condition if BRK = 1 and RUN = 1.

Figure 15: PWM Brake Timing - Indirect Mode PWM

Once enabled, the brake condition will be held until the PWM terminal is changed to its active state. If the motor operation is enabled, with RUN = 1 and BRK = 0, then the A4963 will initiate a start sequence. Once the start sequence is initiated, the duty cycle of the signal on the PWM terminal is monitored as above but not passed to the bridge drive circuits until the completion of six full commutation periods (one electrical cycle) following the hold time. During the start sequence, if the PWM signal is held inactive as described above, then the start sequence will be terminated and the brake condition will be forced.

#### **Closed-Loop Torque (Current) Control**

The A4963 provides a fixed off-time current limiting system that can operate with an applied PWM or in a standalone mode. By

### **Sensorless BLDC Controller**

disabling all other control modes, this current limit can be used to provide closed-loop torque limited motor control.

At the start of the cycle, the bridge is enabled to force current from the supply through the load to ground. This is the PWM-on state. The current flows through a ground-referenced sense resistor which provides a voltage proportional to the current. This voltage is monitored using a differential sense amplifier, where the output is compared to a threshold voltage (V<sub>ILIM</sub>) representing the peak current limit in the load. When the sensed current exceeds the limit, the bridge is switched to the PWM-off state. The PWM-off state is held for the duration of the fixed off-time defined by the value stored in PW[4:0]. This allows the current in the load to decay below the reference limit. At the end of the fixed off-time, the bridge is switched back to the PWM-on state to force the current to rise again. This sequence repeats and produces a ripple current, where the peak current is limited to a controlled level, and the amplitude of the ripple is determined by the motor parameters and the fixed off-time.

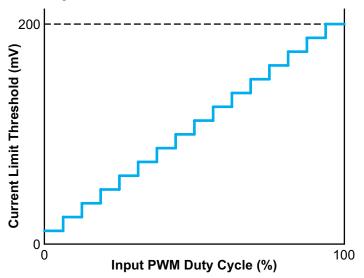

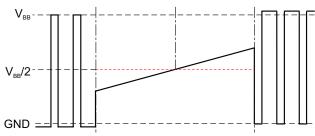

Figure 16: Current Demand vs. Input PWM

In the closed-loop torque control mode, the current limit threshold voltage is adjusted using a PWM signal or optionally via the serial interface. As in the indirect open-loop speed control mode, the PWM signal applied to the PWM terminal is monitored. In this case the duty cycle ratio of the applied PWM signal is translated to the current limit threshold voltage ( $V_{\rm ILIM}$ ) which is proportional to the PWM duty cycle. The duty cycle of the signal on the PWM input terminal is measured to 8-bit resolution, and the most significant 4 bits are used to set the value of  $V_{\rm ILIM}$ . The relationship between the input duty cycle and  $V_{\rm ILIM}$  is shown in Figure 16.

The applied PWM signal can have a frequency from 5 Hz to 1 kHz. It can also accept slight variation in the PWM frequency from cycle to cycle; however, any variation will be translated to a duty cycle error which will cause a disturbance in the current reference. If the PWM signal remains in the inactive state for more than twice the length of time of the last measured period, then the A4963 will put the bridge into the PWM-off state permanently and allow the motor current to decay. Holding the PWM signal inactive for a further PWM period will force a brake condition if BRK = 1 and RUN = 1.

Once enabled, the brake condition will be held until the PWM terminal is changed to its active state. If the motor operation is enabled, with RUN = 1 and BRK = 0, then the A4963 will initiate a start sequence.

After the start sequence is initiated, the duty cycle of the signal on the PWM terminal is monitored as above, but the resulting current reference level is ignored until the completion of six full commutation periods (one electrical cycle) following the hold time. During the start sequence, if the PWM signal is held inactive as described above, then the start sequence will be terminated and the brake condition will be forced.

If the motor speed drops below the low speed threshold (25% of the start speed set by SS), then the A4963 will indicate the loss of synchronization condition by repeatedly pulling the FAULTn output active low for three PWM periods and inactive for three periods.

If a loss of synchronization occurs, the RUN and RSC bits are set to 1, and the PWM signal applied to the PWM input terminal is not 0%, then the FAULTn output will go active low for three PWM periods, inactive for three periods, then repeat this sequence before the start sequencer is reset and the start sequence initiated as shown in Figure 14. This cycle will continue until stopped by holding the PWM terminal inactive or setting either the RUN bit or the RSC bit to 0.

If a loss of synchronization occurs, and RSC = 0, the FAULTn output will continue to indicate loss of synchronization until the PWM signal applied to the PWM input terminal is 0% or the RUN bit is set to 0.

#### **Closed-Loop Speed Control**

For systems where closed-loop speed control is required and no external controller is available, the A4963 includes a full PI (proportional/integral) speed control loop. The motor state and speed are determined by the duty cycle input to the PWM terminal or optionally via the serial interface. The speed demand

### **Sensorless BLDC Controller**

reference to the PI control loop is determined by the duty cycle of the PWM input signal as a percentage of the maximum speed  $(f_{MAX})$ . This is set by the value in the SMX[2:0] variable as:

$$f_{MAX} = 0.1 \times (2^{(SMX + 8)} - 1) Hz$$

$f_{MAX}$  for each value of SMX is listed in Table 2. This also shows the equivalent motor speed (in rpm) for several motor pole-pair options.

Table 2: Max Speed

| SMX   | f <sub>MAX</sub> | IV     | lotor Pole | Pairs (Sp | eed in rpn | 1)    |

|-------|------------------|--------|------------|-----------|------------|-------|

| SIVIA | (Hz)             | 1      | 2          | 3         | 4          | 6     |

| 0     | 25.5             | 1530   | 765        | 510       | 383        | 255   |

| 1     | 51.1             | 3066   | 1533       | 1022      | 767        | 511   |

| 2     | 102.3            | 6138   | 3069       | 2046      | 1535       | 1023  |

| 3     | 204.7            | 12282  | 6141       | 4094      | 3071       | 2047  |

| 4     | 409.5            | 24570  | 12285      | 8190      | 6143       | 4095  |

| 5     | 819.1            | 49146  | 24573      | 16382     | 12287      | 8191  |

| 6     | 1638.3           | 98298  | 49149      | 32766     | 24575      | 16383 |

| 7     | 3276.7           | 196602 | 98301      | 65534     | 49151      | 32767 |

The closed-loop speed controller compares the speed demand, represented by the duty cycle of signal applied to the PWM input terminal, to the motor speed represented by the electrical cycle frequency. It then sets the duty cycle of the internal, higher-frequency bridge PWM signal to adjust the motor speed. The frequency of the PWM signal applied to the power bridge is determined by the value of the PW[4:0] variable. The A4963 will also provide current limiting using the internal fixed off-time closed-loop current regulator synchronized with the bridge PWM control signal. The fixed off-time of the current control circuit will be the same as the programmed bridge PWM period defined by the value of PW[4:0]. This will ensure that the current control circuit does not cause excessive PWM switching and can only switch the bridge into the PWM-on state when 100% duty cycle is required and the motor torque is at the limit.

The dynamic response of the speed controller can be tuned to the motor and load dynamics by independently setting the gains for the proportional and the integral paths in the closed-loop speed controller. The proportional gain is set by the contents of the SP[2:0] variable and the integral gain by the contents of the SI[2:0] variable.

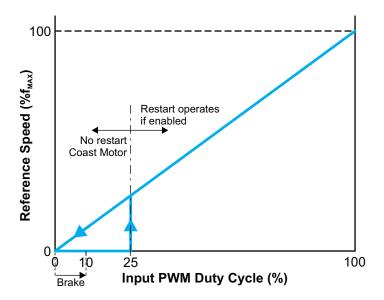

Figure 17: Speed vs. Input PWM

The PWM signal applied to the PWM terminal can have a frequency from 5 Hz to 1 kHz. It can also accept slight variation in the PWM frequency from cycle to cycle; however, any variation will be translated to a duty cycle error which will cause a disturbance in the speed reference.

If the PWM signal remains in the inactive state for more than twice the length of time of the last measured period, then the A4963 will put the bridge into the PWM-off state and allow the motor current to decay. Holding the PWM signal inactive for a further PWM period will force a brake condition if BRK = 1 and RUN = 1.

Once enabled, or following a power-on-reset, the brake condition will be held, if BRK = 1 and RUN = 1, until the duty cycle of the PWM signal is greater than 10%. When BRK = 0, braking is disabled regardless of the PWM input. The brake condition can only be applied when the PWM signal rises from 0% and remains under 10%. The brake condition is not applied if the motor has been running and the PWM signal remains greater than 0% even if it is less than 10%.

Following a brake condition, when the motor is not running, a duty cycle between 10% and 25% on the PWM signal disables the bridge drive and allows the motor to coast. When the duty cycle of the PWM signal exceeds 25%, the A4963 initiates a start sequence, and the motor is allowed to run.

After the start sequence is initiated, the duty cycle of the signal on the PWM terminal is monitored, but the resulting speed

### **Sensorless BLDC Controller**

demand reference level is ignored until the completion of two commutation periods following the hold time. During the start sequence, if the PWM signal is held inactive as described above, then the start sequence will be terminated, and the brake condition will be forced.

Once sensorless operation is achieved, the motor speed will change to match the speed demand reference determined by the duty cycle of the input PWM signal. The speed then continues to match the demand without being affected by varying supply voltage or load, up to the torque limit imposed by either the peak current limiter or effective applied voltage limited by the motor bemf.

As the duty cycle of the PWM signal reduces, the motor speed will follow until the speed is either too low to maintain sensorless operation or the demand is less than the low speed threshold. The low speed threshold is 25% of the start speed set by SS. At this point, the A4963 will turn off all bridge MOSFETs allowing the motor to coast. The A4963 will then indicate a loss of synchronization condition by repeatedly pulling the FAULTn output active low for three PWM periods and inactive for three periods.

If a loss of synchronization occurs, the RUN and RSC bits are set to 1, and the PWM signal applied to the PWM input terminal is greater than 25%, then the FAULTn output will go active low for three PWM periods, inactive for three periods, then repeat this sequence before the start sequencer is reset and the start sequence initiated as shown in Figure 14. This cycle will continue until stopped by holding the PWM terminal inactive or setting either the RUN bit or the RSC bit to 0.

If a loss of synchronization occurs and RSC = 0, the FAULTn output will continue to indicate loss of synchronization until the PWM signal applied to the PWM input terminal is less than 25% or the RUN bit is set to 0.

#### **Power Supplies**

A single power supply voltage is required. This directly supplies the analog and output drive sections. An internal regulator provides a lower fixed logic supply. TTL threshold logic inputs allow the inputs to be driven from a 3.3 or 5 V logic interface.

The A4963 can operate over a wide supply voltage range. Electrical parameters are fully defined from 6 to 28 V; however, it will function correctly up to 50 V during load dump conditions and will achieve full operation down to 4.2 V during cold crank conditions. Below 6 V and above 28 V, some parameters may marginally exceed the limits specified for the normal supply voltage range. The A4963 will function correctly with a VBB

supply down to 4.2 V; however, full sensorless startup may not be possible below 5 V, as the motor bemf may be too low to allow correct operation, and there may be insufficient torque to allow correct startup. In this case, assuming the control conditions allow motor start, the A4963 will continue to force the motor phases to commutate in a repeating start sequence.

The main power supply should be connected to VBB through a reverse voltage protection circuit and should be decoupled with ceramic capacitors connected close to the supply and ground terminals. The supply to the MOSFET bridge should include large electrolytic capacitors that are rated to provide the motor ripple current.

#### **Gate Drive and Bridge PWM**

The A4963 is designed to drive external, low on-resistance, power n-channel (low-side) and p-channel (high-side) MOS-FETs. It supplies the large transient currents necessary to quickly charge and discharge the external FET gate capacitance to reduce dissipation in the FET during switching. The charge and discharge rate can be controlled using an external resistor in series with the connection to the gate of the FET.

#### **Gate Drive Voltage Regulation**

The gate drives are powered directly from the VBB supply, but each drive output incorporates an internal regulator which limits the voltage to the drive outputs and therefore the maximum gate-source voltage applied to the external MOSFETs.

#### Low-Side Gate Drive

The low-side, gate drive outputs on GLA, GLB, and GLC are referenced to the GND terminal. These outputs are designed to drive external N-channel power MOSFETs. External resistors between the gate drive output and the gate connection to the MOSFET (as close as possible to the MOSFET) can be used to control the slew rate seen at the gate, thereby providing some control of the di/dt and dv/dt of the voltage at the SA/SB/SC terminals.