# **AD8058ARM Datasheet**

https://www.DiGi-Electronics.com

DiGi Electronics Part Number AD8058ARM-DG

Manufacturer Analog Devices Inc.

Manufacturer Product Number AD8058ARM

Description IC VOLTAGE FEEDBACK 2 CIRC 8MSOP

Detailed Description Voltage Feedback Amplifier 2 Circuit 8-MSOP

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

## **Purchase and inquiry**

| Manufacturer Product Number: | Manufacturer:                          |

|------------------------------|----------------------------------------|

| AD8058ARM                    | Analog Devices Inc.                    |

| Series:                      | Product Status:                        |

|                              | Obsolete                               |

| Amplifier Type:              | Number of Circuits:                    |

| Voltage Feedback             | 2                                      |

| Output Type:                 | Slew Rate:                             |

|                              | 1150V/µs                               |

| Gain Bandwidth Product:      | -3db Bandwidth:                        |

| 100 MHz                      | 325 MHz                                |

| Current - Input Bias:        | Voltage - Input Offset:                |

| 500 nA                       | 1 mV                                   |

| Current - Supply:            | Voltage - Supply Span (Min):           |

| 14mA                         | 3 V                                    |

| Voltage - Supply Span (Max): | Operating Temperature:                 |

| 12 V                         | -40°C ~ 85°C                           |

| Mounting Type:               | Package / Case:                        |

| Surface Mount                | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width) |

| Supplier Device Package:     | Base Product Number:                   |

| 8-MSOP                       | AD8058                                 |

## **Environmental & Export classification**

| Moisture Sensitivity Level (MSL): | ECCN: |

|-----------------------------------|-------|

| 1 (Unlimited)                     | EAR99 |

| HTSUS:                            |       |

| 8542.33.0001                      |       |

# Low Cost, High Performance Voltage Feedback, 325 MHz Amplifier

Data Sheet AD8057/AD8058

#### **FEATURES**

Low cost single (AD8057) and dual (AD8058) High speed 325 MHz, -3 dB bandwidth (G = +1) 1000 V/μs slew rate Gain flatness: 0.1 dB to 28 MHz Low noise

7 nV/√Hz Low power

5.4 mA/amplifier typical supply current at 5 V Low distortion

-85 dBc at 5 MHz,  $R_L = 1$  k $\Omega$  Wide supply range from 3 V to 12 V

Small packaging

AD8057 is available in an 8-lead SOIC and 5-lead SOT-23

AD8058 is available in an 8-lead SOIC and an 8-lead MSOP

#### **APPLICATIONS**

Imaging

DVD/CD

Photodiode preamp

Analog-to-digital driver

Professional cameras filters

#### **GENERAL DESCRIPTION**

The AD8057 (single) and AD8058 (dual) are very high performance amplifiers with a very low cost. The balance between cost and performance make them ideal for many applications. The AD8057 and AD8058 reduce the need to qualify a variety of specialty amplifiers. The AD8057 and AD8058 are voltage feedback amplifiers with the bandwidth and slew rate normally found in current feedback amplifiers. The AD8057 and AD8058 are low power amplifiers having low quiescent current and a wide supply range from 3 V to 12 V. They have noise and distortion performance required for high end video systems as well as dc performance parameters rarely found in high speed amplifiers.

The AD8057 and AD8058 are available in standard SOIC packaging as well as tiny 5-lead SOT-23 (AD8057) and 8-lead MSOP (AD8058) packages. These amplifiers are available in the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

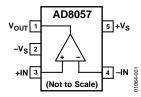

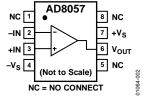

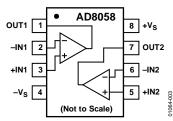

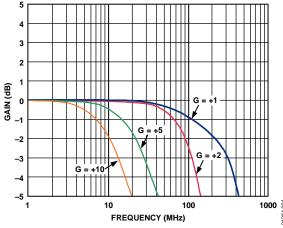

#### **CONNECTION DIAGRAMS**

Figure 1. RT-5 (SOT-23)

Figure 2. R-8 (SOIC)

Figure 3. RM-8 (MSOP) and R-8 (SOIC)

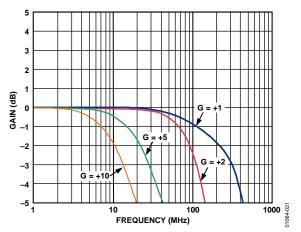

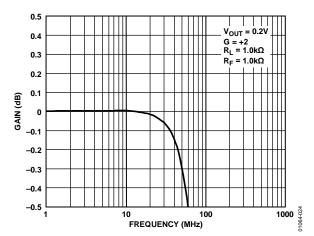

Figure 4. Small Signal Frequency Response

## **TABLE OF CONTENTS**

| Features1                                                                                                    |

|--------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                |

| Connection Diagrams1                                                                                         |

| General Description1                                                                                         |

| Revision History2                                                                                            |

| Specifications3                                                                                              |

| Absolute Maximum Ratings 5                                                                                   |

| Maximum Power Dissipation5                                                                                   |

| ESD Caution5                                                                                                 |

|                                                                                                              |

| REVISION HISTORY                                                                                             |

| 3/14—Rev. D to Rev. E                                                                                        |

| Change to Figure 4814                                                                                        |

| 9/13—Rev. C to Rev. D                                                                                        |

| Changes to Output Voltage Swing Parameter, Table 34 Updated Outline Dimensions15 Changes to Ordering Guide16 |

| 10/10—Rev. B to Rev. C                                                                                       |

| Updated Format                                                                                               |

| Changes to Figure 35                                                                                         |

| Changes to Figure 41 and Figure 42                                                                           |

| Changes to Figure 44 and Figure 45                                                                           |

| Typical Performance Characteristics6    |

|-----------------------------------------|

| Test Circuits                           |

| Applications Information                |

| Driving Capacitive Loads                |

| Video Filter 13                         |

| Differential Analog-to-Digital Driver14 |

| Layout                                  |

| Outline Dimensions                      |

| Ordering Guide                          |

|                                         |

| 8/03—Rev. A to Rev. B                   |

| Renumbered Figures and TPCsUniversa     |

| Changes to Ordering Guide               |

## **SPECIFICATIONS**

At  $T_A$  = 25°C,  $V_S$  = ±5 V,  $R_L$  = 100  $\Omega,\,R_F$  = 0  $\Omega,\,gain$  = +1, unless otherwise noted.

Table 1.

| Parameter                                          | Conditions                                                             | Min   | Тур  | Max   | Unit    |

|----------------------------------------------------|------------------------------------------------------------------------|-------|------|-------|---------|

| DYNAMIC PERFORMANCE                                |                                                                        |       |      |       |         |

| -3 dB Bandwidth                                    | $G = +1, V_0 = 0.2 \text{ V p-p}$                                      |       | 325  |       | MHz     |

|                                                    | $G = -1, V_0 = 0.2 \text{ V p-p}$                                      |       | 95   |       | MHz     |

|                                                    | $G = +1, V_0 = 2 V p-p$                                                |       | 175  |       | MHz     |

| Bandwidth for 0.1 dB Flatness                      | $G = +1, V_0 = 0.2 \text{ V p-p}$                                      |       | 30   |       | MHz     |

| Slew Rate                                          | $G = +1$ , $V_0 = 2 \text{ V step}$ , $R_L = 2 \text{ k}\Omega$        |       | 850  |       | V/µs    |

|                                                    | $G = +1$ , $V_0 = 4$ V step, $R_L = 2$ k $\Omega$                      |       | 1150 |       | V/µs    |

| Settling Time to 0.1%                              | $G = +2, V_0 = 2 V step$                                               |       | 30   |       | ns      |

| NOISE/HARMONIC PERFORMANCE                         |                                                                        |       |      |       |         |

| Total Harmonic Distortion                          | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 1 \text{ k}\Omega$  |       | -85  |       | dBc     |

|                                                    | $f_C = 20 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 1 \text{ k}\Omega$ |       | -62  |       | dBc     |

| SFDR                                               | $f = 5 \text{ MHz}, V_0 = 2 \text{ V p-p}, R_L = 150 \Omega$           |       | -68  |       | dB      |

| Third-Order Intercept                              | $f = 5 \text{ MHz}, V_0 = 2 \text{ V p-p}$                             |       | -35  |       | dBm     |

| Crosstalk, Output to Output                        | f = 5  MHz, G = +2                                                     |       | -60  |       | dB      |

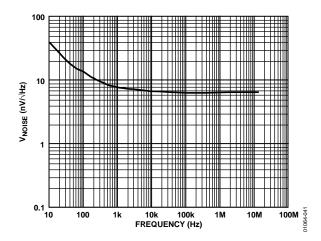

| Input Voltage Noise                                | f = 100 kHz                                                            |       | 7    |       | nV/√Hz  |

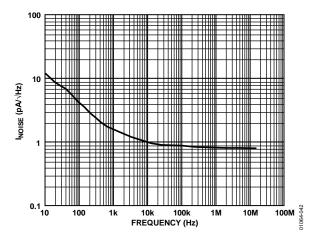

| Input Current Noise                                | f = 100 kHz                                                            |       | 0.7  |       | pA/√Hz  |

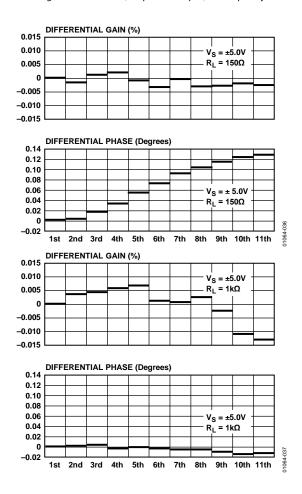

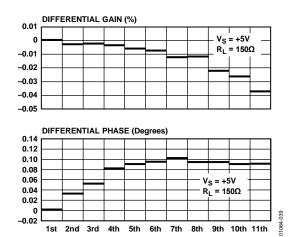

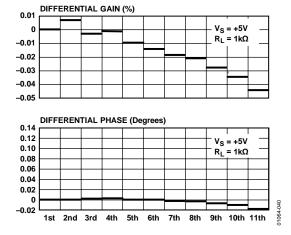

| Differential Gain Error                            | NTSC, $G = +2$ , $R_L = 150 \Omega$                                    |       | 0.01 |       | %       |

|                                                    | NTSC, $G = +2$ , $R_L = 1 \text{ k}\Omega$                             |       | 0.02 |       | %       |

| Differential Phase Error                           | NTSC, $G = +2$ , $R_L = 150 \Omega$                                    |       | 0.15 |       | Degrees |

|                                                    | NTSC, $G = +2$ , $R_L = 1 \text{ k}\Omega$                             |       | 0.01 |       | Degrees |

| Overload Recovery                                  | $V_{IN} = 200 \text{ mV p-p, G} = +1$                                  |       | 30   |       | ns      |

| DC PERFORMANCE                                     |                                                                        |       |      |       |         |

| Input Offset Voltage                               |                                                                        |       | 1    | 5     | mV      |

|                                                    | T <sub>MIN</sub> to T <sub>MAX</sub>                                   |       | 2.5  |       | mV      |

| Input Offset Voltage Drift                         |                                                                        |       | 3    |       | μV/°C   |

| Input Bias Current                                 |                                                                        |       | 0.5  | 2.5   | μA      |

|                                                    | T <sub>MIN</sub> to T <sub>MAX</sub>                                   |       | 3.0  |       | μΑ      |

| Input Offset Current                               |                                                                        |       |      | ±0.75 | μA      |

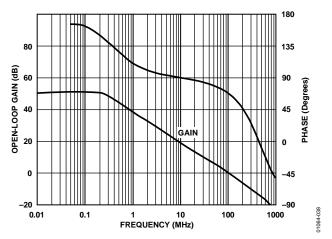

| Open-Loop Gain                                     | $V_0 = \pm 2.5 \text{ V}, R_L = 2 \text{ k}\Omega$                     | 50    | 55   |       | dB      |

|                                                    | $V_0 = \pm 2.5 \text{ V}, R_L = 150 \Omega$                            | 50    | 52   |       | dB      |

| INPUT CHARACTERISTICS                              | V0 - ±2.5 V, NL - 150 22                                               | 30    | 32   |       | ив      |

| Input Resistance                                   |                                                                        |       | 10   |       | ΜΩ      |

| Input Resistance Input Capacitance                 | Hamut                                                                  |       | 2    |       |         |

| Input Capacitance Input Common-Mode Voltage Range  | +Input $R_L = 1 \text{ k}\Omega$                                       | -4.0  | 2    | +4.0  | pF<br>V |

|                                                    |                                                                        | 48    | 60   | +4.0  | dB      |

| Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS | $V_{CM} = \pm 2.5 \text{ V}$                                           | 40    | 60   |       | иь      |

|                                                    | D 210                                                                  | 4.0   |      | . 4.0 | W       |

| Output Voltage Swing                               | $R_L = 2 k\Omega$                                                      | -4.0  | .20  | +4.0  | V       |

| Conscisions Load Drive                             | $R_L = 150 \Omega$                                                     |       | ±3.9 |       |         |

| Capacitive Load Drive                              | 30% overshoot                                                          |       | 30   |       | pF      |

| POWER SUPPLY                                       |                                                                        | . 4 5 |      |       | V       |

| Operating Range                                    |                                                                        | ±1.5  | ±5.0 | ±6    | V       |

| Quiescent Current for AD8057                       |                                                                        |       | 6.0  | 7.5   | mA      |

| Quiescent Current for AD8058                       | W                                                                      |       | 14.0 | 15    | mA      |

| Power Supply Rejection Ratio                       | $V_S = \pm 5 \text{ V to } \pm 1.5 \text{ V}$                          | 54    | 59   |       | dB      |

At  $T_{\text{A}}$  = 25°C,  $V_{\text{S}}$  = 5 V,  $R_{\text{L}}$  = 100  $\Omega,$   $R_{\text{F}}$  = 0  $\Omega,$  gain = +1, unless otherwise noted.

Table 2.

| Parameter                                                  | Conditions                                                              | Min | Тур        | Max       | Unit    |

|------------------------------------------------------------|-------------------------------------------------------------------------|-----|------------|-----------|---------|

| DYNAMIC PERFORMANCE                                        |                                                                         |     |            |           |         |

| –3 dB Bandwidth                                            | $G = +1, V_0 = 0.2 \text{ V p-p}$                                       |     | 300        |           | MHz     |

|                                                            | $G = +1, V_0 = 2 V p-p$                                                 |     | 155        |           | MHz     |

| Bandwidth for 0.1 dB Flatness                              | $V_0 = 0.2 \text{ V p-p}$                                               |     | 28         |           | MHz     |

| Slew Rate                                                  | $G = +1$ , $V_O = 2 \text{ V step}$ , $R_L = 2 \text{ k}\Omega$         |     | 700        |           | V/µs    |

| Settling Time to 0.1%                                      | $G = +2, V_0 = 2 V \text{ step}$                                        |     | 35         |           | ns      |

| NOISE/HARMONIC PERFORMANCE                                 |                                                                         |     |            |           |         |

| Total Harmonic Distortion                                  | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 1 \text{ k}\Omega$   |     | -75        |           | dBc     |

|                                                            | $f_C = 20 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 1 \text{ k}\Omega$  |     | -54        |           | dBc     |

| Crosstalk, Output to Output                                | f = 5  MHz, G = +2                                                      |     | -60        |           | dB      |

| Input Voltage Noise                                        | f = 100 kHz                                                             |     | 7          |           | nV/√Hz  |

| Input Current Noise                                        | f = 100 kHz                                                             |     | 0.7        |           | pA/√Hz  |

| Differential Gain Error                                    | NTSC, $G = +2$ , $R_L = 150 \Omega$                                     |     | 0.05       |           | %       |

|                                                            | NTSC, $G = +2$ , $R_L = 1 \text{ k}\Omega$                              |     | 0.05       |           | %       |

| Differential Phase Error                                   | NTSC, $G = +2$ , $R_L = 150 \Omega$                                     |     | 0.10       |           | Degrees |

|                                                            | NTSC, $G = +2$ , $R_L = 1 \text{ k}\Omega$                              |     | 0.02       |           | Degrees |

| DC PERFORMANCE                                             |                                                                         |     |            |           |         |

| Input Offset Voltage                                       |                                                                         |     | 1          | 5         | mV      |

|                                                            | T <sub>MIN</sub> to T <sub>MAX</sub>                                    |     | 2.5        |           | mV      |

| Input Offset Voltage Drift                                 |                                                                         |     | 3          |           | μV/°C   |

| Input Bias Current                                         |                                                                         |     | 0.5        | 2.5       | μA      |

| ·                                                          | T <sub>MIN</sub> to T <sub>MAX</sub>                                    |     | 3.0        |           | μA      |

| Input Offset Current                                       |                                                                         |     |            | 0.75      | μA      |

| Open-Loop Gain                                             | $V_0 = \pm 1.5 \text{ V}, R_L = 2 \text{ k}\Omega \text{ to midsupply}$ | 50  | 55         |           | dB      |

|                                                            | $V_0 = \pm 1.5 \text{ V}$ , $R_L = 150 \Omega$ to midsupply             |     |            |           | dB      |

| INPUT CHARACTERISTICS                                      | ν <sub>0</sub> – ±1.5 ν, κ <sub>L</sub> = 150 Ω το ππασαρρίγ            | 73  | 32         |           | GD.     |

| Input Resistance                                           |                                                                         |     | 10         |           | ΜΩ      |

| Input Capacitance                                          | +Input                                                                  |     | 2          |           | pF      |

| Input Capacitance Input Common-Mode Voltage Range          | $R_L = 1 k\Omega$                                                       |     | 0.9 to 3.4 |           | V       |

| Common-Mode Rejection Ratio                                | $V_{CM} = \pm 2.5 \text{ V}$                                            | 48  | 60         |           | dB      |

| OUTPUT CHARACTERISTICS                                     | VCM — ±2.5 V                                                            | 40  |            |           | GD.     |

| Output Voltage Swing                                       | $R_{l} = 2 k\Omega$                                                     |     | 0.9 to 3.8 |           | V       |

| Output voltage Swing                                       | $R_L = 150 \Omega$                                                      |     | 1.2 to 3.4 |           | V       |

| Capacitive Load Drive                                      | 30% overshoot                                                           |     | 30         |           | pF      |

| POWER SUPPLY                                               | 3070 0401311001                                                         |     |            |           | Pi      |

| Operating Range                                            |                                                                         | 3   | 5.0        | 10        | V       |

| Quiescent Current for AD8057                               |                                                                         | ر   | 5.0<br>5.4 | 7.0       | mA      |

| Ouiescent Current for AD8057  Ouiescent Current for AD8058 |                                                                         |     | 13.5       | 7.0<br>14 | mA      |

| •                                                          |                                                                         | 54  | 13.5<br>58 | 14        | dB      |

| Power Supply Rejection Ratio                               |                                                                         | 34  | 30         |           | ub      |

#### ABSOLUTE MAXIMUM RATINGS

Table 3.

| Parameter                                            | Rating          |

|------------------------------------------------------|-----------------|

| Supply Voltage (+V <sub>S</sub> to −V <sub>S</sub> ) | 12.6 V          |

| Internal Power Dissipation <sup>1</sup>              |                 |

| SOIC Package (R)                                     | 0.8 W           |

| SOT-23-5 Package (RT)                                | 0.5 W           |

| MSOP Package (RM)                                    | 0.6 W           |

| Input Voltage (Common Mode)                          | ±V <sub>S</sub> |

| Differential Input Voltage                           | ±4.0 V          |

| Output Short-Circuit Duration                        | Observe power   |

|                                                      | derating curves |

| Storage Temperature Range (R)                        | −65°C to +125°C |

| Operating Temperature Range (A Grade)                | −40°C to +85°C  |

|                                                      |                 |

| Lead Temperature (Soldering 10sec)                   | 300°C           |

<sup>&</sup>lt;sup>1</sup> Specification is for device in free air:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

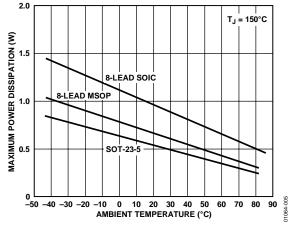

#### **MAXIMUM POWER DISSIPATION**

The maximum power that can be safely dissipated by the AD8057/AD8058 is limited by the associated rise in junction temperature. Exceeding a junction temperature of 175°C for an extended period can result in device failure. Although the AD8057/AD8058 is internally short-circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves.

Figure 5. Maximum Power Dissipation vs. Ambient Temperature

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>8-</sup>lead SOIC package:  $\theta_{JA} = 160^{\circ}\text{C/W}$

<sup>5-</sup>lead SOT-23-5 package:  $\theta_{JA} = 240^{\circ}$ C/W

<sup>8-</sup>Lead MSOP package:  $\theta_{JA} = 200^{\circ}\text{C/W}$

## TYPICAL PERFORMANCE CHARACTERISTICS

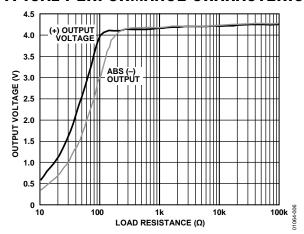

Figure 6. Output Swing vs. Load Resistance

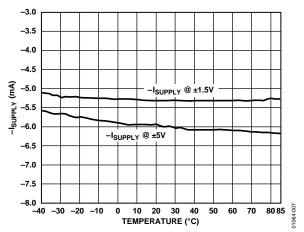

Figure 7. – Isupply vs. Temperature

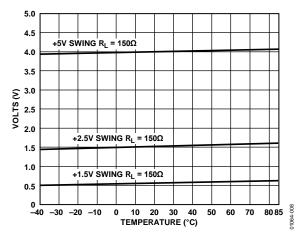

Figure 8. Positive Output Voltage Swing vs. Temperature

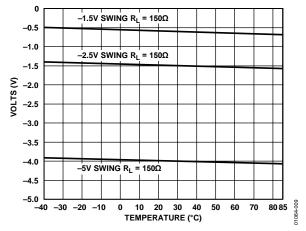

Figure 9. Negative Output Voltage Swing vs. Temperature

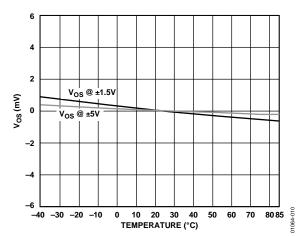

Figure 10. Vos vs. Temperature

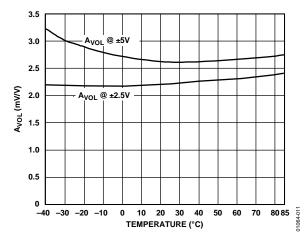

Figure 11. Open-Loop Gain vs. Temperature

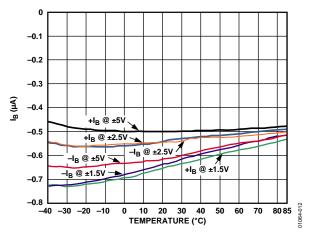

Figure 12. Input Bias Current vs. Temperature

Figure 13. PSRR vs. Temperature

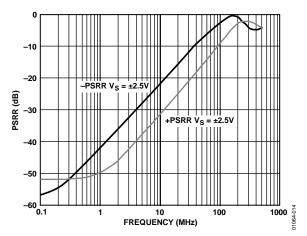

Figure 14. PSRR vs. Frequency

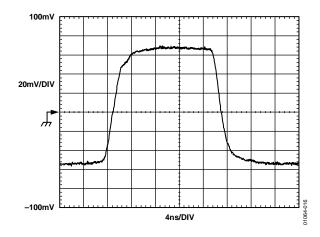

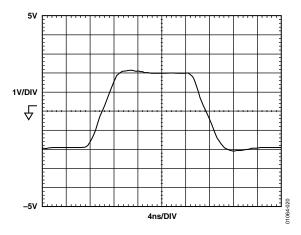

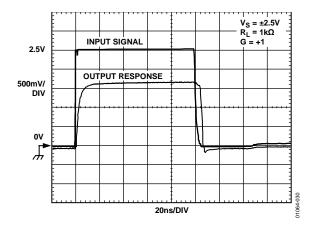

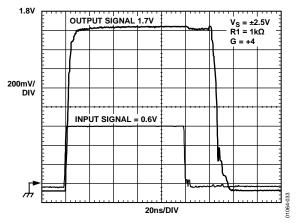

Figure 15. Small Signal Step Response G=+1,  $R_L=1$   $k\Omega$ ,  $V_S=\pm5$  V, See Figure 41 for Test Circuit

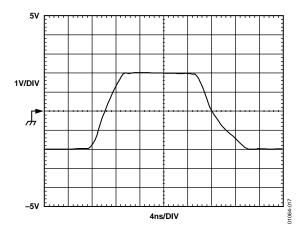

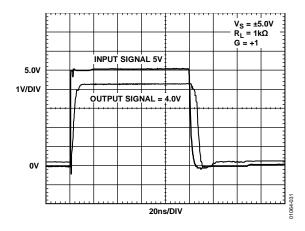

Figure 16. Large Signal Step Response G=+1,RL=1 k $\Omega$ ,  $V_S=\pm5.0$  V, See Figure 41 for Test Circuit

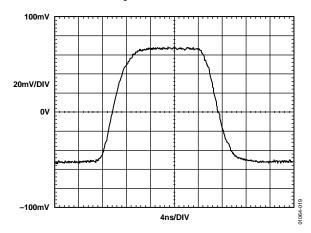

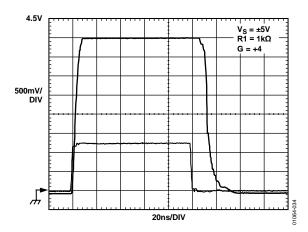

Figure 17. Small Signal Step Response G = -1,  $R_L = 1 \text{ k}\Omega$ , See Figure 42 for Test Circuit

Figure 18. Large Signal Step Response G=-1,  $R_L=1~k\Omega$ , See Figure 42 for Test Circuit

Figure 19. Small Signal Frequency Response,  $V_{OUT} = 0.2 \text{ V } p\text{-}p$

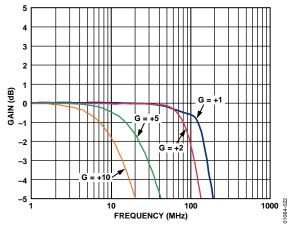

Figure 20. Large Signal Frequency Response,  $V_{OUT} = 2 V p-p$

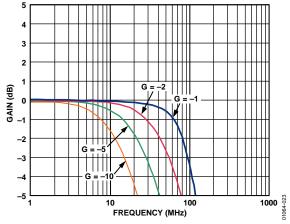

Figure 21. Large Signal Frequency Response

Figure 22. 0.1 dB Flatness G = +2

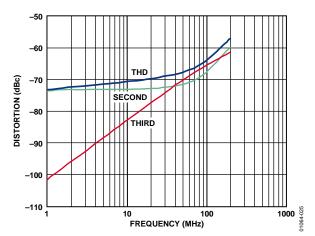

Figure 23. Distortion vs. Frequency,  $R_L = 150 \Omega$

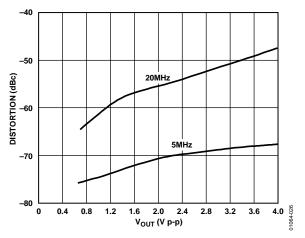

Figure 24. Distortion vs.  $V_{OUT}$  at 20 MHz, 5 MHz,  $R_L = 150 \Omega$ ,  $V_S = \pm 5.0 V$

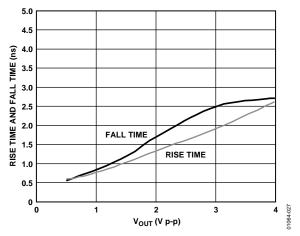

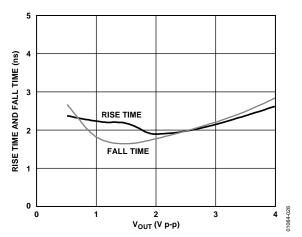

Figure 25. Rise Time and Fall Time vs.  $V_{OUT}$ , G=+1,  $R_L=1$   $k\Omega$ ,  $R_F=0$   $\Omega$

Figure 26. Rise Time and Fall Time vs.  $V_{OUT}$ , G=+2,  $R_L=100~\Omega$ ,  $R_F=402~\Omega$

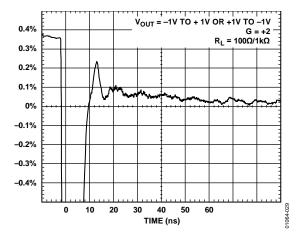

Figure 27. Settling Time

Figure 28. Input Overload Recovery,  $V_S = \pm 2.5 \text{ V}$

Figure 29. Output Overload Recovery,  $V_S = \pm 5.0 \text{ V}$

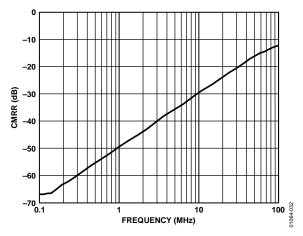

Figure 30. CMRR vs. Frequency

Figure 31. Output Overload Recovery,  $V_S = \pm 2.5 V$

Figure 32. Output Overload Recovery,  $V_S = \pm 5.0 \text{ V}$

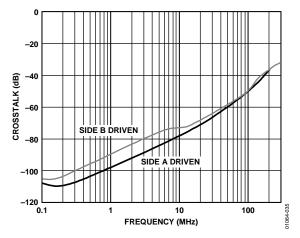

Figure 33. Crosstalk (Output-to-Output) vs. Frequency

Figure 34. Differential Gain and Differential Phase One Back Terminated Load (150  $\Omega$ ) (Video Op Amps Only)

Figure 35. Open-Loop Gain and Phase vs. Frequency

Figure 36. Differential Gain and Differential Phase,  $R_L = 150 \Omega$

Figure 37. Differential Gain and Differential Phase,  $R_L = 1 \text{ k}\Omega$

Figure 38. Voltage Noise vs. Frequency

Figure 39. Current Noise vs. Frequency

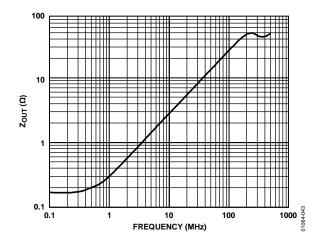

Figure 40. Output Impedance vs. Frequency

## **TEST CIRCUITS**

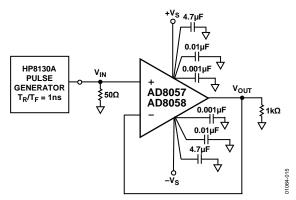

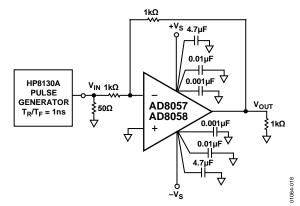

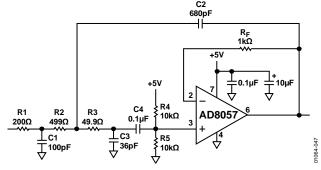

Figure 41. Test Circuit, G = +1,  $R_L = 1 k\Omega$

Figure 42. Test Circuit, G = -1,  $R_L = 1 \text{ k}\Omega$

## APPLICATIONS INFORMATION DRIVING CAPACITIVE LOADS

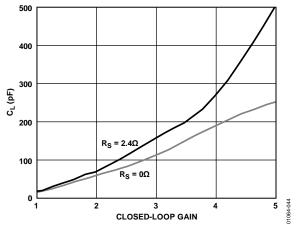

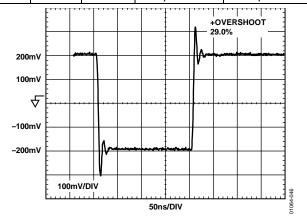

When driving a capacitive load, most op amps exhibit overshoot in their pulse response. Figure 43 shows the relationship between the capacitive load that results in 30% overshoot and the closed-loop gain of an AD8058. It can be seen that, under the gain = +2 condition, the device is stable with capacitive loads of up to 69 pF.

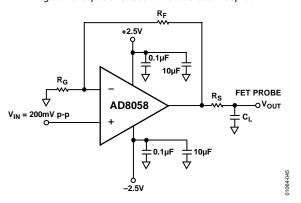

In general, to minimize peaking or to ensure device stability for larger values of capacitive loads, a small series resistor ( $R_s$ ) can be added between the op amp output and the load capacitor ( $C_L$ ) as shown in Figure 44.

For the setup shown in Figure 44, the relationship between Rs and C<sub>L</sub> was empirically derived and is shown in Table 4.

Figure 43. Capacitive Load Drive vs. Closed-Loop Gain

Figure 44. Capacitive Load Drive Circuit

Table 4. Recommended Value for Resistors R<sub>S</sub>, R<sub>F</sub>, R<sub>G</sub> vs. Capacitive Load, C<sub>L</sub>, Which Results in 30% Overshoot

| Gain | R <sub>F</sub> | R <sub>G</sub> | $C_L (R_S = 0 \Omega)$ | $C_L (R_S = 2.4 \Omega)$ |

|------|----------------|----------------|------------------------|--------------------------|

| 1    | 100 Ω          |                | 11 pF                  | 13 pF                    |

| 2    | 100 Ω          | 100 Ω          | 51 pF                  | 69 pF                    |

| 3    | 100 Ω          | 50 Ω           | 104 pF                 | 153 pF                   |

| 4    | 100 Ω          | 33.2 Ω         | 186 pF                 | 270 pF                   |

| 5    | 100 Ω          | 25 Ω           | 245 pF                 | 500 pF                   |

| 10   | 100 Ω          | 11 Ω           | 870 pF                 | 1580 pF                  |

Figure 45. Typical Pulse Response with  $C_L = 65$  pF, Gain = +2, and  $V_S = \pm 2.5$

#### **VIDEO FILTER**

Some composite video signals that are derived from a digital source contain some clock feedthrough that can cause problems with downstream circuitry. This clock feedthrough is usually at 27 MHz, which is a standard clock frequency for both NTSC and PAL video systems. A filter that passes the video band and rejects frequencies at 27 MHz can be used to remove these frequencies from the video signal.

Figure 46 shows a circuit that uses an AD8057 to create a single 5 V supply, 3-pole Sallen-Key filter. This circuit uses a single RC pole in front of a standard 2-pole active section. To shift the dc operating point to midsupply, ac coupling is provided by R4, R5, and C4.

Figure 46. Low-Pass Filter for Video

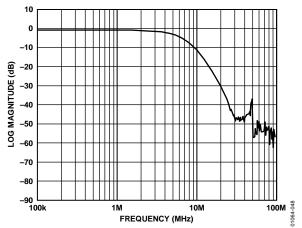

Figure 47 shows a frequency sweep of this filter. The response is down 3 dB at 5.7 MHz; therefore, it passes the video band with little attenuation. The rejection at 27 MHz is 42 dB, which provides more than a factor of 100 in suppression of the clock components at this frequency.

Figure 47. Video Filter Response

#### **DIFFERENTIAL ANALOG-TO-DIGITAL DRIVER**

As system supply voltages are dropping, many ADCs provide differential analog inputs to increase the dynamic range of the input signal while still operating on a low supply voltage. Differential driving can also reduce second and other even-order distortion products.

Analog Devices, Inc., offers an assortment of 12- and 14-bit high speed converters that have differential inputs and can be run from a single 5 V supply. These include the AD9220, AD9221, AD9223, AD9224, and AD9225 at 12 bits, and the AD9240, AD9241, and AD9243 at 14 bits. Although these devices can operate over a range of common-mode voltages at their analog inputs, they work best when the common-mode voltage at the input is at the midsupply or 2.5 V.

Op amp architectures that require upwards of 2 V of headroom at the output have significant problems when trying to drive such ADCs while operating with a 5 V positive supply. The low headroom output design of the AD8057 and AD8058 make them ideal for driving these types of ADCs.

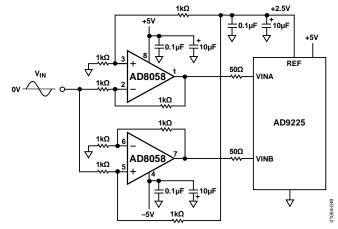

The AD8058 can be used to make a dc-coupled, single-ended-to-differential driver for one of these ADCs. Figure 48 is a schematic of such a circuit for driving an AD9225, 12-bit, 25 MSPS ADC.

Figure 48. Schematic Circuit for Driving AD9225

In this circuit, one of the op amps is configured in the inverting mode whereas the other is in the noninverting mode. However, to provide better bandwidth matching, each op amp is configured for a noise gain of +2. The inverting op amp is configured for a gain of -1 and the noninverting op amp is configured for a gain of +2. Each of these produces a noise gain of +2, which is determined only by the inverse of the feedback ratio. The input signal to the noninverting op amp is divided by two to normalize its level and make it equal to the inverting output.

For 0 V input, the outputs of the op amps want to be at 2.5 V, which is the midsupply level of the ADCs. This is accomplished by first taking the 2.5 V reference output of the ADC and dividing it by two by a pair of 1 k $\Omega$  resistors. The resulting 1.25 V is applied to the positive input of each op amp. This voltage is then multiplied by the gain of +2 of the op amps to provide a 2.5 V level at each output.

The assumption for this circuit is that the input signal is bipolar with respect to ground and the circuit must be dc-coupled thereby implying the existence of a negative supply elsewhere in the system. This circuit uses  $-5~\rm V$  as the negative supply for the AD8058.

Tying the negative supply of the AD8058 to ground causes a problem at the input of the noninverting op amp. The input common-mode voltage can only go to within 1 V of the negative rail. Because this circuit requires that the positive inputs operate with a 1.25 V bias, there is not enough room to swing this voltage in the negative direction. The inverting stage does not have this problem because its common-mode input voltage remains fixed at 1.25 V. If dc coupling is not required, various ac coupling techniques can be used to eliminate this problem.

#### **LAYOUT**

The AD8057 and AD8058 are high speed op amps for use in a board layout that follows standard high speed design rules. Make all signal traces as short and direct as possible. In particular, keep the parasitic capacitance on the inverting input of each device to a minimum to avoid excessive peaking and other undesirable performance. Bypass the power supplies very close to the power pins of the package with a 0.1  $\mu F$  capacitor in parallel with a larger (approximately 10  $\mu F$ ) tantalum capacitor. Connect these capacitors to a ground plane that either is on an inner layer or fills the area of the board that is not used for other signals.

## **OUTLINE DIMENSIONS**

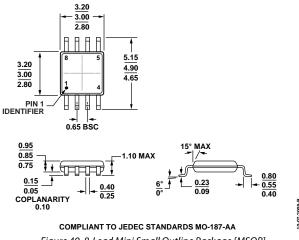

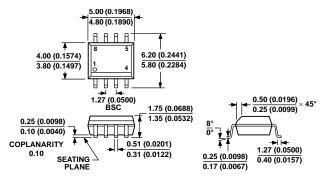

Figure 49. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

#### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 50. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches)

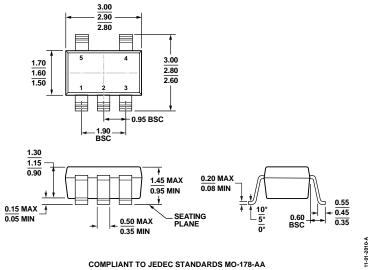

Figure 51. 5-Lead Small Outline Transistor Package [SOT-23] (RJ-5) Dimensions shown in millimeters

#### **ORDERING GUIDE**

|                    |       | Temperature    |                                 | Package    |          |

|--------------------|-------|----------------|---------------------------------|------------|----------|

| Model <sup>1</sup> | Notes | Range          | Package Description             | Option     | Branding |

| AD8057AR           |       | -40°C to +85°C | 8-Lead SOIC_N                   | R-8        |          |

| AD8057AR-REEL      |       | −40°C to +85°C | 8-Lead SOIC_N, 13"Tape and Reel | R-8        |          |

| AD8057AR-REEL7     |       | -40°C to +85°C | 8-Lead SOIC_N, 7"Tape and Reel  | R-8        |          |

| AD8057ARZ          |       | -40°C to +85°C | 8-Lead SOIC_N                   | R-8        |          |

| AD8057ARZ-REEL     |       | -40°C to +85°C | 8-Lead SOIC_N, 13"Tape and Reel | R-8        |          |

| AD8057ARZ-REEL7    |       | -40°C to +85°C | 8-Lead SOIC_N, 7"Tape and Reel  | R-8        |          |

| AD8057ACHIPS       |       | −40°C to +85°C | Die                             | Waffle Pak |          |

| AD8057ART-R2       |       | -40°C to +85°C | 5-Lead SOT-23                   | RJ-5       | H7A      |

| AD8057ART-REEL7    |       | −40°C to +85°C | 5-Lead SOT-23                   | RJ-5       | H7A      |

| AD8057ARTZ-R2      |       | -40°C to +85°C | 5-Lead SOT-23                   | RJ-5       | H08      |

| AD8057ARTZ-REEL    |       | −40°C to +85°C | 5-Lead SOT-23                   | RJ-5       | H08      |

| AD8057ARTZ-REEL7   |       | -40°C to +85°C | 5-Lead SOT-23                   | RJ-5       | H08      |

| AD8057AR-EBZ       |       | −40°C to +85°C | 8-Lead SOIC_N Evaluation Board  |            |          |

| AD8057ART-EBZ      |       | -40°C to +85°C | 5-Lead SOT-23 Evaluation Board  |            |          |

| AD8058AR           |       | -40°C to +85°C | 8-Lead SOIC_N                   | R-8        |          |

| AD8058AR-REEL7     |       | -40°C to +85°C | 8-Lead SOIC_N, 7"Tape and Reel  | R-8        |          |

| AD8058ARZ          |       | -40°C to +85°C | 8-Lead SOIC_N                   | R-8        |          |

| AD8058ARZ-REEL     |       | -40°C to +85°C | 8-Lead SOIC_N, 13"Tape and Reel | R-8        |          |

| AD8058ARZ-REEL7    |       | -40°C to +85°C | 8-Lead SOIC_N, 7"Tape and Reel  | R-8        |          |

| AD8058ACHIPS       |       | -40°C to +85°C | Die                             | Waffle Pak |          |

| AD8058ARM          |       | -40°C to +85°C | 8-Lead MSOP                     | RM-8       | H8A      |

| AD8058ARM-REEL7    |       | -40°C to +85°C | 8-Lead MSOP                     | RM-8       | H8A      |

| AD8058ARMZ-REEL7   | 2     | −40°C to +85°C | 8-Lead MSOP                     | RM-8       | H8A      |

| AD8058ARMZ         | 2     | -40°C to +85°C | 8-Lead MSOP                     | RM-8       | H8A      |

| AD8058ARMZ-REEL    | 2     | −40°C to +85°C | 8-Lead MSOP                     | RM-8       | H8A      |

| AD8058AR-EBZ       |       | -40°C to +85°C | 8-Lead SOIC_N Evaluation Board  |            |          |

| AD8058ARM-EBZ      |       | -40°C to +85°C | 8-Lead MSOP Evaluation Board    |            |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

<sup>&</sup>lt;sup>2</sup> Bottom mark has # sign before date code.

## **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com