# **AD9576BCPZ Datasheet**

D

Mai

| DiGi Electronics Part Number | AD9576BCPZ-DG                                                                    |

|------------------------------|----------------------------------------------------------------------------------|

| Manufacturer                 | Analog Devices Inc.                                                              |

| nufacturer Product Number    | AD9576BCPZ                                                                       |

| Description                  | IC CLOCK GENERATOR 64LFCSP                                                       |

| Detailed Description         | Clock Generator, Frequency Synthesizer IC 1.25GHz<br>1 64-WFQFN Exposed Pad, CSP |

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

## Purchase and inquiry

| Manufacturer Product Number:   | Manufacturer:                          |

|--------------------------------|----------------------------------------|

| AD9576BCPZ                     | Analog Devices Inc.                    |

| Series:                        | Product Status:                        |

|                                | Active                                 |

| DiGi-Electronics Programmable: | Туре:                                  |

| Not Verified                   | Clock Generator, Frequency Synthesizer |

| PLL:                           | Input:                                 |

| Yes                            | Clock, Crystal                         |

| Output:                        | Number of Circuits:                    |

| CMOS, HCSL, HSTL, LVDS         | -1                                     |

| Ratio - Input:Output:          | Differential - Input:Output:           |

| 3:11                           | Yes/Yes                                |

| Frequency - Max:               | Divider/Multiplier:                    |

| 1.25GHz                        | Yes/No                                 |

| Voltage - Supply:              | Operating Temperature:                 |

| 2.38V ~ 3.63V                  | -40°C ~ 85°C                           |

| Mounting Type:                 | Package / Case:                        |

| Surface Mount                  | 64-WFQFN Exposed Pad, CSP              |

| Supplier Device Package:       | Base Product Number:                   |

| 64-LFCSP (9x9)                 | AD9576                                 |

## **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 3 (168 Hours)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

## Dual PLL, Asynchronous Clock Generator

### **Data Sheet**

### FEATURES

Single, low phase noise, fully integrated VCO/fractional-N PLL core VCO range: 2375 MHz to 2725 MHz Integrated loop filter (requires a single external capacitor) 2 differential, XTAL, or single-ended reference inputs **Reference monitoring capability Automatic redundant XTAL switchover** Minimal transient, smooth switching **Typical RMS jitter** <0.3 ps (12 kHz to 20 MHz), integer-N translations <0.5 ps (12 kHz to 20 MHz), fractional-N translations Input frequency 8 kHz, 1.544 MHz, 2.048 MHz, and 10 MHz to 325 MHz Preset frequency translations via pin strapping (PPRx) Using a 25 MHz input reference 24.576 MHz, 25 MHz, 33.33 MHz, 50 MHz, 70.656 MHz, 100 MHz, 125 MHz, 148.5 MHz, 156.25 MHz, 161.1328 MHz, 312.5 MHz, 322.2656 MHz, 625 MHz, or 644.5313 MHz Using a 19.44 MHz input reference 50 MHz, 100 MHz, 125 MHz, 156.25 MHz, 161.1328 MHz, or 644.5313 MHz Using a 30.72 MHz input reference 25 MHz, 50 MHz, 100 MHz, 125 MHz, or 156.25 MHz Single, general-purpose, fully integrated VCO/integer-N PLL core VCO range: 750 MHz to 825 MHz **Integrated loop filter** Independent, duplicate reference input or operation from the fractional-N PLL active reference input Input frequency: 25 MHz Preset frequency translations via pin strapping (PPRx) 25 MHz, 33.33 MHz, 50 MHz, 66.67 MHz, 100 MHz, 133.33 MHz, 200 MHz, or 400 MHz Up to 3 copies of reference clock output 11 pairs of configurable differential outputs **Output drive formats** 3 outputs: HSTL, LVDS, HCSL, 1.8 V CMOS, 2.5 V/3.3 V CMOS 8 outputs: HSTL, LVDS, or 1.8 V CMOS 2.5 V or 3.3 V single-supply operation

### APPLICATIONS

Ethernet line cards, switches, and routers Baseband units SATA and PCI express Low jitter, low phase noise clock generation Asynchronous clock generation

Rev. A

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## AD9576

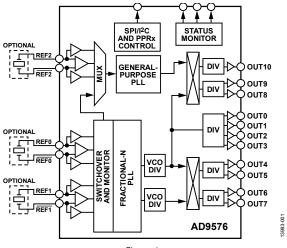

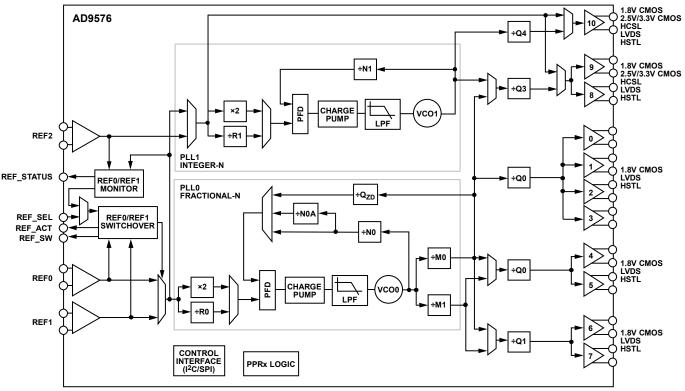

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

### **GENERAL DESCRIPTION**

The AD9576 provides a multiple output clock generator function comprising two dedicated phase-locked loop (PLL) cores with flexible frequency translation capability, optimized to serve as a robust source of asynchronous clocks for an entire system, providing extended operating life within frequency tolerance through monitoring of and automatic switchover between redundant crystal (XTAL) inputs with minimized switching, induced transients. The fractional-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize network performance, whereas the integer-N PLL provides general-purpose clocks for use as CPU and field-programmable gate array (FPGA) reference clocks.

The AD9576 uses pin strapping to select among a multitude of power-on ready configurations for its 11 output clocks, which require only the connection of external pull-up or pull-down resistors to the appropriate pin program reader pins (PPRx). These pins provide control of the internal dividers for establishing the desired frequency translations, clock output functionality, and input reference functionality. These parameters can also be manually configured through a serial port interface (SPI).

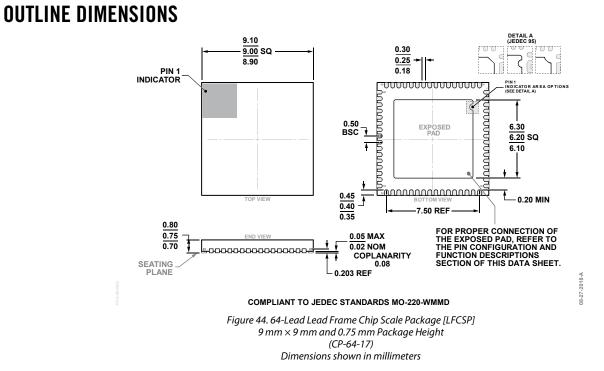

The AD9576 is packaged in a 64-lead, 9 mm  $\times$  9 mm LFCSP, requiring only a single 2.5 V or 3.3 V supply. The operating temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Each OUTx output is differential and contains two pins: OUTx and OUTx. For simplicity, the term OUTx refers to the functional output block containing these two pins.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016-2018 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| Features 1                                                                      |

|---------------------------------------------------------------------------------|

| Applications1                                                                   |

| Functional Block Diagram1                                                       |

| General Description1                                                            |

| Revision History                                                                |

| Specifications                                                                  |

| Conditions                                                                      |

| Supply Current Specifications                                                   |

| Power Dissipation Specifications5                                               |

| Reference Inputs 6                                                              |

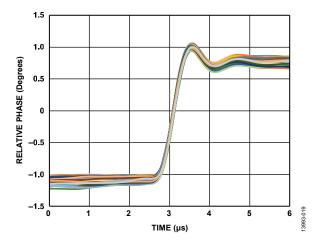

| Reference Switchover Output Disturbance Specifications 6                        |

| PLL0 Characteristics7                                                           |

| PLL1 Characteristics7                                                           |

| Clock Distribution Outputs Specifications7                                      |

| Output Alignment and Startup Specifications                                     |

| PLL0 Channels Absolute Clock Jitter Specifications                              |

| PLL1 and Bypass Channel Absolute Clock Jitter<br>Specifications                 |

| OUT8 to OUT10 Channel Cycle to Cycle Clock Jitter<br>Specifications13           |

| Logic Input Pins Characteristics—REF_SEL, RESET, SPx, PPRx                      |

| Status Output Pins Characteristics—LD_0, LD_1, REF_SW,<br>REF_STATUS, REF_ACT14 |

| Serial Control Port Specifications                                              |

| Absolute Maximum Ratings                                                        |

| Thermal Resistance                                                              |

| ESD Caution17                                                                   |

| Pin Configuration and Function Descriptions                                     |

| Typical Performance Characteristics                                             |

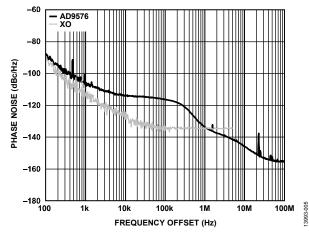

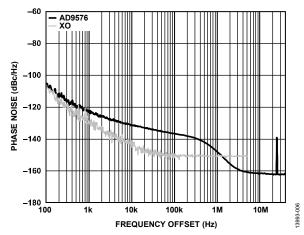

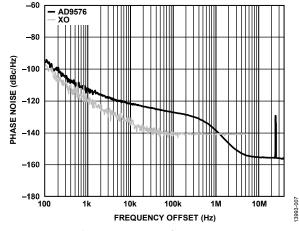

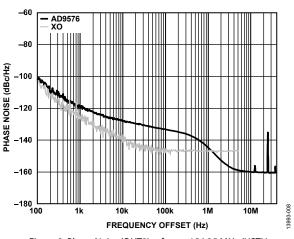

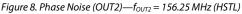

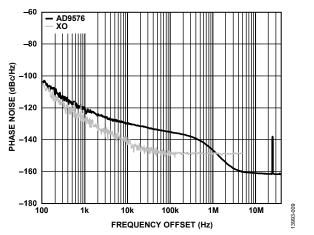

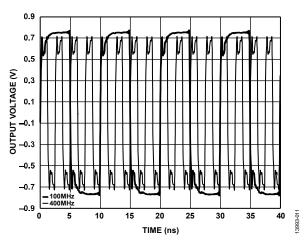

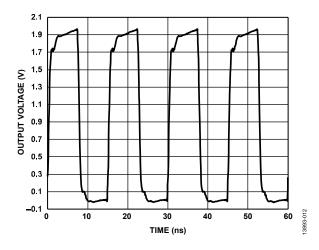

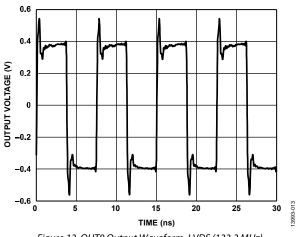

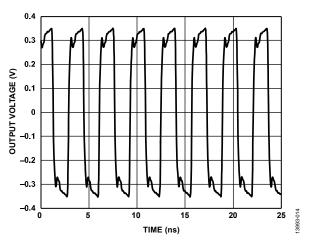

| Phase Noise and Voltage Waveforms                                               |

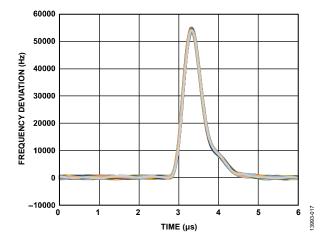

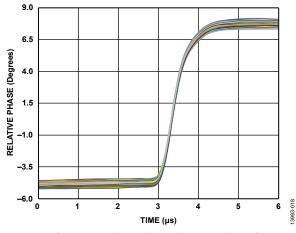

| Reference Switching Frequency and Phase Disturbance 24                          |

| Terminology                                                                     |

| Theory of Operation                                                             |

| Overview                                                                        |

| Reference Inputs                                                                |

| Reference Monitor                                                               |

| Reference Switching                                                             |

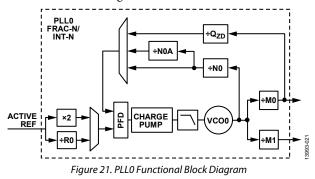

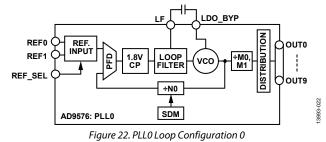

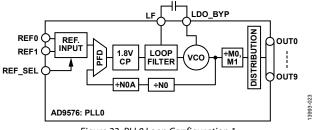

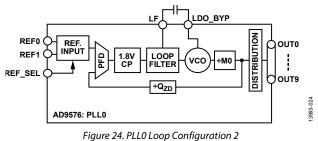

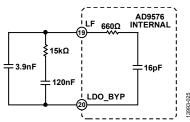

| PLL0 Integer-N/Fractional-N PLL                                              | . 29 |

|------------------------------------------------------------------------------|------|

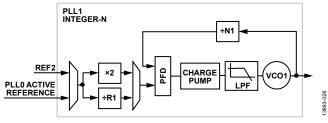

| PLL1 Integer-N PLL                                                           | . 35 |

| Output Distribution                                                          | . 36 |

| PPRx Pins                                                                    | . 38 |

| Power-On Reset (POR)                                                         | . 41 |

| Serial Control Port                                                          | . 42 |

| SPI/I <sup>2</sup> C Port Selection                                          | . 42 |

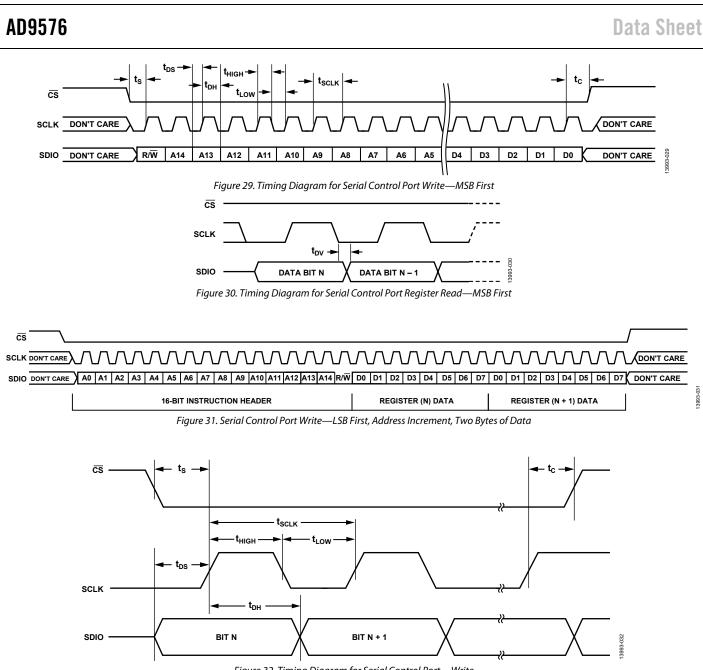

| SPI Serial Port Operation                                                    | . 42 |

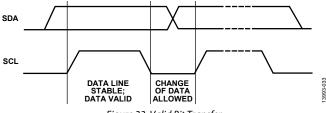

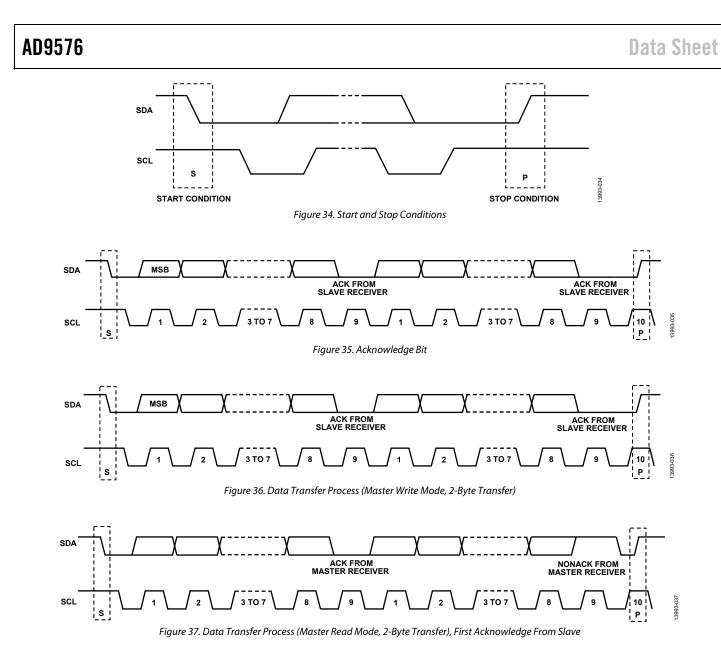

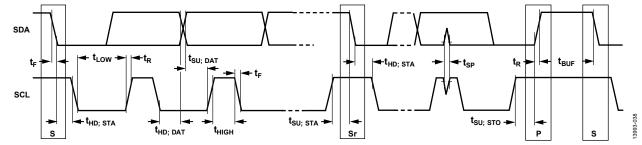

| I <sup>2</sup> C Serial Port Operation                                       | . 44 |

| Control Register Map                                                         | . 48 |

| Control Register Descriptions                                                | . 51 |

| Serial Port Configuration Registers (Register 0x000 to<br>Register 0x00F)    | . 51 |

| Status Indicator Registers (Register 0x020 to Register 0x021).               | . 52 |

| Chip Mode Register (Register 0x040)                                          | . 52 |

| Reference Input Configuration Registers (Register 0x080 t<br>Register 0x081) |      |

| Reference Switchover Registers (Register 0x082 to<br>Register 0x083)         | . 54 |

| PLL0 Configuration Registers (Register 0x100 to Register 0x111)              | 55   |

| PLL0 VCO Dividers Registers (Register 0x120 to Register 0x122)               | 57   |

| PLL0 Distribution Registers (Register 0x140 to Register 0x14D)               | . 58 |

| PLL1 Configuration Registers (Register 0x200 to Register 0x202)              | 60   |

| PLL1 Distribution Registers (Register 0x240 to Register 0x246)               | 60   |

| Applications Information                                                     | . 63 |

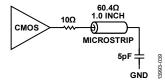

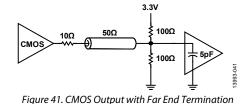

| Interfacing to CMOS Clock Outputs                                            | . 63 |

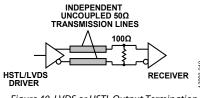

| Interfacing to LVDS and HSTL Clock Outputs                                   | . 63 |

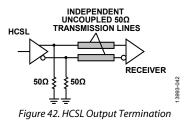

| Interfacing to HCSL Clock Outputs                                            | . 63 |

| Power Supply                                                                 | . 64 |

| Power and Grounding Considerations and Power Supply<br>Rejection             | 64   |

| Rejection<br>Outline Dimensions                                              |      |

|                                                                              |      |

| Ordering Guide                                                               | . 03 |

## **Data Sheet**

### **REVISION HISTORY**

7/2016—Revision 0: Initial Version

## **SPECIFICATIONS**

Typical values are given for  $V_{DD_x}$  = 2.5 V,  $T_A$  = 25°C, unless otherwise noted. Minimum and maximum values are given over the full  $V_{DD_x}$  and  $T_A$  (-40°C to +85°C) range.

VDD\_x and V<sub>DD\_x</sub> refer to the following pins, and to the voltage on any of the following pins, respectively: VDD\_REFMON, VDD\_REF0, VDD\_REF1, VDD\_IO, VDD\_PLL0, VDD\_VCO0, VDD\_M0, VDD\_M1, VDD\_OUT67, VDD\_OUT45, VDD\_OUT23, VDD\_OUT01, VDD\_OUT89, VDD\_OUT10, VDD\_VCO1, VDD\_PLL1, and VDD\_REF2.

Note that throughout this data sheet, multifunction pins, such as SCLK/SCL, are referred to either by the entire pin name or by a single function of the pin, for example, SCLK, when only that function is relevant.

### CONDITIONS

| Parameter                                       | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                                                |

|-------------------------------------------------|------|-----|------|------|-------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY<br>VOLTAGE<br>(V <sub>DD_x</sub> ) |      |     |      |      | Applies to all VDD_x pins; 2.5 V and 3.3 V nominal supplies are supported on all specifications, unless otherwise noted |

|                                                 | 2.38 |     | 2.63 | v    | $2.5 V \pm 5\%$                                                                                                         |

|                                                 | 2.97 |     | 3.63 | v    | $3.3 V \pm 10\%$                                                                                                        |

### SUPPLY CURRENT SPECIFICATIONS

#### Table 2.

| Parameter                                                                            | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------|-----|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLIES OTHER THAN CLOCK<br>OUTPUT DRIVERS                                          |     |      |      |      | All blocks running (excludes clock distribution section); REF0<br>(differential) and REF1 (differential) at 300 MHz; PLL0 locked at<br>2500 MHz with a 100 MHz phase frequency detector (PFD) rate;<br>Divider M0 set to 2 and Divider M1 disabled; REF2 (XTAL) at<br>25 MHz, configured as PLL1 input; PLL1 locked to 800 MHz with<br>input doubler enabled |

| VDD_REFMON and VDD_REFx<br>(Pin 4, Pin 9, Pin 10, and<br>Pin 64)                     |     | 35.6 | 39.2 | mA   | Cumulative current draw from all listed supply pins                                                                                                                                                                                                                                                                                                          |

| VDD_IO and VDD_PLL0 (Pin 16<br>and Pin 18)                                           |     | 26.5 | 29.5 | mA   | Cumulative current draw from all listed supply pins                                                                                                                                                                                                                                                                                                          |

| VDD_VCO0 (Pin 21)                                                                    |     | 33.8 | 36.9 | mA   |                                                                                                                                                                                                                                                                                                                                                              |

| VDD_Mx (Pin 23 and Pin 25)                                                           |     | 81.0 | 88.7 | mA   | Cumulative current draw from all listed supply pins                                                                                                                                                                                                                                                                                                          |

| VDD_VCO1 (Pin 60)                                                                    |     | 19.2 | 21.8 | mA   |                                                                                                                                                                                                                                                                                                                                                              |

| VDD_PLL1 (Pin 61)                                                                    |     | 20.4 | 23.7 | mA   |                                                                                                                                                                                                                                                                                                                                                              |

| SUPPLY CURRENT FOR EACH<br>CLOCK DISTRIBUTION SUPPLY<br>High Speed Transceiver Logic |     |      |      |      | Output driver supplies power both the output driver and output divider                                                                                                                                                                                                                                                                                       |

| (HSTL)                                                                               |     |      |      |      |                                                                                                                                                                                                                                                                                                                                                              |

| VDD_OUT67 (Pin 29)                                                                   |     | 59.8 | 69.7 | mA   | Output at 1250 MHz                                                                                                                                                                                                                                                                                                                                           |

| VDD_OUT45 (Pin 35)                                                                   |     | 59.8 | 69.7 | mA   | Output at 1250 MHz                                                                                                                                                                                                                                                                                                                                           |

| VDD_OUT23 (Pin 41)                                                                   |     | 46.7 | 53.8 | mA   | Output at 625 MHz                                                                                                                                                                                                                                                                                                                                            |

| VDD_OUT01(Pin 46)                                                                    |     | 36.4 | 42.6 | mA   | Output at 625 MHz                                                                                                                                                                                                                                                                                                                                            |

| VDD_OUT89 (Pin 52)                                                                   |     | 57.4 | 67.1 | mA   | Output at 400 MHz                                                                                                                                                                                                                                                                                                                                            |

| VDD_OUT10 (Pin 57)                                                                   |     | 34.2 | 39.5 | mA   | Output at 400 MHz                                                                                                                                                                                                                                                                                                                                            |

| Low Voltage Differential<br>Signaling (LVDS)                                         |     |      |      |      |                                                                                                                                                                                                                                                                                                                                                              |

| VDD_OUT67 (Pin 29)                                                                   |     | 41.3 | 49.2 | mA   | Output at 1250 MHz                                                                                                                                                                                                                                                                                                                                           |

| VDD_OUT45 (Pin 35)                                                                   |     | 41.3 | 49.2 | mA   | Output at 1250 MHz                                                                                                                                                                                                                                                                                                                                           |

| VDD_OUT23 (Pin 41)                                                                   |     | 31.1 | 34.9 | mA   | Output at 625 MHz                                                                                                                                                                                                                                                                                                                                            |

| VDD_OUT01(Pin 46)                                                                    |     | 20.8 | 23.6 | mA   | Output at 625 MHz                                                                                                                                                                                                                                                                                                                                            |

| VDD_OUT89 (Pin 52)                                                                   |     | 37.5 | 43.6 | mA   | Output at 400 MHz                                                                                                                                                                                                                                                                                                                                            |

| VDD_OUT10 (Pin 57)                                                                   |     | 24.1 | 27.7 | mA   | Output at 400 MHz                                                                                                                                                                                                                                                                                                                                            |

AD9576

| Parameter                                  | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                                |

|--------------------------------------------|-----|------|------|------|---------------------------------------------------------------------------------------------------------|

| 1.8 V CMOS                                 |     |      |      |      | All outputs at 100 MHz with a 10 pF load                                                                |

| VDD_OUT67 (Pin 29)                         |     | 27.2 | 34.7 | mA   |                                                                                                         |

| VDD_OUT45 (Pin 35)                         |     | 27.2 | 34.7 | mA   |                                                                                                         |

| VDD_OUT23 (Pin 41)                         |     | 28.2 | 31.7 | mA   |                                                                                                         |

| VDD_OUT01(Pin 46)                          |     | 17.4 | 21.9 | mA   |                                                                                                         |

| VDD_OUT89 (Pin 52)                         |     | 32.7 | 42.5 | mA   |                                                                                                         |

| VDD_OUT10 (Pin 57)                         |     | 21.4 | 26.8 | mA   |                                                                                                         |

| 2.5 V CMOS                                 |     |      |      |      | $V_{\text{DD}\_x}$ set to 2.5 V, output at 100 MHz with a 10 pF load; not available on OUT0 to OUT7     |

| VDD_OUT89 (Pin 52)                         |     | 38.5 | 48.8 | mA   |                                                                                                         |

| VDD_OUT10 (Pin 57)                         |     | 24.4 | 30.1 | mA   |                                                                                                         |

| 3.3 V CMOS                                 |     |      |      |      | $V_{\text{DD}\_x}$ set to 3.3 V, all outputs at 100 MHz with a 10 pF load; no available on OUT0 to OUT7 |

| VDD_OUT89 (Pin 52)                         |     | 48.5 | 60.4 | mA   |                                                                                                         |

| VDD_OUT10 (Pin 57)                         |     | 29.1 | 36.2 | mA   |                                                                                                         |

| High Speed Current Sinking<br>Logic (HCSL) |     |      |      |      | All outputs at 400 MHz; not available on OUT0 to OUT7                                                   |

| VDD_OUT89 (Pin 52)                         |     | 30.7 | 41.4 | mA   |                                                                                                         |

| VDD_OUT10 (Pin 57)                         |     | 20.8 | 26.6 | mA   |                                                                                                         |

### POWER DISSIPATION SPECIFICATIONS

Table 3.

| Parameter                        | Min | Тур  | Max   | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------|-----|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DISSIPATION                |     |      |       |      | All supplies set to 2.5 V nominal; specifications do not include power dissipated by external terminations                                                                                                                                                                                                                                                                                                                  |

| Typical Configuration 1          |     | 680  | 1168  | mW   | Asynchronous operation; PPR0 = State 0, PPR1 = State 0, PPR2 = State 3,<br>PPR3 = State 3; REF 0 and REF1 = 25 MHz XTAL, doubler enabled; OUT10 =<br>25 MHz CMOS; OUT0 to OUT3 = 100 MHz LVDS; OUT4 to OUT5 = 312.5 MHz<br>LVDS, OUT6 to OUT7 = 156.25 MHz LVDS, OUT8 to OUT9 = 125 MHz LVDS                                                                                                                                |

| Typical Configuration 2          |     | 619  | 974   | mW   | Synchronous operation; REF0 (differential) at 100 MHz, REF1 disabled, and REF2 (XTAL) at 25 MHz; PLL1 disabled and PLL0 locked at 2500 MHz using R divider of 2 and PLL0 feedback divider (N0) set to 50; M0 and M1 set to divide by 2; Output 0 set to 625 MHz HSTL; Output 1 to Output 3 disabled; Output 4 to Output 7 set to 125 MHz LVDS; Output 8 to Output 9 set to 156.25 MHz LVDS                                  |

| All Blocks Running               |     | 979  | 1520  | mW   | All blocks running; REF0 (differential) and REF1 (differential) at 300 MHz;<br>PLL0 locked at 2500 MHz with a 100 MHz PFD rate; M0 set to 2 and enabled to<br>Q0, Q1, and Q2; OUT0 to OUT3 = 625 MHz LVDS; OUT4 to OUT 7 = 1250 MHz<br>LVDS; REF2 (XTAL) at 25 MHz, configured as PLL1 input; PLL1 locked to<br>800 MHz with input doubler enabled; Divider Q3 and Divider Q4 set to 2 and<br>OUT8 to OUT10 = 400 MHz, HCSL |

| Minimal Power<br>Configuration   |     | 145  | 179   | mW   | PPR0 = State 0, PPR1 = State 0, PPR2 = State 0, PPR3 = State 0                                                                                                                                                                                                                                                                                                                                                              |

| INCREMENTAL POWER<br>DISSIPATION |     |      |       |      | Typical configuration; values show the change in power due to the indicated operation                                                                                                                                                                                                                                                                                                                                       |

| Input Reference On/Off           |     |      |       |      | Applies to one reference clock input at 25 MHz                                                                                                                                                                                                                                                                                                                                                                              |

| Single-Ended                     |     | 2.5  | 10    | mW   |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Differential                     |     | 27.5 | 33.7  | mW   |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output Driver On/Off             |     |      |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LVDS at 156.25 MHz               |     | 47.6 | 66.1  | mW   |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HSTL at 156.25 MHz               |     | 51.3 | 80.8  | mW   |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.8 V CMOS at<br>100 MHz         |     | 64.6 | 74.1  | mW   | A single 1.8 V CMOS output with a 10 pF load                                                                                                                                                                                                                                                                                                                                                                                |

| 2.5 V CMOS at<br>100 MHz         |     | 88.4 | 102.5 | mW   | A single 2.5 V CMOS output with a 10 pF load                                                                                                                                                                                                                                                                                                                                                                                |

### **REFERENCE INPUTS**

| Table 4. |  |

|----------|--|

|----------|--|

| Parameter                                        | Min   | Тур  | Max   | Unit   | Test Conditions/Comments                                                      |

|--------------------------------------------------|-------|------|-------|--------|-------------------------------------------------------------------------------|

| DIFFERENTIAL INPUT MODE                          |       |      |       |        |                                                                               |

| Input Frequency                                  |       |      | 325   | MHz    |                                                                               |

| Input Sensitivity                                | 100   |      |       | mV p-p |                                                                               |

| Minimum Input Slew Rate                          | 100   |      |       | V/µs   | Minimum limit imposed for jitter performance (when using a sinusoidal source) |

| Minimum Pulse Width                              | 1.38  |      |       | ns     | Applies to both low and high pulses                                           |

| Common-Mode Internally Generated<br>Bias Voltage |       | 1.24 |       | V      |                                                                               |

| Common-Mode Voltage Tolerance                    | 0.83  |      | 1.675 | V      | The acceptable common-mode range for a 200 mV p-p, dc-coupled input signal    |

| Differential Input Capacitance                   |       | 2    |       | pF     |                                                                               |

| Differential Input Resistance                    |       | 4.3  |       | kΩ     |                                                                               |

| SINGLE-ENDED INPUT CMOS MODE                     |       |      |       |        |                                                                               |

| Input Frequency                                  |       |      | 200   | MHz    |                                                                               |

| Minimum Pulse Width                              | 2     |      |       | ns     | Applies to both low and high pulses                                           |

| Hysteresis                                       |       | 240  |       | mV     |                                                                               |

| Input Leakage                                    |       | 2    |       | nA     |                                                                               |

| Input Capacitance                                |       | 2    |       | pF     |                                                                               |

| Input Voltage                                    |       |      |       |        |                                                                               |

| High                                             | 1.93  |      |       | V      |                                                                               |

| Low                                              |       |      | 1.04  | V      |                                                                               |

| CRYSTAL RESONATOR MODE                           |       |      |       |        | Fundamental mode quartz resonator                                             |

| Input Frequency                                  |       |      |       |        |                                                                               |

| Reference of PLL0 or Buffered<br>Output          | 19.44 |      | 30.72 | MHz    |                                                                               |

| Reference of PLL1                                |       | 25   |       | MHz    | REF2                                                                          |

| Effective Series Resistance (ESR)                |       |      | 80    | Ω      |                                                                               |

| Input Capacitance                                |       | 3    |       | рF     |                                                                               |

### **REFERENCE SWITCHOVER OUTPUT DISTURBANCE SPECIFICATIONS**

Table 5.

| Parameter                                                                     | Min | Тур | Max | Unit        | Test Conditions/Comments                                                                                                                         |

|-------------------------------------------------------------------------------|-----|-----|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| INSTANTANEOUS FREQUENCY (dθ/dt)<br>DISTURBANCE DUE TO REFERENCE<br>SWITCHOVER |     | 350 |     | ppm<br>peak | Applies only to PLL0 outputs; 1 ppm frequency offset<br>between the REF0 and REF1 channels; 400 kHz loop<br>bandwidth; smooth switchover enabled |

| INSTANTANEOUS PHASE DISTURBANCE<br>DUE TO REFERENCE SWITCHOVER                |     | 220 |     | ps          | Applies only to the active reference of PLL0; smooth switchover enabled                                                                          |

### PLL0 CHARACTERISTICS

| Parameter                                | Min  | Тур | Max  | Unit  | <b>Test Conditions/Comments</b> |

|------------------------------------------|------|-----|------|-------|---------------------------------|

| REFERENCE INPUT PATH                     |      |     |      |       |                                 |

| Input Frequency                          |      |     |      |       |                                 |

| Divider                                  |      |     | 325  | MHz   |                                 |

| Doubler                                  |      |     | 145  | MHz   |                                 |

| PHASE FREQUENCY DETECTOR (PFD)           |      |     |      |       |                                 |

| Frequency Range                          |      |     |      |       |                                 |

| Integer Mode                             |      |     | 290  | MHz   |                                 |

| Fractional Mode                          | 9.4  |     | 170  | MHz   |                                 |

| Lock Detect Window                       |      | ±16 |      | ppm   |                                 |

| INPUT FREQUENCY OF FEEDBACK DIVIDERS     |      |     |      |       |                                 |

| NO                                       |      |     | 2725 | MHz   |                                 |

| NOA                                      |      |     | 156  | MHz   |                                 |

| Q <sub>ZD</sub>                          |      |     | 1250 | MHz   |                                 |

| VOLTAGE CONTROLLED OSCILLATOR (VCO)      |      |     |      |       |                                 |

| Frequency Range                          | 2375 |     | 2725 | MHz   |                                 |

| Gain                                     |      | 64  |      | MHz/V |                                 |

| VCO DIVIDER (M0 AND M1) OUTPUT FREQUENCY |      |     | 1250 | MHz   |                                 |

### PLL1 CHARACTERISTICS

| Table 7.             |     |     |     |       |                          |

|----------------------|-----|-----|-----|-------|--------------------------|

| Parameter            | Min | Тур | Max | Unit  | Test Conditions/Comments |

| REFERENCE INPUT PATH |     |     |     |       |                          |

| Input Frequency      |     |     |     |       |                          |

| Divider              |     | 25  |     | MHz   |                          |

| Doubler              |     | 25  |     | MHz   |                          |

| PFD FREQUENCY        |     |     |     |       |                          |

| Frequency Range      | 25  |     | 50  | MHz   |                          |

| Lock Detector Window |     | 2   |     | UI    |                          |

| VCO                  |     |     |     |       |                          |

| Frequency Range      | 750 |     | 825 | MHz   |                          |

| Gain                 |     | 750 |     | MHz/V |                          |

### **CLOCK DISTRIBUTION OUTPUTS SPECIFICATIONS**

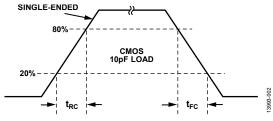

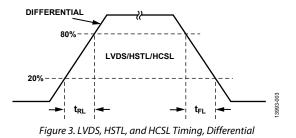

Rise and fall time measurement thresholds are 20% and 80% of the nominal low and high amplitude of the waveform.

| Parameter                         | Min | Тур  | Мах  | Unit | Test Conditions/Comments                               |

|-----------------------------------|-----|------|------|------|--------------------------------------------------------|

| HSTL (OUT0 TO OUT7)               |     |      |      |      | 100 $\Omega$ termination (differential)                |

| Output Frequency                  |     |      |      |      |                                                        |

| OUT0 to OUT3                      |     |      | 1000 | MHz  |                                                        |

| OUT4 to OUT7                      |     |      | 1250 | MHz  |                                                        |

| Output Rise Time, t <sub>RL</sub> | 108 | 136  | 163  | ps   | Measured differentially; output at 100 MHz             |

| Output Fall Time, t <sub>FL</sub> | 108 | 136  | 161  | ps   | Measured differentially; output at 100 MHz             |

| Duty Cycle                        | 45  |      | 55   | %    |                                                        |

| Differential Output Voltage Swing | 861 | 1080 | 1374 | mV   | Magnitude of voltage across pins; output driver static |

| Common-Mode Output Voltage        | 840 | 940  | 1034 | mV   | Output driver static                                   |

## Data Sheet

| Parameter                                                  | Min  | Тур   | Max      | Unit     | Test Conditions/Comments                                                 |

|------------------------------------------------------------|------|-------|----------|----------|--------------------------------------------------------------------------|

| LVDS (OUT0 TO OUT7)                                        |      |       |          |          | 100 $\Omega$ termination (differential)                                  |

| Output Frequency                                           |      |       |          |          |                                                                          |

| OUT0 to OUT3                                               |      |       | 1000     | MHz      |                                                                          |

| OUT4 to OUT7                                               |      |       | 1250     | MHz      |                                                                          |

| Output Rise Time, t <sub>RL</sub>                          | 139  | 158   | 181      | ps       | Measured differentially; output at 100 MHz                               |

| Output Fall Time, t <sub>FL</sub>                          | 141  | 159   | 181      | ps       | Measured differentially; output at 100 MHz                               |

| Duty Cycle                                                 | 45   |       | 55       | %        | ·····                                                                    |

| Differential Output Voltage, VoD                           | 276  | 375   | 490      | mV       | Magnitude of voltage across pins; output driver static                   |

| Delta V <sub>OD</sub>                                      |      |       | 22       | mV       | diverstatic                                                              |

| Output Offset Voltage, Vos                                 | 1.18 | 1.275 | 1.36     | V        |                                                                          |

| Delta V <sub>os</sub>                                      | 1.10 | 1.275 | 26       |          |                                                                          |

| Short-Circuit Current (I <sub>SA</sub> , I <sub>SB</sub> ) |      |       | 26<br>25 | mV<br>mA | Output shorted to GND; value represents the                              |

|                                                            | _    |       |          |          | magnitude of current draw                                                |

| 1.8 V CMOS (OUT0 TO OUT7)                                  |      |       |          |          | $C_{LOAD} = 10 \text{ pF}$                                               |

| Output Frequency                                           |      |       | 200      | MHz      |                                                                          |

| Output Rise Time, t <sub>RC</sub>                          | 0.84 | 1.19  | 1.54     | ns       | Output at 25 MHz                                                         |

| Output Fall Time, t <sub>FC</sub>                          | 1.04 | 1.25  | 1.49     | ns       | Output at 25 MHz                                                         |

| Duty Cycle                                                 | 45   |       | 55       | %        |                                                                          |

| Output Voltage                                             |      |       |          |          |                                                                          |

| High (V <sub>он</sub> )                                    | 1.74 |       |          | V        | $I_{LOAD} = -1 \text{ mA}$                                               |

| Low (V <sub>OL</sub> )                                     |      |       | 0.065    | V        | $I_{LOAD} = 1 \text{ mA}$                                                |

| HSTL (OUT8 TO OUT10)                                       |      |       |          |          | 100 $\Omega$ termination (differential)                                  |

| Output Frequency                                           |      |       | 1000     | MHz      |                                                                          |

| Output Rise Time, t <sub>RL</sub>                          | 124  | 144   | 170      | ps       | Measured differentially; output at 100 MHz                               |

| Output Fall Time, t <sub>FL</sub>                          | 125  | 144   | 170      | ps       | Measured differentially; output at 100 MHz                               |

| Duty Cycle                                                 | 45   |       | 55       | %        | Assumes 50% reference input duty cycle                                   |

| Differential Output Voltage Swing                          | 861  | 1080  | 1374     | mV       | Magnitude of voltage across pins; output driver static                   |

| Common-Mode Output Voltage                                 | 840  | 940   | 1034     | mV       | Output driver static                                                     |

| LVDS (OUT8 TO OUT10)                                       |      |       |          |          | $100 \Omega$ termination (differential)                                  |

| Output Frequency                                           |      |       | 1000     | MHz      |                                                                          |

| Output Rise Time, t <sub>RL</sub>                          | 65   | 85    | 112      | ps       | Measured differentially; output at 100 MHz                               |

| Output Fall Time, t <sub>FL</sub>                          | 66   | 86    | 112      | ps       | Measured differentially; output at 100 MHz                               |

| Duty Cycle                                                 | 45   | 80    | 55       | μs<br>%  | Assumes 50% reference input duty cycle                                   |

| Differential Output Voltage, Vod                           | 276  | 375   |          |          |                                                                          |

|                                                            | 270  | 575   | 490      | mV       | Magnitude of voltage across pins; output driver static                   |

| $\Delta V_{OD}$                                            | 1    |       | 22       | mV       |                                                                          |

| Output Offset Voltage, Vos                                 | 1.18 | 1.275 | 1.36     | V        |                                                                          |

| ΔVos                                                       |      |       | 26       | mV       |                                                                          |

| Short-Circuit Current (I <sub>SA</sub> , I <sub>SB</sub> ) |      |       | 25       | mA       | Output shorted to GND; value represents the<br>magnitude of current draw |

| 1.8 V CMOS (OUT8 TO OUT10)                                 |      |       |          |          | $C_{LOAD} = 10 \text{ pF}$                                               |

| Output Frequency                                           |      |       | 200      | MHz      |                                                                          |

| Output Rise Time, t <sub>RC</sub>                          | 1    | 0.49  | 1.41     | ns       | Output at 25 MHz                                                         |

| Output Fall Time, t <sub>FC</sub>                          |      | 0.59  | 1.24     | ns       | Output at 25 MHz                                                         |

| Duty Cycle                                                 | 45   |       | 55       | %        | Assumes 50% reference input duty cycle                                   |

| Output Voltage                                             |      |       | -        |          |                                                                          |

| High (V <sub>он</sub> )                                    | 1.74 |       |          | v        | $I_{LOAD} = -1 \text{ mA}$                                               |

| Low (V <sub>oL</sub> )                                     |      |       | 0.065    | v        | $I_{\text{LOAD}} = 1 \text{ mA}$                                         |

|                                                            |      |       | 0.005    | v        |                                                                          |

## AD9576

| Parameter                         | Min                     | Тур  | Max  | Unit | Test Conditions/Comments                               |

|-----------------------------------|-------------------------|------|------|------|--------------------------------------------------------|

| FULL SWING CMOS (OUT8 TO OUT10)   |                         |      |      |      | $C_{LOAD} = 10 \text{ pF}$                             |

| Output Frequency                  |                         |      | 250  | MHz  |                                                        |

| Output Rise Time, t <sub>RC</sub> |                         | 0.50 | 1.38 | ns   | Output at 25 MHz                                       |

| Output Fall Time, t <sub>FC</sub> |                         | 0.57 | 1.19 | ns   | Output at 25 MHz                                       |

| Duty Cycle                        | 45                      |      | 55   | %    | Assumes 50% reference input duty cycle                 |

| Output Voltage                    |                         |      |      |      |                                                        |

| High (V <sub>он</sub> )           | V <sub>DD_x</sub> - 0.3 | 3    |      | V    | $I_{LOAD} = -10 \text{ mA}$                            |

| Low (V <sub>OL</sub> )            |                         |      | 0.25 | V    | $I_{LOAD} = 10 \text{ mA}$                             |

| HCSL (OUT8 to OUT10)              |                         |      |      |      | 50 $\Omega$ from each output pin to GND                |

| Output Frequency                  |                         |      | 800  |      |                                                        |

| Output Rise Time, t <sub>RL</sub> | 145                     | 174  | 211  | ps   | Measured differentially; output at 100 MHz             |

| Output Fall Time, t <sub>FL</sub> | 141                     | 175  | 209  | ps   | Measured differentially; output at 100 MHz             |

| Duty Cycle                        | 45                      |      | 55   | %    | Assumes 50% reference input duty cycle                 |

| Differential Output Voltage Swing | 570                     | 770  | 975  | mV   | Magnitude of voltage across pins; output driver static |

| Common-Mode Output Voltage        | 295                     | 400  | 500  | mV   | Output driver static                                   |

### Timing Diagrams

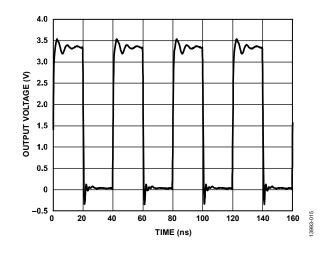

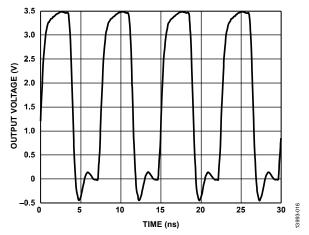

Figure 2. CMOS Timing, Single-Ended, 10 pF Load

### **OUTPUT ALIGNMENT AND STARTUP SPECIFICATIONS**

The indicated times assume the voltage applied to all power supply pins is within specification and stable.

| Table 9.                                                  |      |      |      |      |                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------|------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                 | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                                                                 |

| ZERO DELAY                                                |      |      |      |      | Timing delay between input clock edge on REF0 or REF1 to any corresponding OUTx clock edge; R divider and doubler are bypassed                                                                                                                           |

| OUT0 to OUT7                                              |      | 3.44 | 3.87 | ns   |                                                                                                                                                                                                                                                          |

| OUT8 to OUT9                                              |      | 3.82 | 4.28 | ns   |                                                                                                                                                                                                                                                          |

| OUTPUT TO OUTPUT SKEW                                     |      |      |      |      | Deviation between rising edges of outputs of a similar logic type; frequency source to distribution is the output of the M0 divider; all output drivers are configured to the same logic type, unless otherwise noted; all output frequencies are 25 MHz |

| Between Outputs that<br>Share a Single Qx Divider<br>LVDS |      |      |      |      |                                                                                                                                                                                                                                                          |

| OUT1, OUT2, and<br>OUT3                                   | -36  |      | +29  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| OUT5                                                      | -13  |      | +30  | ps   | Relative to OUT4                                                                                                                                                                                                                                         |

| OUT7                                                      | -19  |      | +15  | ps   | Relative to OUT6                                                                                                                                                                                                                                         |

| OUT9                                                      | -22  |      | +20  | ps   | Relative to OUT8                                                                                                                                                                                                                                         |

| HSTL                                                      |      |      |      |      |                                                                                                                                                                                                                                                          |

| OUT1, OUT2, and<br>OUT3                                   | -33  |      | +30  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| OUT5                                                      | -16  |      | +37  | ps   | Relative to OUT4                                                                                                                                                                                                                                         |

| OUT7                                                      | -16  |      | +19  | ps   | Relative to OUT6                                                                                                                                                                                                                                         |

| OUT9                                                      | -23  |      | +24  | ps   | Relative to OUT8                                                                                                                                                                                                                                         |

| Between OUT0 to OUT9                                      |      |      |      |      |                                                                                                                                                                                                                                                          |

| LVDS                                                      |      |      |      |      |                                                                                                                                                                                                                                                          |

| OUT4                                                      | -141 |      | -8   | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| OUT6                                                      | -105 |      | +23  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| OUT8                                                      | 229  |      | 440  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| HSTL                                                      |      |      |      |      |                                                                                                                                                                                                                                                          |

| OUT4                                                      | -149 |      | -12  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| OUT6                                                      | -116 |      | +17  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| OUT8                                                      | 271  |      | 487  | ps   | Relative to OUT0                                                                                                                                                                                                                                         |

| PROPAGATION DELAY                                         |      | 3.88 | 4.47 | ns   | Rising edge on REF2 input to OUT8 to OUT10; 25 MHz reference input clock, PLL1 bypassed, and Qx dividers set to 1                                                                                                                                        |

| OUTPUT READY TIME                                         |      |      |      |      | 25 MHz reference input clocks, input doublers disabled                                                                                                                                                                                                   |

| PLLO                                                      |      | 8    |      | ms   | Time interval from RESET pin = Logic 1 to LD_0 pin = Logic 1 (PLL0 lock detection)                                                                                                                                                                       |

| PLL1                                                      |      | 455  |      | μs   | Time interval from RESET pin = Logic 1 to LD_1 pin = Logic 1 (PLL1 lock detection)                                                                                                                                                                       |

### PLL0 CHANNELS ABSOLUTE CLOCK JITTER SPECIFICATIONS

Reference input frequency source is a 25 MHz Taitien XTAL, and frequency multiplier (×2) at PLL input enabled, unless otherwise noted.

| Րable 10.<br>Parameter                                              | Min | Тур   | Мах | Unit | Test Conditions/Comments |

|---------------------------------------------------------------------|-----|-------|-----|------|--------------------------|

| HSTL INTEGRATED RMS JITTER                                          |     | .76   | max | •    |                          |

| Jitter Integration Bandwidth = $10 \text{ kHz}$ to $10 \text{ MHz}$ |     |       |     |      |                          |

| Integer-N Translations                                              |     |       |     |      |                          |

| 100 MHz Output                                                      |     | 0.233 |     | ps   |                          |

| 125 MHz Output                                                      |     | 0.218 |     | ps   |                          |

| 156.25 MHz Output                                                   |     | 0.218 |     | ps   |                          |

| 625 MHz Output                                                      |     | 0.210 |     | -    |                          |

| Fractional-N Translations                                           |     | 0.221 |     | ps   |                          |

| 70.656 MHz Output                                                   |     | 0.291 |     | nc   |                          |

| •                                                                   |     | 0.291 |     | ps   |                          |

| 148.5 MHz Output                                                    |     | 0.292 |     | ps   |                          |

| 153.6 MHz Output                                                    |     |       |     | ps   |                          |

| 644.53125 MHz Output                                                |     | 0.313 |     | ps   |                          |

| Jitter Integration Bandwidth = 12 kHz to 20 MHz                     |     |       |     |      |                          |

| Integer-N Translations                                              |     |       |     |      |                          |

| 100 MHz Output                                                      |     | 0.239 |     | ps   |                          |

| 125 MHz Output                                                      |     | 0.222 |     | ps   |                          |

| 156.25 MHz Output                                                   |     | 0.221 |     | ps   |                          |

| 625 MHz Output                                                      |     | 0.222 |     | ps   |                          |

| Fractional-N Translations                                           |     |       |     |      |                          |

| 70.656 MHz Output                                                   |     | 0.298 |     | ps   |                          |

| 148.5 MHz Output                                                    |     | 0.310 |     | ps   |                          |

| 153.6 MHz Output                                                    |     | 0.296 |     | ps   |                          |

| 644.53125 MHz Output                                                |     | 0.314 |     | ps   |                          |

| Jitter Integration Bandwidth = 50 kHz to 80 MHz                     |     |       |     |      |                          |

| 312.5 MHz Output                                                    |     | 0.237 |     | ps   |                          |

| Jitter Integration Bandwidth = 1.875 MHz to 20 MHz                  |     |       |     |      |                          |

| Integer-N Translations                                              |     |       |     |      |                          |

| 100 MHz Output                                                      |     | 0.088 |     | ps   |                          |

| 125 MHz Output                                                      |     | 0.076 |     | ps   |                          |

| 156.25 MHz Output                                                   |     | 0.071 |     | ps   |                          |

| 625 MHz Output                                                      |     | 0.053 |     | ps   |                          |

| Fractional-N Translations                                           |     |       |     |      |                          |

| 70.656 MHz Output                                                   |     | 0.119 |     | ps   |                          |

| 148.5 MHz Output                                                    |     | 0.106 |     | ps   |                          |

| 153.6 MHz Output                                                    |     | 0.103 |     | ps   |                          |

| 644.53125 MHz Output                                                |     | 0.096 |     | ps   |                          |

| VDS INTEGRATED RMS JITTER                                           |     |       |     |      |                          |

| Jitter Integration Bandwidth = 10 kHz to 10 MHz                     |     |       |     |      |                          |

| Integer-N Translations                                              |     |       |     |      |                          |

| 100 MHz Output                                                      |     | 0.242 |     | ps   |                          |

| 125 MHz Output                                                      |     | 0.227 |     | ps   |                          |

| 156.25 MHz Output                                                   |     | 0.250 |     | ps   |                          |

| 625 MHz Output                                                      |     | 0.221 |     | ps   |                          |

| Fractional-N Translations                                           |     | 0.221 |     | 22   |                          |

| 70.656 MHz Output                                                   |     | 0.351 |     | nç   |                          |

| •                                                                   |     |       |     | ps   |                          |

| 148.5 MHz Output<br>153.6 MHz Output                                |     | 0.329 |     | ps   |                          |

|                                                                     | 1   | 0.327 |     | ps   |                          |

| Parameter                                          | Min | Тур   | Мах | Unit | <b>Test Conditions/Comments</b> |

|----------------------------------------------------|-----|-------|-----|------|---------------------------------|

| Jitter Integration Bandwidth = 12 kHz to 20 MHz    |     |       |     |      |                                 |

| Integer-N Translations                             |     |       |     |      |                                 |

| 100 MHz Output                                     |     | 0.268 |     | ps   |                                 |

| 125 MHz Output                                     |     | 0.240 |     | ps   |                                 |

| 156.25 MHz Output                                  |     | 0.257 |     | ps   |                                 |

| 625 MHz Output                                     |     | 0.221 |     | ps   |                                 |

| Fractional-N Translations                          |     |       |     |      |                                 |

| 70.656 MHz Output                                  |     | 0.412 |     | ps   |                                 |

| 148.5 MHz Output                                   |     | 0.336 |     | ps   |                                 |

| 153.6 MHz Output                                   |     | 0.334 |     | ps   |                                 |

| 644.53125 MHz Output                               |     | 0.314 |     | ps   |                                 |

| Jitter Integration Bandwidth = 50 kHz to 80 MHz    |     |       |     |      |                                 |

| 312.5 MHz Output                                   |     | 0.246 |     | ps   |                                 |

| Jitter Integration Bandwidth = 1.875 MHz to 20 MHz |     |       |     |      |                                 |

| Integer-N Translations                             |     |       |     |      |                                 |

| 100 MHz Output                                     |     | 0.161 |     | ps   |                                 |