# ADA4830-2BCPZ-R7 Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number ADA4830-2BCPZ-R7-DG

Manufacturer Analog Devices Inc.

Manufacturer Product Number ADA4830-2BCPZ-R7

Description IC OPAMP DIFF 2 CIRCUIT 16LFCSP

Detailed Description Differential Amplifier 2 Circuit 16-LFCSP (3x3)

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

## **Purchase and inquiry**

| Manufacturer Product Number: | Manufacturer:                |

|------------------------------|------------------------------|

| ADA4830-2BCPZ-R7             | Analog Devices Inc.          |

| Series:                      | Product Status:              |

|                              | Active                       |

| Amplifier Type:              | Number of Circuits:          |

| Differential                 | 2                            |

| Output Type:                 | Slew Rate:                   |

|                              | 250V/µs                      |

| -3db Bandwidth:              | Current - Supply:            |

| 84 MHz                       | 6.8mA (x2 Channels)          |

| Current - Output / Channel:  | Voltage - Supply Span (Min): |

| 125 mA                       | 2.9 V                        |

| Voltage - Supply Span (Max): | Operating Temperature:       |

| 5.5 V                        | -40°C ~ 125°C                |

| Mounting Type:               | Package / Case:              |

| Surface Mount                | 16-WFQFN Exposed Pad, CSP    |

| Supplier Device Package:     | Base Product Number:         |

| 16-LFCSP (3x3)               | ADA4830                      |

|                              |                              |

## **Environmental & Export classification**

8542.33.0001

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 3 (168 Hours)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

# ANALOG High Speed Difference Amplifier with Input Short-to-Battory Protections **Short-to-Battery Protection**

**Data Sheet**

ADA4830-1/ADA4830-2

#### **FEATURES**

Input overvoltage (short-to-battery) protection of up to 18 V Short-to-battery output flag for wire diagnostics Wide input common-mode range with single 5 V supply High performance video amplifier with 0.50 V/V gain

-3 dB bandwidth of 84 MHz 250 V/us slew rate (2 V step) **Excellent video specifications** 0.1 dB flatness to 28 MHz

SNR of 73 dB to 15 MHz

Differential gain/phase of 0.1%/0.1°

Wide supply range: 2.9 V to 5.5 V **Enable/output disable mode** Space saving 3 mm × 3 mm LFCSP package

Wide operating temperature range: -40°C to +125°C

**Qualified for automotive applications**

#### **APPLICATIONS**

**Automotive vision systems Automotive infotainment** Surveillance systems

#### **GENERAL DESCRIPTION**

The ADA4830-1 (single) and ADA4830-2 (dual) are monolithic, high speed difference amplifiers that integrate input overvoltage (short-to-battery) protection of up to 18 V with a wide input common-mode voltage range and excellent ESD robustness. They are intended for use as receivers for differential or pseudo differential CVBS and other high speed video signals in harsh, noisy environments such as automotive infotainment and vision systems. The ADA4830-1 and ADA4830-2 combine high speed and precision, which allows for accurate reproduction of CVBS video signals, yet rejects unwanted common-mode error voltages.

The short-to-battery protection that is integrated into the ADA4830-1 and ADA4830-2 employs fast switching circuitry to clamp and hold internal voltage nodes at a safe level when an input overvoltage condition is detected. This protection allows the inputs of the ADA4830-1 and ADA4830-2 to be directly connected to a remote video source, such as a rearview camera, without the need for large expensive series capacitors. The ADA4830-1 and ADA4830-2 can withstand direct short-to-battery voltages as high as 18 V on their input pins.

The ADA4830-1 and ADA4830-2 are designed to operate at supply voltages as low as 2.9 V and as high as 5.5 V, using only 6.8 mA of supply current per channel. These devices provide true singlesupply capability, allowing the input signal to extend 8.5 V

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

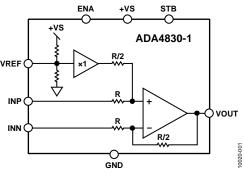

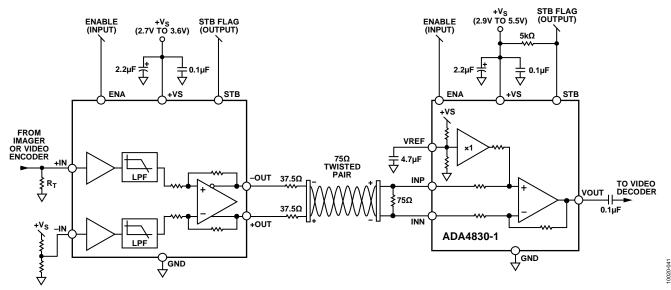

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1. FNA1 +VS1 STB1 ADA4830-2 VREF INP VOUT1 INN<sub>1</sub> R/2 GND1 GND<sub>2</sub> -^^ R/2 INN2 VOUT2 INP2 +VS VREF2 ENA2 STB2 Figure 2.

below ground rail and to 8.5 V above ground on a single 5 V supply. At the output, the amplifier can swing to within 250 mV of either supply rail into a 150  $\Omega$  load.

The ADA4830-1 and ADA4830-2 present a gain of 0.50 V/V at their output. This is designed to keep the video signal within the allowed range of the video decoder, which is typically 1 V p-p or less.

The ADA4830-1W and ADA4830-2W are automotive grade version, qualified for automotive applications. See the Automotive Products section for more details.

The ADA4830-1 and ADA4830-2 are available in  $3 \text{ mm} \times 3 \text{ mm}$ LFCSP packages, 8-lead and 16-lead, respectively, and are specified for operation over the automotive temperature range of -40°C to +125°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. www.analog.com Tel: 781.329.4700 Fax: 781.461.3113 ©2011–2012 Analog Devices, Inc. All rights reserved.

**TABLE OF CONTENTS**

# **Data Sheet**

| Features                                                               | Power Supply Pins (ADA4830-2)13                            |

|------------------------------------------------------------------------|------------------------------------------------------------|

| Applications                                                           | Applications Information                                   |

| General Description                                                    | Methods of Transmission14                                  |

| Functional Block Diagram                                               | Voltage Reference (VREF Pin)14                             |

| Revision History                                                       |                                                            |

| Specifications                                                         |                                                            |

| 5 V Operation                                                          |                                                            |

| 3.3 V Operation                                                        |                                                            |

| -                                                                      | •                                                          |

| Absolute Maximum Ratings                                               | -                                                          |

| Thermal Resistance                                                     | Using the ADA4830-2 as a Low Cost Video Switch 16          |

| Maximum Power Dissipation                                              | Driving Capacitive Loads                                   |

| ESD Caution                                                            | Typical Applications Circuits                              |

| Pin Configurations and Function Descriptions                           | Fully DC-Coupled Transmission Line                         |

| Typical Performance Characteristics                                    | Packaging and Ordering Information                         |

| Theory of Operation                                                    |                                                            |

| Core Amplifier                                                         |                                                            |

| -                                                                      | C                                                          |

| Overvoltage (Short-to-Battery) Protection                              |                                                            |

| Short-to-Battery Output Flag                                           |                                                            |

| ESD Protection                                                         | 3                                                          |

|                                                                        |                                                            |

| REVISION HISTORY                                                       |                                                            |

| 6/12—Rev. B to Rev. C                                                  | Added Figure 5 and Table 6                                 |

| Added ADA4830-2W                                                       | 0 71                                                       |

| Changes to Features                                                    |                                                            |

| Changes to Ordering Guide                                              | Added Figure 24 to Figure 29                               |

| 4/12—Rev. A to Rev. B                                                  | Termination) Section, Fully Differential Mode Section, and |

| Changes to Features Section and Generation Description Section.        |                                                            |

| Changes to Table 1                                                     |                                                            |

| Changes to Table 2                                                     | č .                                                        |

| Changes to Table 4                                                     | , 1                                                        |

| Changes to Figure 28                                                   | · ·                                                        |

| Changes to Figure 28 Changes to ESD Protection Section                 |                                                            |

| Changes to Ordering Guide                                              |                                                            |

| Added Automotive Products Section                                      |                                                            |

| Added Automotive Froducts Section                                      | Added Fully DC-Coupled Transmission Line Section 19        |

| 1/12—Rev. 0 to Rev. A                                                  | Changes to Figure 42                                       |

| Added ADA4830-2                                                        |                                                            |

| Changes to Features Section and Figure 1                               | 1                                                          |

| Added Figure 2; Renumbered Sequentially                                | · · · · · · · · · · · · · · · · · · ·                      |

| Changes to Table 1                                                     |                                                            |

| · ·                                                                    |                                                            |

| Changes to Table 2                                                     | ī                                                          |

| Added Supply Voltage Delta Parameter, Table 3; Renumbered Sequentially |                                                            |

| ocquericially                                                          | ,                                                          |

ADA4830-1/ADA4830-2

### **SPECIFICATIONS**

### **5 V OPERATION**

$T_{A}=25^{\circ}C\text{, }+V_{S}=5\text{ V}\text{, }R_{L}=1\text{ k}\Omega\text{, }V_{REF}=2.5\text{ V}\text{ (floating), }V_{INCM}=+V_{S}/2\text{, }R_{STB}=5\text{ k}\Omega\text{ to }+V_{S}\text{, unless otherwise specified.}$

Table 1.

| Parameter                                     | Test Conditions/Comments                                              | Min     | Тур        | Max  | Unit    |

|-----------------------------------------------|-----------------------------------------------------------------------|---------|------------|------|---------|

| DYNAMIC PERFORMANCE                           |                                                                       |         |            |      |         |

| –3 dB Large Signal Bandwidth                  | $V_{OUT} = 0.5 \text{ V p-p, R}_{L} = 150 \Omega$                     | 64      | 71         |      | MHz     |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 56      |            |      | MHz     |

|                                               | $V_{OUT} = 0.1 \text{ V p-p, } R_L = 1 \text{ k}\Omega$               |         | 84         |      | MHz     |

|                                               | $V_{OUT} = 0.1 \text{ V p-p, } R_L = 150 \Omega$                      | 65      | 74         |      | MHz     |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 60      |            |      | MHz     |

| Bandwidth for 0.1 dB Flatness                 | $V_{OUT} = 0.5 \text{ V p-p, R}_{L} = 150 \Omega$                     |         | 28         |      | MHz     |

| Slew Rate (t <sub>R</sub> /t <sub>F</sub> )   | V <sub>OUT</sub> = 2 V step                                           | 196/200 | 250/300    |      | V/µs    |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 164/220 |            |      | V/µs    |

| Settling Time to 0.1%                         | V <sub>OUT</sub> = 2 V step                                           |         | 25         |      | ns      |

| NOISE/DISTORTION PERFORMANCE                  |                                                                       |         |            |      |         |

| Output Voltage Noise                          | f = 1 MHz                                                             |         | 28         |      | nV/√Hz  |

| Differential Gain Error (NTSC)                | $R_L = 150 \Omega, V_{IN} = 1 V p-p$                                  |         | 0.1        |      | %       |

| Differential Phase Error (NTSC)               | $R_L = 150 \Omega, V_{IN} = 1 V p-p$                                  |         | 0.1        |      | Degrees |

| Signal-to-Noise Ratio                         | $f = 100 \text{ kHz to } 15 \text{ MHz}, V_{OUT} = 0.5 \text{ V p-p}$ |         | 73         |      | dB      |

| DC PERFORMANCE                                |                                                                       |         |            |      |         |

| Nominal Gain                                  | V <sub>IN</sub> to V <sub>OUT</sub>                                   | 0.49    | 0.50       | 0.51 | V/V     |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 0.49    |            | 0.51 | V/V     |

| Output Bias Voltage                           |                                                                       | 2.45    | 2.50       | 2.55 | V       |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 2.44    |            | 2.56 | V       |

| INPUT CHARACTERISTICS                         |                                                                       |         |            |      |         |

| Input Resistance (Differential Mode)          |                                                                       |         | 6.7        |      | kΩ      |

| Input Resistance (Common Mode)                |                                                                       |         | 2          |      | kΩ      |

| Input Common-Mode Voltage Range               | V <sub>REF</sub> voltage adjusted to optimized range                  | -10     |            | +9.5 | V       |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | -10     |            | +9.5 | V       |

| Common-Mode Rejection (CMR)                   | $V_{IN} = \pm 5 V$                                                    | 42      | 65         |      | dB      |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 42      |            |      | dB      |

| SHORT-TO-BATTERY CHARACTERISTICS              |                                                                       |         |            |      |         |

| Input Current                                 | $V_{IN} = 18 V$ (short-to-battery)                                    |         | 4.1        |      | mA      |

| Protected Input Voltage Range                 |                                                                       | -9      |            | +20  | V       |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | -9      |            | +20  | V       |

| Short-to-Battery Output Flag Trigger<br>Level | Minimum V <sub>IN</sub> needed to signal an input fault condition     | 9.8     | 10.3       | 10.8 | V       |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>       | 9.8     |            | 10.8 | V       |

| VOLTAGE REFERENCE INPUT                       |                                                                       |         |            |      |         |

| Input Voltage Range                           |                                                                       |         | 0.2 to 3.9 |      | V       |

| Input Resistance                              |                                                                       |         | 20         |      | kΩ      |

| Gain                                          | V <sub>REF</sub> to V <sub>OUT</sub>                                  |         | 1          |      | V/V     |

| LOGIC OUTPUT/INPUT CHARACTERISTICS            |                                                                       |         |            |      |         |

| STB V <sub>OH</sub>                           | $V_{IN} \le 9.8  V$ (normal operation)                                |         | 5.0        |      | V       |

| STB V <sub>OL</sub>                           | V <sub>IN</sub> ≥ 10.8 V (fault condition), ADA4830-1/ADA4830-2       |         | 110/253    |      | mV      |

| ENA V <sub>IH</sub>                           | Voltage to enable device                                              |         | ≥3.0       |      | V       |

| ENA V <sub>IL</sub>                           | Voltage to disable device                                             |         | ≤1.0       |      | V       |

**Data Sheet**

| Parameter                           | Test Conditions/Comments                                           | Min | Тур          | Max  | Unit |

|-------------------------------------|--------------------------------------------------------------------|-----|--------------|------|------|

| OUTPUT CHARACTERISTICS              |                                                                    |     |              |      |      |

| Output Voltage Swing                | $R_L = 150 \Omega$ to ground                                       |     | 0.01 to 4.75 |      | V    |

| Linear Output Current               | <1% THD at 100 kHz                                                 |     | 125          |      | mA   |

| Short-Circuit Current               | Sourcing/sinking                                                   |     | 248/294      |      | mA   |

| Capacitive Load Drive               | Peaking ≤ 3 dB                                                     |     | 47           |      | pF   |

| POWER SUPPLY                        |                                                                    |     |              |      |      |

| Operating Range                     | Operation outside of this range results in performance degradation | 2.9 |              | 5.5  | V    |

| Quiescent Current per Amplifier     | Enabled (ENA = 5 V), no load                                       |     | 6.8          | 10   | mA   |

|                                     | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>    |     |              | 10.4 | mA   |

|                                     | Disabled (ENA = $0 \text{ V}$ ), no load                           |     | 90           |      | μΑ   |

|                                     | $V_{IN} = 18 V$ (short-to-battery), no load                        |     | 5.3          |      | mA   |

| Power Supply Rejection Ratio (PSRR) | $+V_S = 4.5 \text{ V}$ to 5.5 V, $V_{REF}$ is forced to 2.5 V      |     | 53           |      | dB   |

| OPERATING TEMPERATURE RANGE         |                                                                    | -40 |              | +125 | °C   |

#### **3.3 V OPERATION**

$T_{A}=25^{\circ}C, +V_{S}=3.3 \text{ V}, R_{L}=1 \text{ k}\Omega, V_{REF}=1.65 \text{ V} \text{ (floating)}, V_{INCM}=+V_{S}/2, R_{STB}=5 \text{ k}\Omega \text{ to } +V_{S}, unless \text{ otherwise specified.}$

Table 2.

| Parameter                                     | Test Conditions/Comments                                        | Min     | Тур     | Max  | Unit   |

|-----------------------------------------------|-----------------------------------------------------------------|---------|---------|------|--------|

| DYNAMIC PERFORMANCE                           |                                                                 |         |         |      |        |

| –3 dB Large Signal Bandwidth                  | $V_{OUT} = 0.5 \text{ V p-p, } R_L = 150 \Omega$                | 63      | 73      |      | MHz    |

| -                                             | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 58      |         |      | MHz    |

|                                               | $V_{OUT} = 0.1 \text{ V p-p, } R_L = 1 \text{ k}\Omega$         |         | 89      |      | MHz    |

|                                               | $V_{OUT} = 0.1 \text{ V p-p, } R_L = 150 \Omega$                | 64      | 78      |      | MHz    |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 59      |         |      | MHz    |

| Bandwidth for 0.1 dB Flatness                 | $V_{OUT} = 0.5 \text{ V p-p, } R_L = 150 \Omega$                |         | 20      |      | MHz    |

| Slew Rate (t <sub>R</sub> /t <sub>F</sub> )   | $V_{OUT} = 1 \text{ V step}$                                    | 147/155 | 165/180 |      | V/µs   |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 136/145 |         |      | V/µs   |

| Settling Time to 0.1%                         | $V_{OUT} = 1 \text{ V step}$                                    |         | 25      |      | ns     |

| NOISE/DISTORTION PERFORMANCE                  |                                                                 |         |         |      |        |

| Output Voltage Noise                          | f = 1 MHz                                                       |         | 28      |      | nV/√H: |

| Differential Gain Error (NTSC)                | $R_L = 150 \Omega, V_{IN} = 1 V p-p$                            |         | 0.1     |      | %      |

| Differential Phase Error (NTSC)               | $R_L = 150 \Omega, V_{IN} = 1 V p-p$                            |         | 0.1     |      | Degree |

| Signal-to-Noise Ratio                         | f = 100 kHz to 15 MHz, V <sub>OUT</sub> = 0.5 V p-p             |         | 73      |      | dB     |

| DC PERFORMANCE                                |                                                                 |         |         |      |        |

| Nominal Gain                                  | V <sub>IN</sub> to V <sub>OUT</sub>                             | 0.49    | 0.50    | 0.51 | V/V    |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 0.49    |         | 0.51 | V/V    |

| Output Bias Voltage                           | ,                                                               | 1.60    | 1.65    | 1.70 | V      |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 1.59    |         | 1.71 | V      |

| INPUT CHARACTERISTICS                         | ,                                                               |         |         |      |        |

| Input Resistance (Differential Mode)          |                                                                 |         | 6.7     |      | kΩ     |

| Input Resistance (Common Mode)                |                                                                 |         | 2       |      | kΩ     |

| Input Common-Mode Voltage Range               | V <sub>REF</sub> voltage adjusted to optimized range            | -8      |         | +6   | V      |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | -8      |         | +6   | V      |

| Common-Mode Rejection (CMR)                   | $V_{IN} = \pm 3.3 \text{ V}$                                    | 41      | 54      |      | dB     |

| ·                                             | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 40      |         |      | dB     |

| SHORT-TO-BATTERY CHARACTERISTICS              | ,                                                               |         |         |      |        |

| Input Current                                 | $V_{IN} = 18 V$ (short-to-battery)                              |         | 4.4     |      | mA     |

| Protected Input Voltage Range                 | , ,                                                             | -9      |         | +20  | V      |

| , 3                                           | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | -9      |         | +20  | V      |

| Short-to-Battery Output Flag Trigger<br>Level | Minimum VIN needed to signal an input fault condition           | 7.4     | 7.8     | 8.2  | V      |

|                                               | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub> | 7.4     |         | 8.2  | V      |

Rev. C | Page 4 of 22

# ADA4830-1/ADA4830-2

| Parameter                           | Test Conditions/Comments                                           | Min | Тур          | Max  | Unit |

|-------------------------------------|--------------------------------------------------------------------|-----|--------------|------|------|

| VOLTAGE REFERENCE INPUT             |                                                                    |     |              |      |      |

| Input Voltage Range                 |                                                                    |     | 0.2 to 2.2   |      | V    |

| Input Resistance                    |                                                                    |     | 20           |      | kΩ   |

| Gain                                | V <sub>REF</sub> to V <sub>OUT</sub>                               |     | 1            |      | V/V  |

| LOGIC OUTPUT/INPUT CHARACTERISTICS  |                                                                    |     |              |      |      |

| STB V <sub>OH</sub>                 | V <sub>IN</sub> ≤ 7.4 V (normal operation)                         |     | 3.3          |      | V    |

| STB V <sub>OL</sub>                 | V <sub>IN</sub> ≥ 8.2 V (fault condition), ADA4830-1/ADA4830-2     |     | 85/178       |      | mV   |

| ENA V <sub>IH</sub>                 | Voltage to enable device                                           |     | ≥1.8         |      | V    |

| ENA V <sub>IL</sub>                 | Voltage to disable device                                          |     | ≤0.8         |      | V    |

| OUTPUT CHARACTERISTICS              |                                                                    |     |              |      |      |

| Output Voltage Swing                | $R_L = 150 \Omega$ to ground                                       |     | 0.01 to 3.08 |      | V    |

| Linear Output Current               | <1% THD at 100 kHz                                                 |     | 50           |      | mA   |

| Short-Circuit Current               | Sourcing/sinking                                                   |     | 85/180       |      | mA   |

| Capacitive Load Drive               | Peaking ≤ 4 dB                                                     |     | 47           |      | рF   |

| POWER SUPPLY                        |                                                                    |     |              |      |      |

| Operating Range                     | Operation outside of this range results in performance degradation | 2.9 |              | 5.5  | V    |

| Quiescent Current per Amplifier     | Enabled (ENA = 3.3 V), no load                                     |     | 5.5          | 8.0  | mA   |

|                                     | ADA4830-1W/ADA4830-2W only T <sub>MIN</sub> to T <sub>MAX</sub>    |     |              | 8.4  | mA   |

|                                     | Disabled (ENA = 0 V), no load                                      |     | 60           |      | μΑ   |

|                                     | $V_{IN} = 18 V$ (short-to-battery), no load                        |     | 4.3          |      | mA   |

| Power Supply Rejection Ratio (PSRR) | $+V_S = 3.0 \text{ V}$ to 3.6 V, $V_{REF}$ forced to 1.65 V        |     | 42           |      | dB   |

| OPERATING TEMPERATURE RANGE         |                                                                    | -40 |              | +125 | °C   |

**Data Sheet**

#### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                     | Rating           |

|-----------------------------------------------|------------------|

| Supply Voltage (+VS Pin)                      | 6 V              |

| Supply Voltage Delta                          |                  |

| +VS1 to +VS2, ADA4830-2 Only                  | 0.5 V            |

| Input Voltage Positive Direction (INNx, INPx) | 22 V             |

| Input Voltage Negative Direction (INNx, INPx) | -10 V            |

| Reference Voltage (VREFx Pin)                 | $+V_{S} + 0.3 V$ |

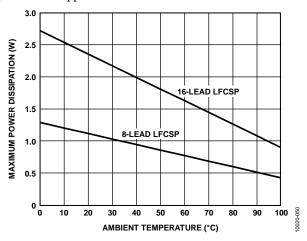

| Power Dissipation                             | See Figure 3     |

| Storage Temperature Range                     | −65°C to +150°C  |

| Operating Temperature Range                   | -40°C to +125°C  |

| Lead Temperature (Soldering, 10 sec)          | 260°C            |

| Junction Temperature                          | 150°C            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the device and its exposed paddle is soldered to a high thermal conductivity, 4-layer (2s2p) circuit board, as described in EIA/JESD 51-7.

Table 4.

| Package Type  | θ <sub>JA</sub> | θις | Unit |

|---------------|-----------------|-----|------|

| 8-Lead LFCSP  | 50              | 5   | °C/W |

| 16-Lead LFCSP | 54              | 6   | °C/W |

#### **MAXIMUM POWER DISSIPATION**

The maximum safe power dissipation in the ADA4830-1 and ADA4830-2 packages is limited by the associated rise in junction temperature (T<sub>1</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Exceeding a junction temperature of 150°C for an extended time can result in changes in the silicon devices, potentially causing failure.

The power dissipated in the package ( $P_D$ ) is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the supply voltage (+ $V_S$ ) times the quiescent current ( $I_S$ ). The power dissipated due to load drive depends on the particular application. The power due to load drive is calculated by multiplying the load current by the associated voltage drop across the device. RMS voltages and currents must be used in these calculations.

Airflow increases heat dissipation, effectively reducing  $\theta_{IA}$ .

Figure 3 shows the maximum power dissipation in the package vs. the ambient temperature for the 8-lead LFCSP (116°C/W) and the 16-lead LFCSP (54°C/W) on a JEDEC standard 4-layer board.  $\theta_{JA}$  values are approximate.

Figure 3. Maximum Power Dissipation vs. Ambient Temperature for a 4-Layer Board

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

ADA4830-1/ADA4830-2

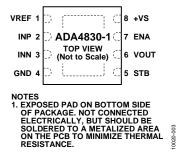

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 4. ADA4830-1 Pin Configuration

Table 5. ADA4830-1 Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                    |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VREF     | Voltage Reference Input. Sets the output dc bias voltage. Internally biased to $+V_s/2$ when left floating. See the Applications Information section.                                                                          |

| 2       | INP      | Positive Input.                                                                                                                                                                                                                |

| 3       | INN      | Negative Input.                                                                                                                                                                                                                |

| 4       | GND      | Power Supply Ground Pin.                                                                                                                                                                                                       |

| 5       | STB      | Short-to-Battery Indicator Output Pin. A logic low indicates an overvoltage condition (short-to-battery), whereas a logic high indicates normal operation. An open-drain configuration requires external pull-up resistor.     |

| 6       | VOUT     | Amplifier Output.                                                                                                                                                                                                              |

| 7       | ENA      | Enable Pin. Connect to $\pm V_S$ or float for normal operation. Connect to ground for device disable.                                                                                                                          |

| 8       | +VS      | Positive Power Supply Pin. Bypass this pin with a 0.1 µF capacitor to ground.                                                                                                                                                  |

|         | EPAD     | Exposed Pad. The exposed pad is located on the bottom side of the package. The pad is not connected electrically but should be soldered to a metalized area on the printed circuit board (PCB) to minimize thermal resistance. |

**Data Sheet**

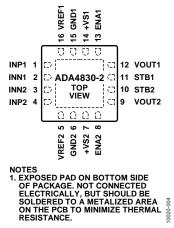

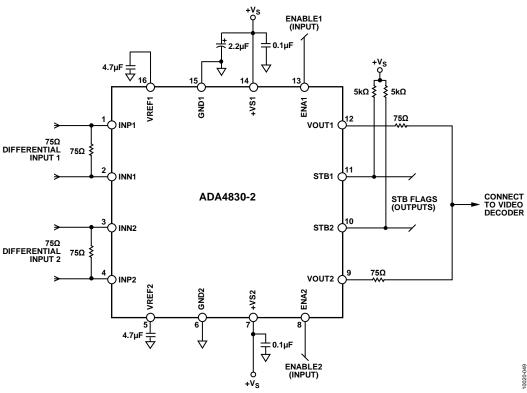

Figure 5. ADA4830-2 Pin Configuration

Table 6. ADA4830-2 Pin Function Descriptions

| Pin No. | Mnemonic     | Description                                                                                                                                                                                                                    |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4    | INP1, INP2   | Positive Inputs.                                                                                                                                                                                                               |

| 2, 3    | INN1, INN2   | Negative Inputs.                                                                                                                                                                                                               |

| 5, 16   | VREF2, VREF1 | Voltage Reference Inputs. Sets the output dc bias voltage. Internally biased to $+V_s/2$ when left floating. See the Applications Information section.                                                                         |

| 6, 15   | GND2, GND1   | Power Supply Ground Pins.                                                                                                                                                                                                      |

| 7, 14   | +VS2, +VS1   | Positive Power Supply Pins. These pins must be connected together, to the same voltage. Bypass these pins with a 0.1 µF capacitor to ground.                                                                                   |

| 8, 13   | ENA2, ENA1   | Enable Pins. Connect to +V <sub>s</sub> or float for normal operation and to ground for device disable.                                                                                                                        |

| 9, 12   | VOUT2, VOUT1 | Amplifier Outputs.                                                                                                                                                                                                             |

| 10, 11  | STB2, STB1   | Short-to-Battery Indicator Output Pins. A logic low indicates an overvoltage condition (short-to-battery), whereas a logic high indicates normal operation. An open-drain configuration requires an external pull-up resistor. |

|         | EPAD         | Exposed Pad. The exposed pad is located on the bottom side of the package. The pad is not connected electrically, but should be soldered to a metalized area on the PCB to minimize thermal resistance.                        |

### ADA4830-1/ADA4830-2

### TYPICAL PERFORMANCE CHARACTERISTICS

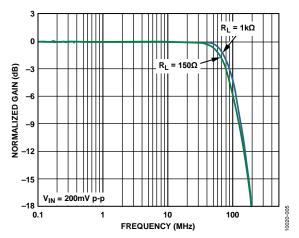

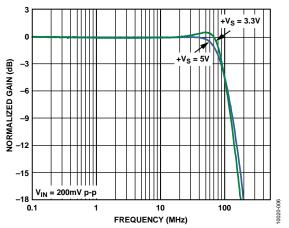

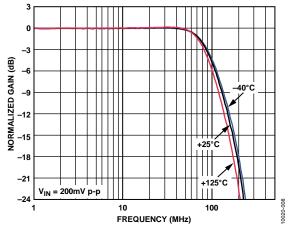

$T_{A}=25^{\circ}\text{C}\text{, }+V_{S}=5\text{ V}\text{, }R_{L}=1\text{ k}\Omega\text{, }V_{REF}=2.5\text{ V (floating), }V_{INCM}=+V_{S}/2\text{, }R_{STB}=5\text{ k}\Omega\text{ to }+V_{S}\text{, unless otherwise specified.}$

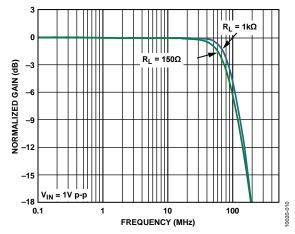

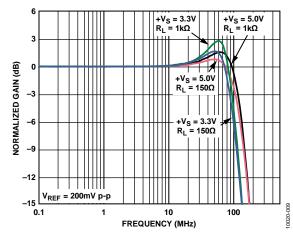

Figure 6. Small Signal Frequency Response for Various Loads

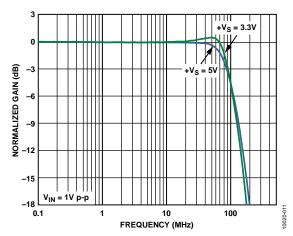

Figure 7. Small Signal Frequency Response for Various Supply Voltages

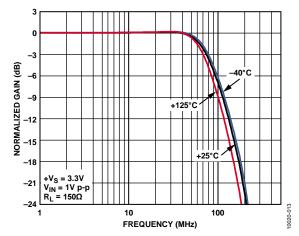

Figure 8. Small Signal Frequency Response for Various Temperatures

Figure 9. Large Signal Frequency Response for Various Loads

Figure 10. Large Signal Frequency Response for Various Supply Voltages

Figure 11. Large Signal Frequency Response for Various Temperatures

**Data Sheet**

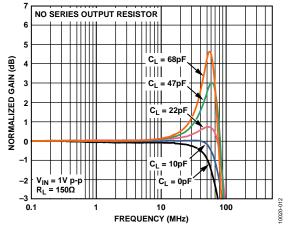

Figure 12. Large Signal Frequency Response for Various Capacitor Loads

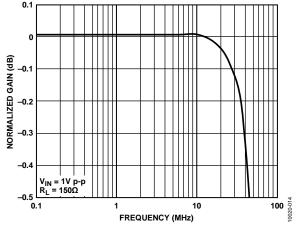

Figure 13. 0.1 dB Flatness

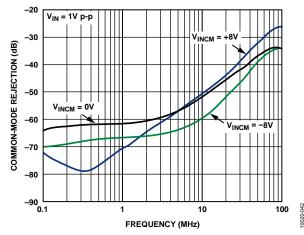

Figure 14. CMR Frequency Response for Various Input Common-Mode Voltages

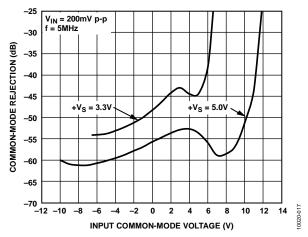

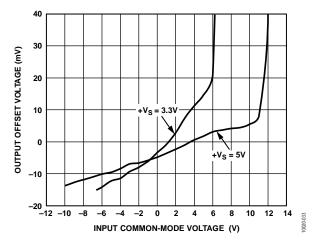

Figure 15. Small Signal CMR vs. V<sub>INCM</sub> for Various Supply Voltages

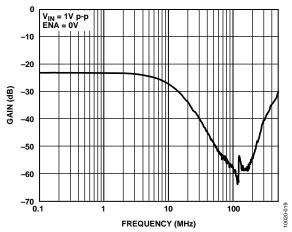

Figure 16. Input-to-Output Isolation with Device Disabled

Figure 17. V<sub>REF</sub> to V<sub>OUT</sub> Frequency Response

## ADA4830-1/ADA4830-2

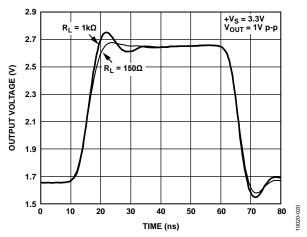

Figure 18. Pulse Response at  $+V_S = 3.3 \text{ V}$

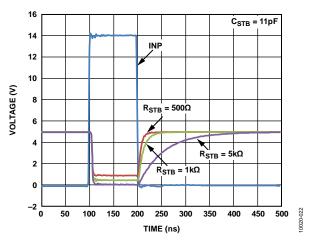

Figure 19. Short-to-Battery Output Flag Response for Various R<sub>STB</sub>, ADA4830-1

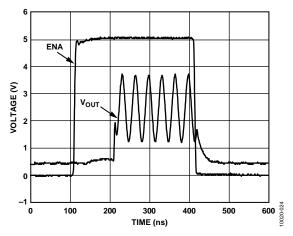

Figure 20. Enable Turn-on/Turn-off Time

Figure 21. Output Offset Voltage ( $V_{OUT} - V_{REF}$ ) vs. Input Common-Mode Voltage

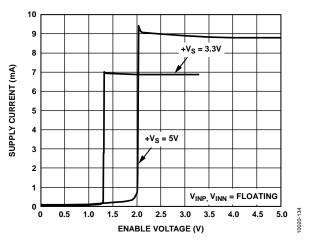

Figure 22. Supply Current vs. Enable Voltage

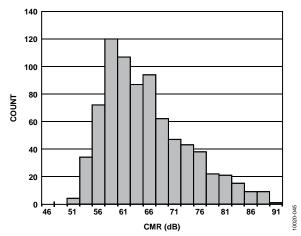

Figure 23. Typical Distribution of Common-Mode Rejection

### **Data Sheet**

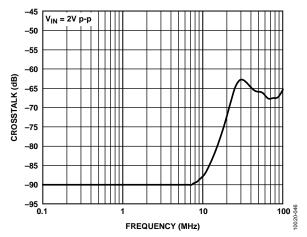

Figure 24. Crosstalk (Output-to-Output) vs. Frequency, ADA4830-2

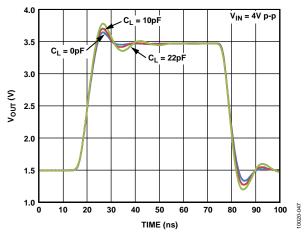

Figure 25. Pulse Response for Various Capacitor Loads

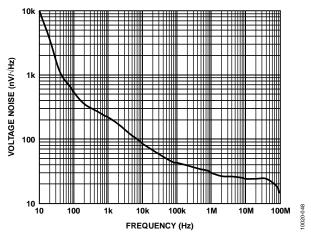

Figure 26. Total Output Voltage Noise vs. Frequency

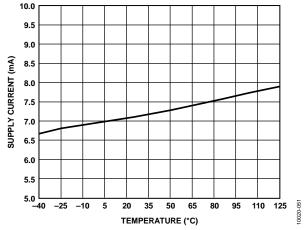

Figure 27. Supply Current vs. Temperature

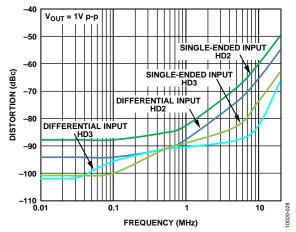

Figure 28. Harmonic Distortion Vs Frequency

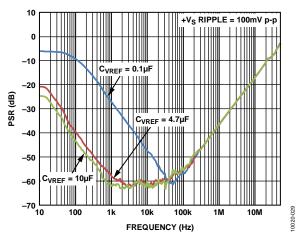

Figure 29. PSR vs. Frequency for Various VREF Bypass Capacitors

ADA4830-1/ADA4830-2

# THEORY OF OPERATION CORE AMPLIFIER

At the core of the ADA4830-1 and ADA4830-2 are high speed, rail-to-rail op amps that are built on a 0.35  $\mu$ m CMOS process. Together with the core amplifier, the ADA4830-1 and ADA4830-2 combine four highly matched on-chip resistors into a difference amplifier function. Common-mode range extension at its inputs is achieved by employing a resistive attenuator. The closed-loop differential to single-ended gain of the video channel is internally fixed at 0.50 V/V (-6 dB) to ensure compatibility with video decoders whose input range is constrained to 1 V p-p or less. The transfer function of the ADA4830-1 and ADA4830-2 is

$$V_{OUT} = \frac{V_{INP} - V_{INN}}{2} + V_{REF}$$

where:

$V_{OUT}$  is the voltage at the output pin, VOUT.

$V_{INP}$  and  $V_{INN}$  are the input voltages at the INP and INN pins, respectively.

$V_{REF}$  is the voltage at the VREF pin.

# OVERVOLTAGE (SHORT-TO-BATTERY) PROTECTION

Robust inputs guarantee that sensitive internal circuitry is not subjected to extreme voltages or currents during a stressful event. A short-to-battery condition usually consists of a voltage on either input (or both inputs) that is significantly higher than the power supply voltage of the amplifier. Duration may vary from a short transient to a continuous fault.

The ADA4830-1 and ADA4830-2 can withstand voltages of up to 18 V on the inputs. Critical internal nodes are protected from exposure to high voltages by circuitry that clamps the inputs at a safe level and limits internal currents. This protection is available whether the device is enabled or disabled, even when the supply voltage is removed.

#### **SHORT-TO-BATTERY OUTPUT FLAG**

The short-to-battery output flag (STB pin) is functionally independent of the short-to-battery protection. Its purpose is to indicate an overvoltage condition on either input. Because protection is provided passively, it is always available; the flag merely indicates the presence or absence of a fault condition.

#### **ESD PROTECTION**

All pins on the ADA4830-1 and ADA4830-2 are protected with internal ESD protection structures connected to the power supply pins (+VS and GND). These structures provide protection during the handling and manufacturing process.

The inputs (INN and INP) of the ADA4830-1 and ADA4830-2 can be exposed to dc voltages well above the supply voltage; therefore, conventional ESD structure protection cannot be used.

The ADA4830-1 and ADA4830-2 employ Analog Devices, Inc., proprietary ESD devices at the input pins (INN, INP) to allow for a wide common-mode voltage range and ESD protection well beyond the handling and manufacturing requirements.

The inputs of the ADA4830-1 and ADA4830-2 are ESD protected to survive ±8 kV human body model (HBM)

#### **POWER SUPPLY PINS (ADA4830-2)**

As indicated in the Absolute Maximum Ratings section, the voltage difference between the +VS1 and +VS2 pins of the ADA4830-2 cannot exceed 0.5 V. To ensure compliance with the Absolute Maximum Ratings, it is recommended that these supply pins be connected together to the same power supply source.

**Data Sheet**

### APPLICATIONS INFORMATION

#### **METHODS OF TRANSMISSION**

# Pseudo Differential Mode (Unbalanced Source Termination)

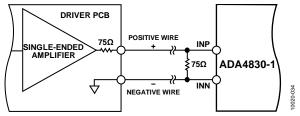

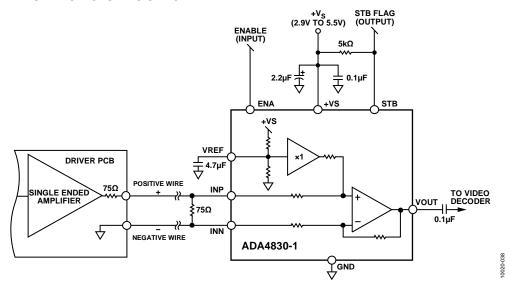

The ADA4830-1 and ADA4830-2 can be operated in a pseudo differential configuration with an unbalanced input signal. This allows the receiver to be driven by a single-ended source. Pseudo differential mode uses a single conductor to carry an unbalanced signal and connects the negative input terminal to the ground reference of the source.

Use the positive wire or coaxial center conductor to connect the source output to the positive input (INP) of the ADA4830-1 or ADA4830-2. Next, connect the negative wire or coaxial shield from the negative input (INN) back to a ground reference on the source printed circuit board (PCB). The input termination should match the source impedance and be referenced to the remote ground. An example of this configuration is shown in Figure 30.

Figure 30. Pseudo Differential Mode

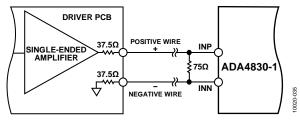

#### Pseudo Differential Mode (Balanced Source Impedance)

Pseudo differential signaling is typically implemented using unbalanced source termination, as shown in Figure 30. With this arrangement, however, common-mode signals on the positive and negative inputs receive different attenuation due to unbalanced termination at the source. This effectively converts some of the common-mode signal into differential mode signal, degrading the overall common-mode rejection of the system. System common-mode rejection can be improved by balancing the output impedance of the driver, as shown in Figure 31. Splitting the source termination resistance evenly between the hot and cold conductors results in matched attenuation of the common-mode signals, ensuring maximum rejection.

Figure 31. Pseudo Differential Mode with Balanced Source Impedance

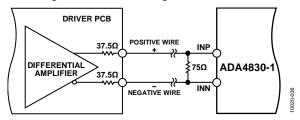

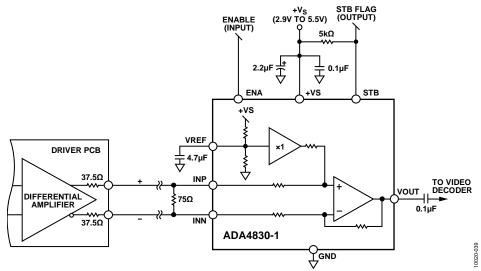

#### **Fully Differential Mode**

The differential inputs of the ADA4830-1 and ADA4830-2 allow full balanced transmission using a differential source. In this configuration, the differential input termination is equal to twice the source impedance of each output. For example, a source with 37.5  $\Omega$  back termination resistors in each leg should be terminated with a differential resistance of 75  $\Omega$ . An illustration of this arrangement is shown in Figure 32.

Figure 32. Fully Differential Mode

#### **VOLTAGE REFERENCE (VREF PIN)**

An internal reference level ( $V_{REF}$ ) determines the output voltage when the differential input voltage is zero. A resistor divider connected between the supply rails sets the  $V_{REF}$  voltage. Built with a pair of matched 40 k $\Omega$  resistors, the divider sets this voltage to  $+V_S/2$ .

The voltage reference pin (VREF) normally floats at its default value of  $+V_s/2$ . However, it can be used to vary the output reference level from this default value. A voltage applied to VREF appears at the output with unity gain, within the bandwidth limit of the internal reference buffer. Figure 17 shows the frequency response of the VREF input.

Any noise on the  $+V_s$  supply rail appears at the output with only 6 dB of attenuation (the divide-by-two provided by the reference divider). Even when this pin is floating, it is recommended that an external capacitor be connected from the reference node to ground to provide further attenuation of noise on the power supply line. A 4.7  $\mu$ F capacitor combined with the internal 40 k $\Omega$  resistor sets the low-pass corner at under 1 Hz and results in better than 40 dB of supply noise attenuation at 100 Hz.

### ADA4830-1/ADA4830-2

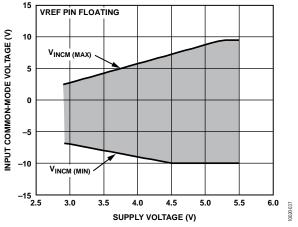

#### INPUT COMMON-MODE RANGE

In a standard four resistor difference amplifier with 0.50 V/V gain, the input common-mode (CM) range is three times the CM range of the core amplifier. In the ADA4830-1 and ADA4830-2, however, the input CM range has been extended to more than 18 V (with a 5 V supply). The input CM range can be approximated by using the following formulas:

For the maximum CM voltage,

$$5(+V_S - 1.25) - 4V_{REF} \approx V_{INCM(MAX)} \le 9.5 \text{ V}$$

For the minimum CM voltage,

$$-10 \text{ V} \le V_{INCM(MIN)} \approx -(1 + 4V_{REF})$$

Approximate minimum and maximum CM voltages are shown in Table 7 for several common supply voltages.

**Table 7. Input Common-Mode Range Examples**

| V <sub>REF</sub> (V) | $V_{INCM(MIN)}(V)$                                                                                    | $V_{INCM(MAX)}(V)$ |

|----------------------|-------------------------------------------------------------------------------------------------------|--------------------|

| 1.5 <sup>1</sup>     | -7.0                                                                                                  | 2.8                |

| 0.97                 | -4.9                                                                                                  | 4.9                |

| 1.65 <sup>1</sup>    | -7.6                                                                                                  | 3.6                |

| 1.15                 | -5.6                                                                                                  | 5.6                |

| 1.8 <sup>1</sup>     | -8.2                                                                                                  | 4.5                |

| 1.34                 | -6.4                                                                                                  | 6.4                |

| 2.5 <sup>1</sup>     | -10                                                                                                   | 8.7                |

| 2.22                 | -9.9                                                                                                  | 9.5                |

|                      | 1.5 <sup>1</sup><br>0.97<br>1.65 <sup>1</sup><br>1.15<br>1.8 <sup>1</sup><br>1.34<br>2.5 <sup>1</sup> | 1.5 <sup>1</sup>   |

<sup>&</sup>lt;sup>1</sup> Floating (default condition).

Figure 33. Input Common-Mode Range vs. Supply Voltage

#### SHORT-TO-BATTERY OUTPUT FLAG PIN

The flag output (STB) is an active low, open-drain logic configuration. A low level on this output indicates that an overvoltage event has been detected on either the positive or the negative input or both. Flags from multiple chips can be wire-OR'ed to form a single fault detection signal. The output is driven by a grounded source NMOS device, capable of sinking approximately 10 mA while pulling within a few hundred millivolts above ground. The output high level is set with an external pull-up resistor connected to the supply voltage of the logic family that is used to monitor the state of the flag.

In the falling direction, the speed with which the flag output responds primarily depends on the external capacitance attached to this node and the sink current that can be provided. For example, if the load is 10 pF, and the external pull-up voltage is 3.3 V, the fall time is a few nanoseconds. In the rising direction, the speed is determined by external capacitance and the magnitude of the pull-up resistor. For the case of 10 pF of external capacitance and a pull-up of 5 k $\Omega$ , the time constant of the rising edge is approximately 50 ns.

**Table 8. STB Pin Function**

| STB Pin Output | Device State        |

|----------------|---------------------|

| High (Logic 1) | Normal operation    |

| Low (Logic 0)  | STB fault condition |

#### **ENABLE/DISABLE MODES (ENA PIN)**

The power-down, or enable/disable (ENA) pin, is internally pulled up to  $+V_s$  through a 250 k $\Omega$  resistor. When the voltage on this pin is high, the amplifier is enabled; pulling ENA low disables the channel. With no external connection, this pin floats high, enabling the amplifier channel.

**Table 9. ENA Pin Function**

| ENA Pin Input     | Device State     |

|-------------------|------------------|

| High (Logic 1)    | Enabled          |

| Low (Logic 0)     | Disabled         |

| High-Z (Floating) | Normal operation |

#### **PCB LAYOUT**

As with all high speed applications, attention to PCB layout is of paramount importance. Adhere to standard high speed layout practices in designs using the ADA4830-1 and ADA4830-2. A solid ground plane is recommended, and placing a 0.1  $\mu F$  surfacemount, ceramic power supply, decoupling capacitor as close as possible to the supply pin(s) is recommended.

Connect the GND pin(s) to the ground plane with a trace that is as short as possible. In cases where the ADA4830-1 and ADA4830-2 drive transmission lines, series terminate the outputs and use controlled impedance traces of the shortest length possible to connect to the signal I/O pins, which should not pass over any voids in the ground plane.

#### **EXPOSED PADDLE (EPAD) CONNECTION**

The ADA4830-1 and ADA4830-2 have an exposed thermal pad (EPAD) on the bottom of the package. This pad is not electrically connected to the die and can be left floating or connected to the ground plane. Should heat dissipation be a concern, thermal resistance can be minimized by soldering the EPAD to a metalized pad on the PCB. Connect this pad to the ground plane with multiple vias. Note that the thermal resistance ( $\theta_{IA}$ ) of the device is specified with the EPAD soldered to the PCB.

**Data Sheet**

# USING THE ADA4830-2 AS A LOW COST VIDEO SWITCH

Figure 34 shows a video multiplexer/switch using the ADA4830-2, dual, high speed difference amplifier. This circuit allows the user to input two remote video sources into a single channel of a video decoder, such as the ADV7180.

Traditional CMOS multiplexers and switches suffer several disadvantages at video frequencies where their on-resistance introduces distortion, degrades differential gain and phase performance, and interacts with the termination resistor to attenuate the incoming video signal and affect the luminance. System designers generally address these issues by adding external buffers to add gain and increase drive capability.

Video multiplexing can be simplified by using high speed video amplifiers with a disable/enable function (sometimes called powerdown). When the amplifier is disabled, its output stage goes into a high impedance state, allowing several amplifier outputs to be

wired together. High speed video op amps have all the key features required to make them ideal for this function. Their high input impedance does not affect the characteristic impedance of the transmission line, thus allowing back termination. They also have inherently good video specifications, including differential gain and phase, slew rate, bandwidth, and 0.1 dB flatness.

Each channel of the ADA4830-2 is a high speed difference amplifier circuit that eliminates common-mode noise and phase noise caused by ground potential differences between the incoming video signal and the receiver. The ADA4830-2 also offers integrated short-to-battery protection and heightened ESD tolerance in a small foot print. The fault detection output (the STB pins) of the ADA4830-2 allows for proactive wire diagnostics when connected to a microcontroller or video decoder and are used to generate an interrupt during a fault condition.

Figure 34. Low Cost Video Switch Using the ADA4830-2

### ADA4830-1/ADA4830-2

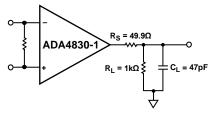

#### **DRIVING CAPACITIVE LOADS**

The ADA4830-1 and ADA4830-2 are capable of driving large capacitive loads while maintaining its rated performance. Several performance curves vs. capacitive load are shown in Figure 12 and Figure 25. Capacitive loads interact with an op amp's output impedance to create an extra delay in the feedback path. This reduces circuit stability and can cause unwanted ringing and oscillation.

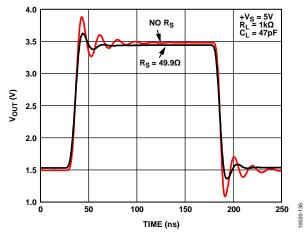

The capacitive load drive of the ADA4830-1 and ADA4830-2 can be increased by adding a low valued resistor, R<sub>s</sub>, in series with the capacitive load. Figure 35 shows the test circuit.

Figure 35. Rs Test Circuit

Introducing a series resistor tends to isolate the capacitive load from the feedback loop, thereby diminishing its influence. One drawback to this approach is a slight loss of signal amplitude. Figure 36 shows the effects of a series resistor on the capacitive drive. For very large capacitive loads, the frequency response of the amplifier is dominated by the roll-off of the series resistor and capacitive load.

Figure 36. Pulse Response With and Without Series Resistor

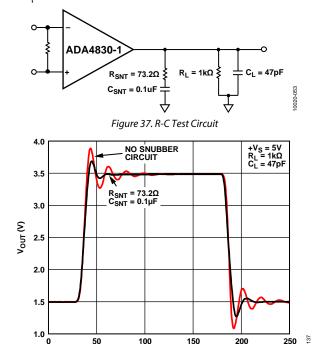

Another method of reducing the resonant peaking caused by driving large capacitive loads at the output of the ADA4830-1 and ADA4830-2 is with the use of a R-C shunt circuit or a snubber circuit. This method acts to resistively load the amplifier output, thus reducing frequency response peaking. One drawback to this approach is a slight loss of signal bandwidth. Figure 37 shows a simple circuit representation of the implementation of the R-C snubber circuit with  $R_{\text{SNT}}$  and  $C_{\text{SNT}}$ . Figure 38 shows the effects of a R-C snubber circuit driving 47 pF, where  $R_{\text{SNT}}=73.2~\Omega$  and  $C_{\text{SNT}}=0.1~\mu\text{F}$ .

TIME (ns)

Figure 38. Pulse Response With and Without R-C Snubber Circuit

**Data Sheet**

### TYPICAL APPLICATIONS CIRCUITS

Figure 39. Typical Application with Pseudo Differential Input

Figure 40. Typical Application with Fully Differential Input

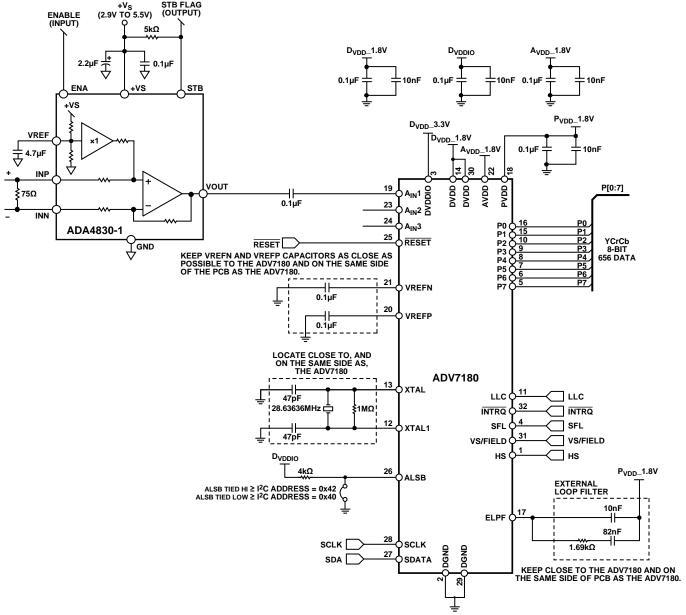

Figure 41. ADA4830-1 Driving an ADV7180 Video Decoder

The ADA4830-1 and ADA4830-2 are differential receivers whose overall performance is independent of the transmitter IC used and whether the transmission line is ac-coupled or dc-coupled.

The ADA4830-1 and ADA4830-2 are specifically designed to perform as differential line receivers. The circuit in Figure 41 shows a detailed schematic of the ADA4830-1 and the ADV7180 configured for this function. The signal is received differentially relative to the common of the source circuitry, and that voltage is exactly reproduced with an attenuating gain of 0.50 V/V. This is designed to keep the video signal within the allowed range of the video decoder, which is typically 1 V p-p or less.

The common-mode rejection vs. frequency, shown in Figure 14, typically 65 dB at low frequencies, enables the recovery of video signals in the presence of large common-mode noise. The high input impedance permits the ADA4830-1 and ADA4830-2 to operate as a bridging amplifier across low impedance terminations with negligible loading.

**Data Sheet**

#### **FULLY DC-COUPLED TRANSMISSION LINE**

The wide input common-mode range and high input impedance of the ADA4830-1 and ADA4830-2 allow them to be used in fully dc-coupled transmission line applications in which there may be a significant discrepancy between voltage levels at the ground pins of the driver and receiver. As long as the voltage difference between

reference levels at the transmitter and receiver is within the common-mode range of the receiver, very little current flow results, and no image degradation should be anticipated.

Figure 42 shows an example configuration of a completely dccoupled transmission using a low impedance differential driver.

Figure 42. Differential Video Filter Driver and ADA4830-1 Difference Amplifier

### ADA4830-1/ADA4830-2

### PACKAGING AND ORDERING INFORMATION

#### **OUTLINE DIMENSIONS**

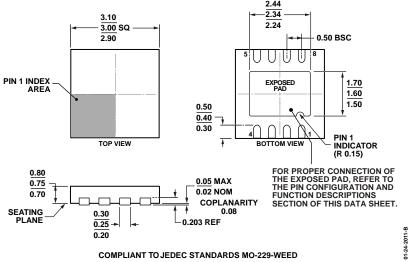

Figure 43. 8-Lead Lead Frame Chip Scale Package [LFCSP\_WD] 3 mm × 3 mm Body, Very Very Thin, Dual Lead (CP-8-11)

Dimensions shown in millimeters

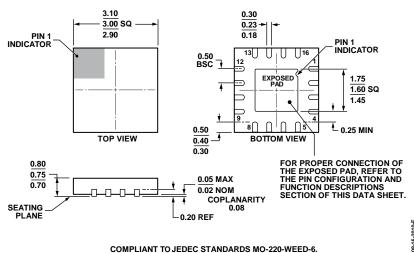

Figure 44. 16-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 3 mm × 3 mm Body, Very Very Thin Quad (CP-16-22) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description                              | Package<br>Option | Branding | Ordering<br>Quantity |

|-----------------------|-------------------|--------------------------------------------------|-------------------|----------|----------------------|

| ADA4830-1BCP-EBZ      |                   | Evaluation Board                                 |                   |          |                      |

| ADA4830-1BCPZ-R7      | -40°C to +125°C   | 8-Lead Lead Frame Chip Scale Package [LFCSP_WD]  | CP-8-11           | H30      | 1500                 |

| ADA4830-1WBCPZ-R7     | -40°C to +125°C   | 8-Lead Lead Frame Chip Scale Package [LFCSP_WD]  | CP-8-11           | 4H1      | 1500                 |

| ADA4830-1BCPZ-R2      | -40°C to +125°C   | 8-Lead Lead Frame Chip Scale Package [LFCSP_WD]  | CP-8-11           | H30      | 250                  |

| ADA4830-2BCPZ-R7      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-22          | H31      | 1500                 |

| ADA4830-2BCPZ-R2      | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-22          | H31      | 250                  |

| ADA4830-2WBCPZ-R7     | -40°C to +125°C   | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-22          | 4H2      | 1500                 |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

$<sup>^{2}</sup>$  W = Qualified for Automotive Applications.

**Data Sheet**

#### **AUTOMOTIVE PRODUCTS**

The ADA4830-1W and ADA4830-2W models are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial model; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

### **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com