# **ADAU1860BCBZRL Datasheet**

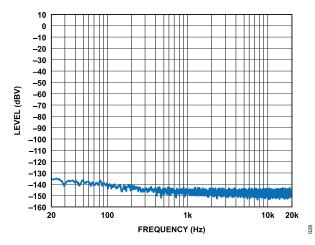

www.digi-electronics.com

| DiGi Electronics Part Number | ADAU1860BCBZRL-DG                                           |

|------------------------------|-------------------------------------------------------------|

| Manufacturer                 | Analog Devices Inc.                                         |

| Manufacturer Product Number  | ADAU1860BCBZRL                                              |

| Description                  | 56-BUMP WAFER LEVEL CHIP SCALE P                            |

| Detailed Description         | Audio Interface 24 b I2C, I2S, SPI 56-WLCSP (2.98x2<br>.68) |

|                              |                                                             |

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

### Purchase and inquiry

| Manufacturer Product Number:         | Manufacturer:                    |

|--------------------------------------|----------------------------------|

| ADAU1860BCBZRL                       | Analog Devices Inc.              |

| Series:                              | Product Status:                  |

|                                      | Active                           |

| Type:                                | Data Interface:                  |

| Audio                                | 12C, 12S, SPI                    |

| Resolution (Bits):                   | Number of ADCs / DACs:           |

| 24 b                                 | 3 / 1                            |

| Sigma Delta:                         | S/N Ratio, ADCs / DACs (db) Typ: |

| No                                   |                                  |

| Dynamic Range, ADCs / DACs (db) Typ: | Voltage - Supply, Analog:        |

| 110 / 130                            | 1.7V ~ 1.98V                     |

| Voltage - Supply, Digital:           | Operating Temperature:           |

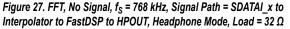

| 0.85V ~ 1.21V                        | -40°C ~ 85°C                     |

| Mounting Type:                       | Package / Case:                  |

| Surface Mount                        | 56-UFBGA, WLCSP                  |

| Supplier Device Package:             |                                  |

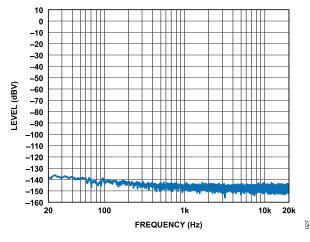

| 56-WLCSP (2.98x2.68)                 |                                  |

### **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

### ADAU1860/ADAU1860-1

### Three ADCs, One DAC, Low Power Codec with Audio DSPs

#### **FEATURES**

- Programmable FastDSP audio processing engine

- Up to 768 kHz sample rate

- ▶ Biquad filters, limiters, volume controls, mixing

- ▶ Tensilica HiFi 3z DSP core

- Quad MAC per cycle: 24 × 24-bit multiplier and 64-bit accumulator

- Flexible power operation mode: 24.576 MHz, 49.152 MHz, 73.728 MHz, and 98.304 MHz

- ▶ 288 kB total memory

- ▶ JTAG debug and trace

- ▶ Low latency, 24-bit ADCs and DAC

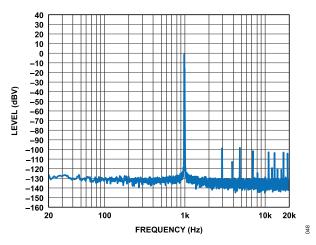

- ▶ 106 dB SNR (signal through ADC with A-weighted filter)

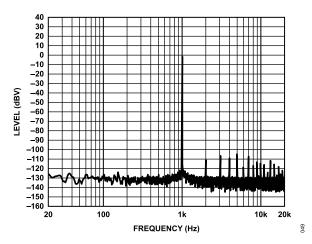

- 110 dB combined SNR (signal through DAC and headphone with A-weighted filter)

- Programmable double precision MAC engine for maximum 24stage equalizer

- ▶ Serial port sample rates from 8 kHz to 768 kHz

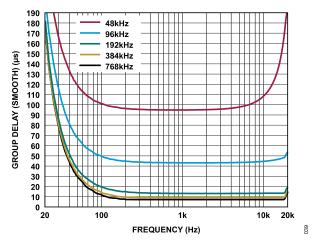

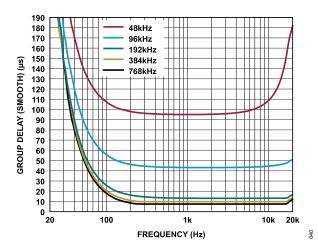

- ▶ 5 µs group delay (f<sub>S</sub> = 768 kHz) analog in to analog out with FastDSP bypass (zero instructions)

- 3 differential or single-ended analog inputs, configurable as microphone or line inputs

- ▶ 8 digital microphone inputs

- Analog differential audio output, configurable as either line output or headphone drive

- 2 PDM output channels

- ▶ PLL supporting any input clock rate from 30 kHz to 36 MHz

- ▶ 4 channel asynchronous sample rate converters (ASRCs)

- 2, 16-channel serial audio ports supporting I<sup>2</sup>S, left justified, right justified, or up to TDM16 (TDM12 in Turbo mode)

- ▶ 8 interpolators and 8 decimators with flexible routing

- Power supplies

- ▶ Digital I/O IOVDD at 1.1 V to 1.98 V

- ▶ Digital DVDD at 0.85 V to 1.21 V

- Headphone HPVDD at 1.8 V typical

- ► Headphone HPVDD L at 1.2 V to HPVDD

- ► Control/communication interfaces

- ▶ I<sup>2</sup>C, SPI, or UART control ports

- Master quad SPI (QSPI)

- ► UART communication port

- Self-boot from QSPI flash

- Flexible GPIO and IRQ

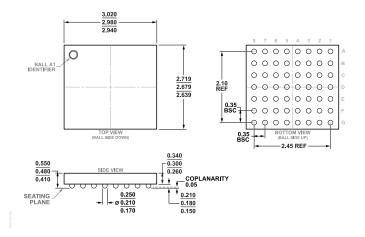

- ▶ 56-ball, 0.35 mm pitch, 2.980 mm × 2.679 mm WLCSP

Rev. C

#### DOCUMENT FEEDBACK

#### TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### **APPLICATIONS**

- Noise canceling handsets, headsets, and headphones

- Bluetooth active noise canceling (ANC) handsets, headsets, and headphones

- Personal navigation devices

- Digital still and video cameras

- Musical instrument effect processors

- Multimedia speaker systems

- Smartphones

#### **GENERAL DESCRIPTION**

The ADAU1860/ADAU1860-1 are codecs with three inputs and one output that incorporate two digital signal processors (DSPs). The path from the analog input to the DSP core to the analog output is optimized for low latency and is ideal for noise canceling earphones. With the addition of just a few passive components, the ADAU1860/ADAU1860-1 provide a complete earphone solution.

All specifications, functions, and features described in this data sheet are shared between the ADAU1860 and the ADAU1860-1. The ADAU1860 is only available for ordering by customers located in the People's Republic of China (PRC). The ADAU1860-1 is available for ordering by customers located outside of PRC.

Analog Devices is in the process of updating documentation to provide terminology and language that is culturally appropriate. This is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

## ADAU1860/ADAU1860-1

#### TABLE OF CONTENTS

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| General Description                     | 1  |

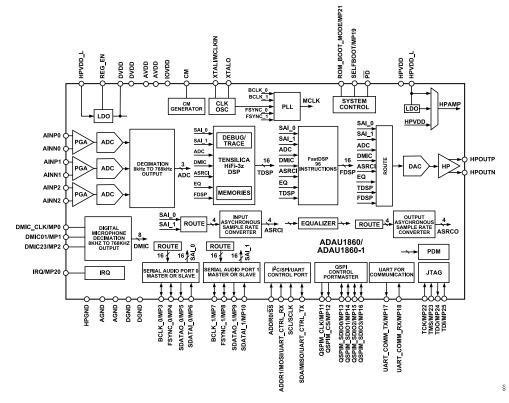

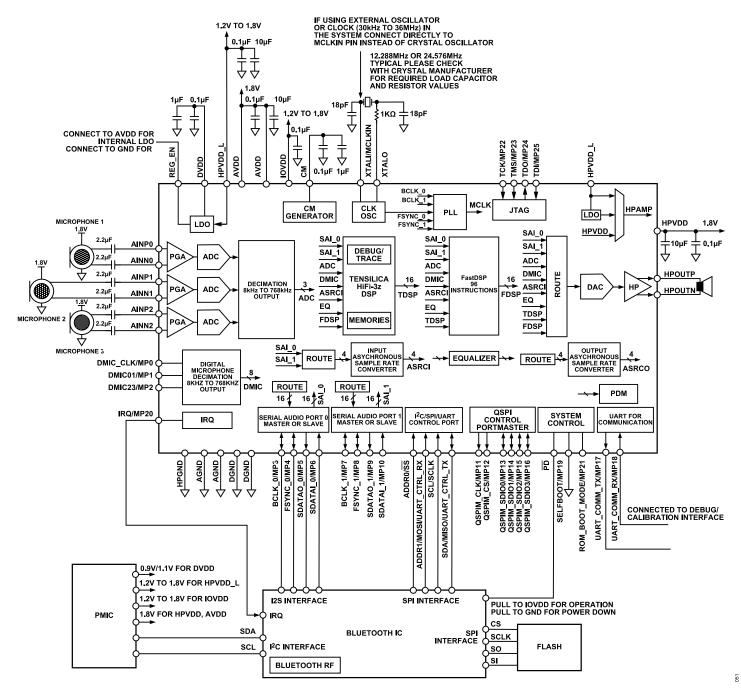

| Functional Block Diagram                | 3  |

| Specifications                          | 4  |

| Analog Performance Specifications       | 4  |

| Crystal Amplifier Specifications        | 8  |

| Digital Input and Output Specifications | 9  |

| Power Supply Specifications             | 9  |

| Power-Down Current                      | 9  |

| Typical Power Consumption               | 10 |

| Digital Filters                         | 11 |

| Digital Timing Specifications           | 11 |

| Absolute Maximum Ratings                | 16 |

|                                             | 10   |

|---------------------------------------------|------|

| Electrostatic Discharge (ESD) Ratings       | . 10 |

| ESD Caution                                 | .16  |

| Pin Configuration and Function Descriptions | 17   |

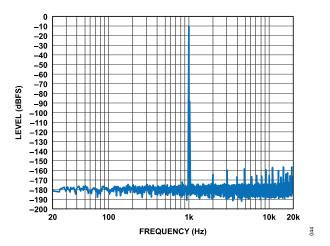

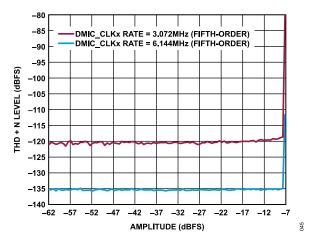

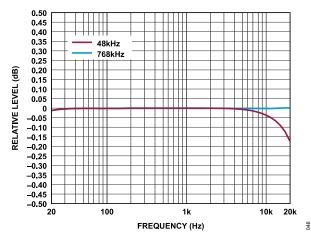

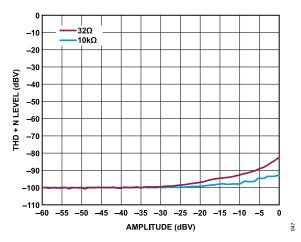

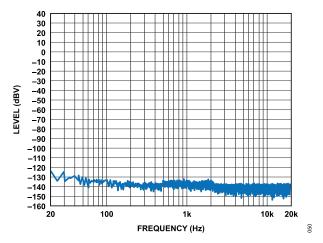

| Typical Performance Characteristics         | 20   |

| Theory of Operation                         | .27  |

| System Block Diagram                        |      |

| Applications Information                    |      |

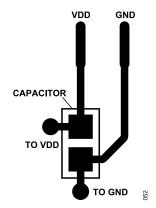

| Power Supply Bypass Capacitors              | 29   |

| Layout                                      | .29  |

| Grounding                                   |      |

| Outline Dimensions                          | 30   |

| Ordering Guide                              | 30   |

| Evaluation Boards                           | 30   |

#### **REVISION HISTORY**

| 9/2024—Rev. B to Rev. C                                |    |

|--------------------------------------------------------|----|

| Change to Features Section                             | 1  |

| 11/2023—Rev. A to Rev. B                               |    |

| Added ADAU1860-1 (Universal)                           | 1  |

| Changes to General Description Section                 | 1  |

| 9/2022—Rev. 0 to Rev. A                                |    |

| Changes to Features Section                            | 1  |

| Changes to Table 1                                     | 4  |

| Changes to Typical Performance Characteristics Section | 20 |

| Changes to Theory of Operation Section                 |    |

#### 10/2021—Revision 0: Initial Version

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### SPECIFICATIONS

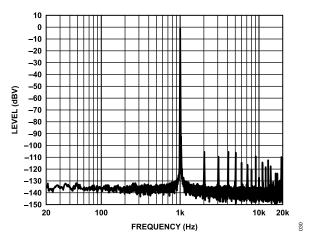

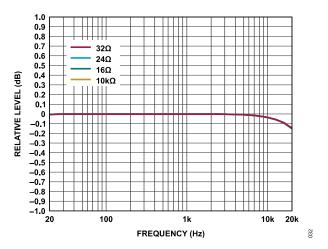

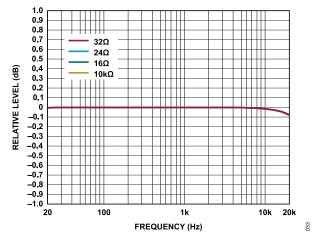

Master clock = 24.576 MHz, Hibernate 1 mode, serial input sample rate = 48 kHz, measurement bandwidth = 20 Hz to 20 kHz, word width = 24 bits, ambient temperature =  $25^{\circ}$ C, and outputs line loaded with 10 k $\Omega$ , unless otherwise noted.

#### ANALOG PERFORMANCE SPECIFICATIONS

Supply voltages: AVDD = HPVDD = IOVDD = 1.8 V, and DVDD = 0.9 V, unless otherwise noted.

| Parameter                                      | Test Conditions/Comments                        | Min    | Тур   | Max | Unit  |

|------------------------------------------------|-------------------------------------------------|--------|-------|-----|-------|

| ANALOG-TO-DIGITAL CONVERTERS (ADCs)            |                                                 |        | 11    | -   |       |

| ADC Resolution                                 | All ADCs                                        |        | 24    |     | Bits  |

| Digital Gain Step                              |                                                 |        | 0.375 |     | dB    |

| Digital Gain Range                             |                                                 | -71.25 | 0.010 | +24 | dB    |

| INPUT RESISTANCE (R <sub>IN</sub> )            |                                                 | 11.20  |       | .71 |       |

| Single-Ended Line Input                        | Nonvoice wake-up mode                           |        | 9     |     | kΩ    |

|                                                | Voice wake-up mode                              |        | 18    |     | kΩ    |

| Differential Line Input                        | Nonvoice wake-up mode                           |        | 36    |     | kΩ    |

|                                                | Voice wake-up mode                              |        | 36    |     | kΩ    |

| Programmable Gain Amplifier (PGA) Single-Ended | PGA high R <sub>IN</sub> , normal, 0 dB gain    |        | 20.6  |     | kΩ    |

| Inputs                                         | PGA high R <sub>IN</sub> , normal, 24 dB gain   |        | 2.4   |     | kΩ    |

|                                                | PGA low R <sub>IN</sub> , enhanced, 0 dB gain   |        | 10.3  |     | kΩ    |

|                                                | PGA low R <sub>IN</sub> , enhanced, 24 dB gain  |        | 1.2   |     | kΩ    |

|                                                | PGA high R <sub>IN</sub> , enhanced, 0 dB gain  |        | 20.6  |     | kΩ    |

|                                                | PGA high R <sub>IN</sub> , enhanced, 24 dB gain |        | 2.4   |     | kΩ    |

| PGA Differential Inputs                        | PGA high R <sub>IN</sub> , normal, 0 dB gain    |        | 41.2  |     | kΩ    |

|                                                | PGA high R <sub>IN</sub> , normal, 24 dB gain   |        | 4.8   |     | kΩ    |

|                                                | PGAlow R <sub>IN</sub> , enhanced, 0 dB gain    |        | 20.6  |     | kΩ    |

|                                                | PGA low R <sub>IN</sub> , enhanced, 24 dB gain  |        | 2.4   |     | kΩ    |

|                                                | PGA high R <sub>IN</sub> , enhanced, 0 dB gain  |        | 41.2  |     | kΩ    |

|                                                | PGA high R <sub>IN</sub> , enhanced, 24 dB gain |        | 4.8   |     | kΩ    |

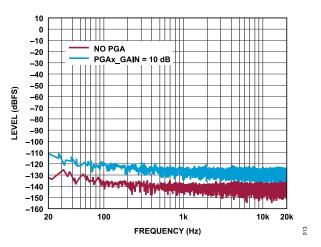

| SINGLE-ENDED LINE INPUT                        | PGAx_EN = 0, and PGAx_SLEW_DIS = 1              |        |       |     |       |

| Full-Scale Input Voltage                       | 0 dBFS                                          |        | 0.49  |     | V rms |

|                                                | 0 dBFS                                          |        | 1.39  |     | V p-p |

| Dynamic Range <sup>1</sup>                     | 20 Hz to 20 kHz, -60 dB input                   |        |       |     |       |

| With A-Weighted Filter (RMS)                   | Enhanced performance                            |        | 103   |     | dB    |

|                                                | Normal performance                              |        | 103   |     | dB    |

|                                                | Power saving                                    |        | 102   |     | dB    |

|                                                | Voice wake up                                   |        | 99    |     | dB    |

| With Flat 20 Hz to 20 kHz Filter               | Enhanced performance                            |        | 98    |     | dB    |

|                                                | Normal performance                              |        | 98    |     | dB    |

|                                                | Power saving                                    |        | 98    |     | dB    |

|                                                | Voice wake up                                   |        | 96    |     | dB    |

| Signal-to-Noise Ratio (SNR) <sup>2</sup>       |                                                 |        |       |     |       |

| With A-Weighted Filter (RMS)                   | Enhanced performance                            |        | 102   |     | dB    |

|                                                | Normal performance                              |        | 102   |     | dB    |

|                                                | Power saving                                    |        | 102   |     | dB    |

|                                                | Voice wake up                                   |        | 98    |     | dB    |

| With Flat 20 Hz to 20 kHz Filter               | Enhanced performance                            |        | 98    |     | dB    |

|                                                | Normal performance                              |        | 98    |     | dB    |

|                                                | Power saving                                    |        | 98    |     | dB    |

|                                                | Voice wake up                                   |        | 95    |     | dB    |

### ADAU1860/ADAU1860-1

#### **SPECIFICATIONS**

#### Table 1. (Continued)

| Parameter                                   | Test Conditions/Comments                 | Min | Тур  | Max | Unit  |

|---------------------------------------------|------------------------------------------|-----|------|-----|-------|

| Interchannel Gain Mismatch                  |                                          |     | 40   |     | mdB   |

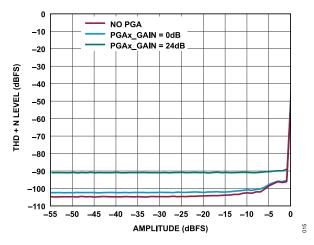

| Total Harmonic Distortion + Noise (THD + N) | 20 Hz to 20 kHz, -1 dB full-scale output |     |      |     |       |

|                                             | Enhanced performance                     |     | -78  |     | dBFS  |

|                                             | Normal performance                       |     | -78  |     | dBFS  |

|                                             | Power saving                             |     | -78  |     | dBFS  |

|                                             | Voice wake up                            |     | -78  |     | dBFS  |

| Offset Error                                |                                          |     | ±0.3 |     | mV    |

| Gain Error                                  |                                          |     | ±0.2 |     | dB    |

| Interchannel Isolation                      | CM capacitor = 1 µF                      |     | 100  |     | dB    |

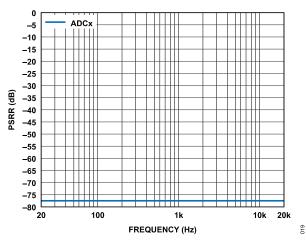

| Power Supply Rejection Ratio (PSRR)         | CM capacitor = 1 µF                      |     |      |     |       |

|                                             | 100 mV p-p at 1 kHz                      |     | 60   |     | dB    |

|                                             | 100 mV p-p at 10 kHz                     |     | 40   |     | dB    |

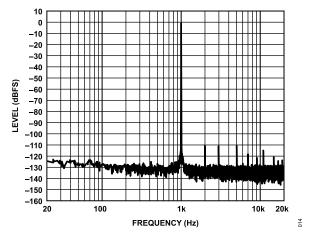

| DIFFERENTIAL LINE INPUT                     | PGAx_EN = 0, PGAx_SLEW_DIS = 1           |     |      |     |       |

| Full-Scale Input Voltage                    | 0 dBFS                                   |     | 0.98 |     | V rms |

|                                             | 0 dBFS                                   |     | 2.78 |     | V p-p |

| Dynamic Range <sup>1</sup>                  | 20 Hz to 20 kHz, -60 dB input            |     |      |     |       |

| With A-Weighted Filter (RMS)                | Enhanced performance                     |     | 106  |     | dB    |

|                                             | Normal performance                       |     | 106  |     | dB    |

|                                             | Power saving                             |     | 105  |     | dB    |

|                                             | Voice wake up                            |     | 100  |     | dB    |

| With Flat 20 Hz to 20 kHz Filter            | Enhanced performance                     |     | 100  |     | dB    |

|                                             | Normal performance                       |     | 104  |     | dB    |

|                                             |                                          |     | 104  |     | dB    |

|                                             | Power saving                             |     |      |     |       |

|                                             | Voice wake up                            |     | 98   |     | dB    |

| SNR <sup>2</sup>                            | Falsan and a structure                   |     | 400  |     |       |

| With A-Weighted Filter (RMS)                | Enhanced performance                     |     | 106  |     | dB    |

|                                             | Normal performance                       |     | 106  |     | dB    |

|                                             | Power saving                             |     | 104  |     | dB    |

|                                             | Voice wake up                            |     | 99   |     | dB    |

| With Flat 20 Hz to 20 kHz Filter            | Enhanced performance                     |     | 103  |     | dB    |

|                                             | Normal performance                       |     | 103  |     | dB    |

|                                             | Power saving                             |     | 102  |     | dB    |

|                                             | Voice wake up                            |     | 98   |     | dB    |

| Interchannel Gain Mismatch                  |                                          |     | 40   |     | mdB   |

| THD + N                                     | 20 Hz to 20 kHz, -1 dB full-scale output |     |      |     |       |

|                                             | Enhanced performance                     |     | -95  |     | dBFS  |

|                                             | Normal performance                       |     | -95  |     | dBFS  |

|                                             | Power saving                             |     | -95  |     | dBFS  |

|                                             | Voice wake up                            |     | -95  |     | dBFS  |

| Offset Error                                |                                          |     | ±0.2 |     | mV    |

| Gain Error                                  |                                          |     | ±0.2 |     | dB    |

| Interchannel Isolation                      | CM capacitor = 1 µF                      |     | 100  |     | dB    |

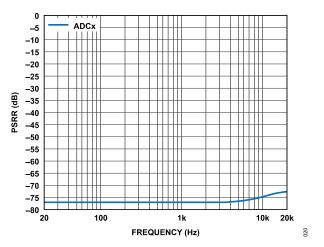

| PSRR                                        | CM capacitor = 1 µF                      |     |      |     |       |

|                                             | 100 mV p-p at 1 kHz                      |     | 70   |     | dB    |

|                                             | 100 mV p-p at 10kHz                      |     | 70   |     | dB    |

#### **SPECIFICATIONS**

#### Table 1. (Continued)

| Parameter                           | Test Conditions/Comments      | Min | Тур       | Мах | Unit     |

|-------------------------------------|-------------------------------|-----|-----------|-----|----------|

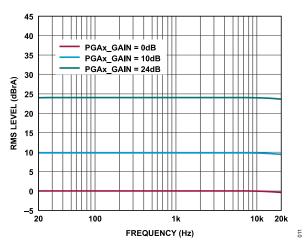

| SINGLE-ENDED PGA INPUT              | PGAx_EN = 1                   |     |           |     |          |

| Full-Scale Input Voltage            | 0 dBFS                        |     | 0.49      |     | V rms    |

|                                     | 0 dBFS                        |     | 1.39      |     | V p-p    |

| Dynamic Range <sup>1</sup>          | 20 Hz to 20 kHz, -60 dB input |     |           |     |          |

| With A-Weighted Filter (RMS)        | Enhanced performance          |     | 100       |     | dB       |

|                                     | Normal performance            |     | 100       |     | dB       |

|                                     | Power saving                  |     | 99        |     | dB       |

|                                     | Voice wake up                 |     | 97        |     | dB       |

| With Flat 20 Hz to 20 kHz Filter    | Enhanced performance          |     | 96        |     | dB       |

|                                     | Normal performance            |     | 96        |     | dB       |

|                                     | Power saving                  |     | 96        |     | dB       |

|                                     | Voice wake up                 |     | 94        |     | dB       |

| SNR <sup>2</sup>                    |                               |     |           |     |          |

| With A-Weighted Filter (RMS)        | Enhanced performance          |     | 100       |     | dB       |

| 5 ( )                               | Normal performance            |     | 100       |     | dB       |

|                                     | Power saving                  |     | 99        |     | dB       |

|                                     | Voice wake up                 |     | 97        |     | dB       |

| With Flat 20 Hz to 20 kHz Filter    | Enhanced performance          |     | 96        |     | dB       |

|                                     | Normal performance            |     | 96        |     | dB       |

|                                     | Power saving                  |     | 96        |     | dB       |

|                                     | Voice wake up                 |     | 94        |     | dB       |

| THD + N                             | 20 Hz to 20 kHz, -1 dBFS      |     | •         |     |          |

|                                     | Enhanced performance          |     | -78       |     | dBFS     |

|                                     | Normal performance            |     | -78       |     | dBFS     |

|                                     | Power saving                  |     | -78       |     | dBFS     |

|                                     | Voice wake up                 |     | -78       |     | dBFS     |

| PGA Gain Range                      |                               | 0   | 10        | 24  | dB       |

| PGA Gain Variation                  |                               | Ů   |           |     | 40       |

| With 0 dB Setting                   | Standard deviation            |     | 0.05      |     | dB       |

| With 24 dB Setting                  | Standard deviation            |     | 0.15      |     | dB       |

| Interchannel Gain Mismatch          |                               |     | 40        |     | mdB      |

| Offset Error                        |                               |     | 0.3       |     | mV       |

| Gain Error                          |                               |     | ±0.2      |     | dB       |

| Interchannel Isolation              | CM capacitor = 1 µF           |     | 83        |     | dB       |

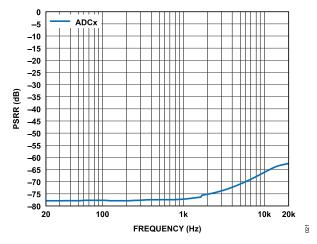

| PSRR                                | CM capacitor = 1 $\mu$ F      |     | 00        |     | uD       |

|                                     | 100 mV p-p at 1 kHz           |     | 70        |     | dB       |

|                                     | 100 mV p-p at 10 kHz          |     | 50        |     | dB       |

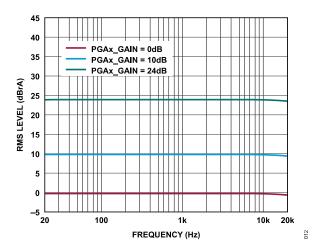

| IFFERENTIAL PGA INPUT               | PGAx_EN = 1                   |     |           |     |          |

| Full-Scale Input Voltage            | 0 dBFS                        |     | 0.98      |     | V rms    |

|                                     | 0 dBFS                        |     | 2.78      |     | V p-p    |

| Dynamic Range <sup>1</sup>          | 20 Hz to 20 kHz, -60 dB input |     | 2.70      |     | V P-P    |

| With A-Weighted Filter (RMS)        | Enhanced performance          |     | 103       |     | dB       |

| Will A-Weighted Filter (NWO)        | Normal performance            |     | 103       |     | dB       |

|                                     | Power saving                  |     | 103       |     | dB       |

|                                     | Voice wake up                 |     | 97        |     | dB       |

| With Flat 20 Hz to 20 kHz Filter    | Enhanced performance          |     | 97<br>101 |     | dB       |

| אאונוז רומנ בט דוב נט בט גחב רוונטו |                               |     | 101       |     | dВ       |

|                                     | Normal performance            |     |           |     | dB<br>dB |

|                                     | Power saving                  |     | 100       |     |          |

|                                     | Voice wake up                 |     | 96        |     | dB       |

### ADAU1860/ADAU1860-1

#### **SPECIFICATIONS**

#### Table 1. (Continued)

| Parameter                          | Test Conditions/Comments                                          | Min    | Тур          | Max        | Unit        |

|------------------------------------|-------------------------------------------------------------------|--------|--------------|------------|-------------|

| SNR <sup>2</sup>                   |                                                                   |        |              |            |             |

| With A-Weighted Filter (RMS)       | Enhanced performance                                              |        | 102          |            | dB          |

|                                    | Normal performance                                                |        | 102          |            | dB          |

|                                    | Power saving                                                      |        | 102          |            | dB          |

|                                    | Voice wake up                                                     |        | 97           |            | dB          |

| With Flat 20 Hz to 20 kHz Filter   | Enhanced performance                                              |        | 100          |            | dB          |

|                                    | Normal performance                                                |        | 100          |            | dB          |

|                                    | Power saving                                                      |        | 100          |            | dB          |

|                                    | Voice wake up                                                     |        | 95           |            | dB          |

| THD + N                            | 20 Hz to 20 kHz, -1 dBFS                                          |        |              |            |             |

|                                    | Enhanced performance                                              |        | -95          |            | dBFS        |

|                                    | Normal performance                                                |        | -95          |            | dBFS        |

|                                    | Power saving                                                      |        | -95          |            | dBFS        |

|                                    | Voice wake up                                                     |        | -95          |            | dBFS        |

| PGA Gain Range                     |                                                                   | 0      | 00           | 24         | dB          |

| PGA Gain Variation                 |                                                                   |        |              | <b>L</b> T |             |

| With 0 dB Setting                  | Standard deviation                                                |        | 0.05         |            | dB          |

| With 24 dB Setting                 | Standard deviation                                                |        | 0.05         |            | dB          |

| Interchannel Gain Mismatch         |                                                                   |        | 40           |            | mdB         |

| Offset Error                       |                                                                   |        | 40<br>±0.2   |            | mV          |

| Gain Error                         |                                                                   |        | ±0.2<br>±0.2 |            | dB          |

| Interchannel Isolation             | CM conseiter = 1 uF                                               |        |              |            | dB          |

|                                    | CM capacitor = 1 µF                                               |        | 100          |            | uБ          |

| PSRR                               | CM capacitor = $1 \mu F$                                          |        | 70           |            | чD          |

|                                    | 100 mV p-p at 1 kHz                                               |        | 70<br>70     |            | dB          |

|                                    | 100 mV p-p at 10 kHz                                              |        | 70           |            | dB          |

| IGITAL-TO-ANALOG CONVERTERS (DACs) |                                                                   |        |              |            | <b>D</b> ., |

| Internal Converter Resolution      | All digital-to-analog converters                                  |        | 24           |            | Bits        |

| Digital Gain                       |                                                                   |        |              |            |             |

| Step                               |                                                                   |        | 0.375        |            | dB          |

| Range                              |                                                                   | -71.25 |              | +24        | dB          |

| Ramp Rate                          |                                                                   |        | 4.5          |            | dB/ms       |

| AC DIFFERENTIAL OUTPUT             | Differential operation                                            |        |              |            |             |

| Full-Scale Output Voltage          | 0 dBFS to DAC                                                     |        | 1.0          |            | V rms       |

| Dynamic Range <sup>1</sup>         | 20 Hz to 20 kHz, -60 dB input                                     |        |              |            |             |

| With A-Weighted Filter (RMS)       | Enhanced performance                                              |        | 110          |            | dB          |

|                                    | Normal performance                                                |        | 106          |            | dB          |

| With Flat 20 Hz to 20 kHz Filter   | Enhanced performance                                              |        | 107          |            | dB          |

|                                    | Normal performance                                                |        | 103          |            | dB          |

| SNR <sup>2</sup>                   | 20 Hz to 20 kHz                                                   |        |              |            |             |

| With A-Weighted Filter (RMS)       | Enhanced performance                                              |        | 110          |            | dB          |

|                                    | Normal performance                                                |        | 106          |            | dB          |

| With Flat 20 Hz to 20 kHz Filter   | Enhanced performance                                              |        | 106          |            | dB          |

|                                    | Normal performance                                                |        | 103          |            | dB          |

| Output Noise                       | 20 Hz to 20 kHz                                                   |        |              |            |             |

| With A-Weighted Filter (RMS)       |                                                                   |        | 3.15         |            | μV          |

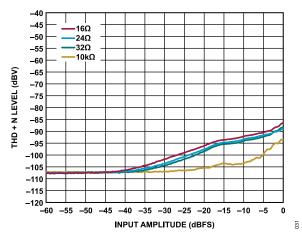

| THD + N Level                      | Headphone mode                                                    |        |              |            |             |

| 32 Ω Load                          | -15 dBFS input, output power (P <sub>OUT</sub> ) = 1 mW, enhanced |        | -96          |            | dBV         |

|                                    | performace                                                        |        |              |            |             |

|                                    |                                                                   |        | -85          |            | dBV         |

### ADAU1860/ADAU1860-1

#### **SPECIFICATIONS**

#### Table 1. (Continued)

| Parameter                    | Test Conditions/Comments                                       | Min  | Тур    | Max  | Unit |

|------------------------------|----------------------------------------------------------------|------|--------|------|------|

|                              | -1 dBFS input, enhanced performance                            |      | -89    |      | dBV  |

|                              | -1 dBFS input, normal performance                              |      | -80    |      | dBV  |

| 24 Ω Load                    | -2 dBFS input, enhanced performance                            |      | -89    |      | dBV  |

|                              | -2 dBFS input, normal performance                              |      | -80    |      | dBV  |

| 16 Ω Load                    | -3 dBFS input, enhanced performance                            |      | -89    |      | dBV  |

|                              | -3 dBFS input, normal performance                              |      | -80    |      | dBV  |

| THD + N Ratio <sup>3</sup>   | Headphone mode                                                 |      |        |      |      |

| 10 kΩ Load                   | -1 dBFS input, normal performance                              |      | -95    |      | dB   |

| 300 Ω Load                   | -1 dBFS input, enhanced performance                            |      | -93    |      | dB   |

| 600 Ω Load                   | -1 dBFS input, enhanced performance                            |      | -93    |      | dB   |

| Headphone Output Power       |                                                                |      |        |      |      |

| 32 Ω Load                    | AVDD = 1.8 V, <0.1% THD + N                                    |      | 30     |      | mW   |

| 24 Ω Load                    | AVDD = 1.8 V, <0.1% THD + N                                    |      | 40     |      | mW   |

| 16 Ω Load                    | AVDD = 1.8 V, <0.1% THD + N                                    |      | 50     |      | mW   |

| Gain Error                   |                                                                |      | ±2.5   |      | %    |

| DC Offset                    |                                                                |      | ±0.1   |      | mV   |

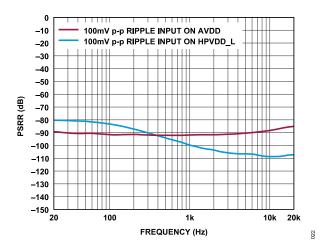

| PSRR                         | CM capacitor = 1 µF                                            |      |        |      |      |

| HPVDD                        | 100 mV p-p at 1 kHz                                            |      | 85     |      | dB   |

|                              | 100 mV p-p at 10 kHz                                           |      | 85     |      | dB   |

| HPVDD_L (LDO Bypass)         | 100 mV p-p at 1 kHz                                            |      | 90     |      | dB   |

|                              | 100 mV p-p at 10 kHz                                           |      | 90     |      | dB   |

| AVDD Undervoltage Trip Point |                                                                |      | 1.5    |      | V    |

| CM REFERENCE                 | CM pin                                                         |      |        |      |      |

| Output                       |                                                                |      | 0.85   |      | V    |

| Source Impedance             |                                                                |      | 5      |      | kΩ   |

| PHASE LOCKED LOOP (PLL)      |                                                                |      |        |      |      |

| Input Frequency              | After input prescale                                           | 0.03 |        | 36   | MHz  |

| Output Frequency             |                                                                | 24   | 49.152 | 100  | MHz  |

| Fractional Limits            | Fractional mode, fraction part (numerator (N)/denominator (M)) | 0.1  |        | 0.9  |      |

| Integer Limits               | Fractional mode, integer part                                  | 2    |        | 3072 |      |

| Lock Time                    | 32 kHz input                                                   |      | 6.5    |      | ms   |

|                              | 24.576 MHz input                                               |      | 0.46   | 0.55 | ms   |

| REGULATOR                    |                                                                |      |        |      |      |

| Line Regulation              |                                                                |      | 1      |      | mV/V |

| Load Regulation              |                                                                |      | 0.5    |      | mV/m |

<sup>1</sup> Dynamic range is the ratio of the sum of noise and harmonic power in the band of interest with a -60 dBFS signal present to the full-scale power level in decibels.

<sup>2</sup> SNR is the ratio of the sum of all noise power in the band of interest with no signal present to the full-scale power level in decibels.

<sup>3</sup> 25°C with DAC\_MORE\_FILT, DAC\_LPM enabled with A-weighted filter used.

#### **CRYSTAL AMPLIFIER SPECIFICATIONS**

Supply voltages: AVDD = IOVDD = 1.8 V, and DVDD = 0.9 V, unless otherwise noted.

| Table 2.         |     |     |     |      |

|------------------|-----|-----|-----|------|

| Parameter        | Min | Тур | Max | Unit |

| JITTER           |     | 270 | 500 | ps   |

| FREQUENCY RANGE  | 1   |     | 36  | MHz  |

| LOAD CAPACITANCE |     |     | 20  | pF   |

#### **SPECIFICATIONS**

#### DIGITAL INPUT AND OUTPUT SPECIFICATIONS

$-40^{\circ}$ C < T<sub>A</sub> < +85°C, and IOVDD = 1.1 V to 1.98 V, unless otherwise noted.

#### Table 3.

| Parameter           | Symbols         | Test Conditions/Comments                                           | Min         | Тур          | Max         | Unit |

|---------------------|-----------------|--------------------------------------------------------------------|-------------|--------------|-------------|------|

| INPUT VOLTAGE       |                 |                                                                    |             |              |             |      |

| High                | V <sub>IH</sub> |                                                                    | 0.7 × IOVDD |              |             | V    |

| Low                 | VIL             |                                                                    |             |              | 0.3 × IOVDD | V    |

|                     | I <sub>IH</sub> | IOVDD = 1.8 V, input high current ( $I_{IH}$ ) at $V_{IH}$ = 1.1 V |             |              | 10          | μA   |

|                     | I <sub>IL</sub> | Input low current ( $I_{IL}$ ) at $V_{IL}$ = 0.45 V                |             |              | 10          | μA   |

| OUTPUT VOLTAGE HIGH | V <sub>OH</sub> |                                                                    |             |              |             |      |

| Drive Strength      |                 |                                                                    |             |              |             |      |

| Low                 |                 | Output high current (I <sub>OH</sub> ) = 1 mA                      | 0.7 × IOVDD | 0.83 × IOVDD |             | V    |

| High                |                 | I <sub>OH</sub> = 3 mA                                             | 0.7 × IOVDD | 0.83 × IOVDD |             | V    |

| OUTPUT VOLTAGE LOW  | V <sub>OL</sub> |                                                                    |             |              |             |      |

| Drive Strength      |                 |                                                                    |             |              |             |      |

| Low                 |                 | Output low current (I <sub>OL</sub> ) = 1 mA                       |             | 0.1 × IOVDD  | 0.3 × IOVDD | V    |

| High                |                 | Output low current (I <sub>OL</sub> ) = 3 mA                       |             | 0.1 × IOVDD  | 0.3 × IOVDD | V    |

| NPUT CAPACITANCE    |                 |                                                                    |             |              | 5           | pF   |

#### POWER SUPPLY SPECIFICATIONS

Supply voltages: AVDD = HPVDD = IOVDD = 1.8 V and DVDD = 0.9 V, unless otherwise noted. PLL disabled, direct master clock. Digital input/output (I/O) lines loaded with 25 pF.

#### Table 4.

| Parameter       | Test Conditions/Comments | Min  | Тур | Max   | Unit |

|-----------------|--------------------------|------|-----|-------|------|

| SUPPLIES        |                          |      |     |       |      |

| AVDD Voltage    |                          | 1.7  | 1.8 | 1.98  | V    |

| DVDD Voltage    |                          | 0.85 | 0.9 | 1.21  | V    |

| IOVDD Voltage   |                          | 1.1  | 1.8 | 1.98  | V    |

| HPVDD Voltage   |                          | 1.7  | 1.8 | 1.98  | V    |

| HPVDD_L Voltage |                          | 1.2  |     | HPVDD | V    |

#### **POWER-DOWN CURRENT**

Supply voltages: AVDD = HPVDD = IOVDD = 1.8 V and DVDD = 0.9 V and was externally supplied. PLL and crystal oscillator was disabled and bypassed.

Table 5.

|                                  | AVDI | AVDD + HPVDD Current |     | DVDD Current |      | IOVDD Current |     |     | HPVDD_L Current |     |     |     |      |

|----------------------------------|------|----------------------|-----|--------------|------|---------------|-----|-----|-----------------|-----|-----|-----|------|

| Parameter                        | Min  | Тур                  | Max | Min          | Тур  | Max           | Min | Тур | Max             | Min | Тур | Мах | Unit |

| POWER-DOWN CURRENT               |      |                      |     |              |      |               |     |     |                 |     |     |     |      |

| PD Pin Low (Hardware Power Down) |      | 6.6                  |     |              | 56.9 |               |     | 2.6 |                 |     | 3   |     | μA   |

| PWR_MODE = 00                    |      |                      |     |              |      |               |     |     |                 |     |     |     |      |

| CM_KEEP_ALIVE = 0                |      | 11                   |     |              | 258  |               |     | 21  |                 |     | 3   |     | μA   |

| CM_KEEP_ALIVE = 1                |      | 588                  |     |              | 258  |               |     | 21  |                 |     | 3   |     | μA   |

#### **SPECIFICATIONS**

#### TYPICAL POWER CONSUMPTION

PLL bypassed with a master clock = 24.576 MHz (external oscillator). DVDD = 0.9 V, and AVDD = HPVDD = IOVDD = 1.8 V was supplied externally. Where applicable, ADC0 and ADC1 were run at 192 kHz, and ADC2 was run at 48 kHz. FastDSP<sup>TM</sup> was run at 192 kHz (biquad filters with 27-bit precision), and Tensilica DSP was run at 48 kHz. DAC was run at 192 kHz, and DAC\_LPM = 0. One serial port input and output, configured as a slave, with a headphone load of 32  $\Omega$  was used. The DAC headphone amplifier (HPAMP) was in normal voltage mode. Quiescent current had no signal.

In Table 6, ASRCI and ASRCO are the input and output ports of the asynchronous sample rate converters, FIFO is first in, first out, DMIC is the digital microphone, and PDM is the pulse density modulation.

Table 6.

| ADC + PGA<br>Channels           | DAC<br>Channels | ASRCI/<br>ASRCO<br>Channels | FIFO and<br>SRAM2 | FastDSP<br>Instructions | Equalizer<br>Filters | DMIC/PDM<br>Channels | Interpolator<br>/ Decimator<br>Channels | AVDD +<br>HPVDD<br>Current<br>(mA) | DVDD<br>Current<br>(mA) | IOVDD<br>Current<br>(mA) | HPVDD_L<br>Current<br>(mA) |

|---------------------------------|-----------------|-----------------------------|-------------------|-------------------------|----------------------|----------------------|-----------------------------------------|------------------------------------|-------------------------|--------------------------|----------------------------|

| 0                               | 1               | 1/0                         | N                 | 0                       | 13                   | 0                    | 0                                       | 0.99                               | 1.09                    | 0.15                     | 0.003                      |

| 2                               | 1               | 0                           | N                 | 32                      | 13                   | 0                    | 0                                       | 2.18                               | 1.87                    | 0.15                     | 0.003                      |

| 2                               | 1               | 1/0                         | N                 | 32                      | 13                   | 0                    | 0                                       | 2.18                               | 2.54                    | 0.15                     | 0.003                      |

| 1                               | 1               | 1/1                         | N                 | 0                       | 13                   | 0                    | 0                                       | 1.76                               | 1.30                    | 0.22                     | 0.003                      |

| 3                               | 1               | 1/3                         | N                 | 32                      | 13                   | 0                    | 0                                       | 2.58                               | 3.04                    | 0.315                    | 0.003                      |

| 1 <sub>(Voice</sub> Wake<br>Up) | 0               | 0                           | Y                 | 0                       | 0                    | 0                    | 0                                       | 1.46                               | 1.56                    | 0.15                     | 0.003                      |

Typical active noise cancelling (ANC) settings (phone call with ANC). Master clock = 24.576 MHz (external oscillator and PLL bypassed). DVDD = 0.9 V, and AVDD = HPVDD = 10VDD = 1.8 V was supplied externally. The three ADCs were PGA enabled and configured for headphone input. The DAC was configured for differential headphone operation, and the DAC output was loaded with  $32 \Omega$ , and DAC\_LPM = 0. One serial port input and output, configured as slave, was used. One input and three output ASRCs were used. FastDSP was run at 24.576 MHz, 32 instructions (biquad filters with 27-bit precision) at 192 kHz. Tensilica DSP was bypassed, quiescent current had no signal, and the input signal level was -15 dBFS.

Table 7.

|                          |                        |                |                 | Туріса | al Current (mA) |         |                                    | Typical ADC                              | Typical Head-                                 |

|--------------------------|------------------------|----------------|-----------------|--------|-----------------|---------|------------------------------------|------------------------------------------|-----------------------------------------------|

| - I                      | Performance<br>Setting | Power Mode     | AVDD +<br>HPVDD | DVDD   | IOVDD           | HPVDD_L | Total Power<br>Consumption<br>(mW) | THD + N,<br>Differential<br>Mode (dB FS) | phone Output<br>THD + N (dBV),<br>1 mW Output |

| AVDD =<br>IOVDD = 1.8 V, | High                   | Normal voltage | 3.04            | 3.06   | 0.316           | 0.003   | 8.8                                | -95                                      | Not applicable<br>No load                     |

| DVDD = 0.9 V             |                        |                | 7.87            | 3.06   | 0.315           | 0.003   | 17.49                              | -95                                      | -96                                           |

|                          |                        | Low voltage    | 2.76            | 3.06   | 0.316           | 0.286   | 8.63                               | -95                                      | Not applicable<br>No load                     |

|                          |                        |                | 2.76            | 3.06   | 0.316           | 5.093   | 14.4                               | -95                                      | -96                                           |

|                          | Normal                 | Normal voltage | 2.58            | 3.06   | 0.316           | 0.003   | 7.97                               | -95                                      | Not applicable<br>No load                     |

|                          |                        |                | 7.41            | 3.06   | 0.316           | 0.003   | 16.66                              | -95                                      | -85                                           |

|                          |                        | Low voltage    | 2.32            | 3.06   | 0.316           | 0.257   | 7.8                                | -95                                      | Not applicable<br>No load                     |

|                          |                        |                | 2.32            | 3.06   | 0.316           | 5.071   | 13.58                              | -95                                      | -85                                           |

## ADAU1860/ADAU1860-1

#### **SPECIFICATIONS**

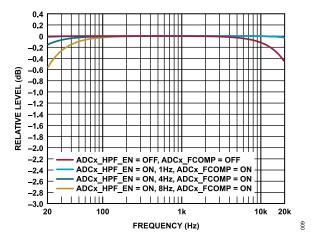

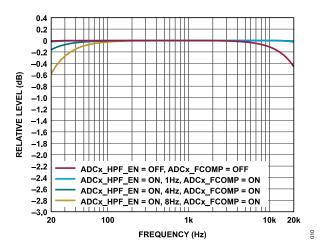

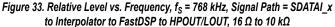

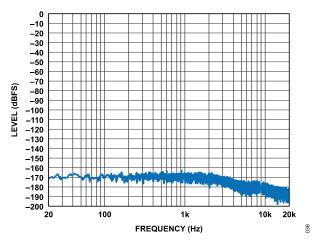

#### **DIGITAL FILTERS**

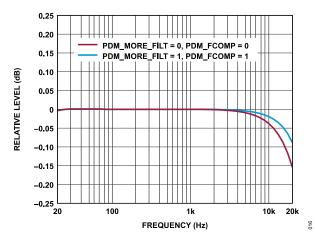

| Parameter                               | Test Conditions/Comments                                                                | Min  | Тур                     | Max                     | Unit |

|-----------------------------------------|-----------------------------------------------------------------------------------------|------|-------------------------|-------------------------|------|

| ADC INPUT TO DAC OUTPUT PATH            |                                                                                         |      |                         |                         |      |

| Pass-Band Ripple                        | DC to 20 kHz, sampling frequency ( $f_S$ ) = 192 kHz (ADC_FCOMP = 1, and DAC_FCOMP = 1) |      |                         | ±0.02                   | dB   |

| Group Delay                             | f <sub>S</sub> = 192 kHz                                                                |      | 12.9                    |                         | μs   |

|                                         | f <sub>S</sub> = 384 kHz                                                                |      | 7.5                     |                         | μs   |

|                                         | f <sub>S</sub> = 768 kHz                                                                |      | 5                       |                         | μs   |

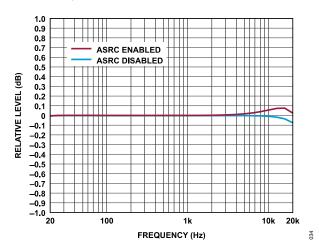

| SAMPLE RATE CONVERTER                   |                                                                                         |      |                         |                         |      |

| Pass Band                               | FSYNC < 63 kHz                                                                          |      |                         | 0.475 × f <sub>S</sub>  | kHz  |

|                                         | 63 kHz < FSYNC < 112 kHz                                                                |      |                         | 0.4286 × f <sub>S</sub> | kHz  |

|                                         | FSYNC > 112 kHz                                                                         |      | 0.2383 × f <sub>S</sub> | · · ·                   | kHz  |

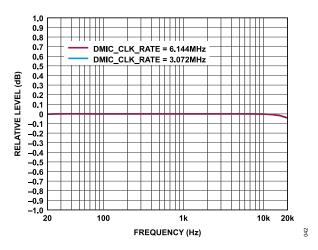

| Audio Band Ripple                       | 20 Hz to 20 kHz                                                                         | -0.1 |                         | +0.1                    | dB   |

| Input and Output Sample Frequency Range |                                                                                         | 7    |                         | 224                     | kHz  |

| Dynamic Range                           | ASRCx_LPM = 0                                                                           |      | 130                     |                         | dB   |

|                                         | ASRCx_LPM = 1                                                                           |      | 130                     |                         | dB   |

|                                         | ASRCx_LPM_II = 1                                                                        |      | 130                     |                         | dB   |

| THD + Noise                             | 20 Hz to 20 kHz, input is typical at 1 kHz and maximum at 20 kHz                        |      |                         |                         |      |

|                                         | ASCRx_LPM = 0                                                                           |      | -130                    | -120                    | dBF  |

|                                         | ASCRx_LPM = 1                                                                           |      | -120                    | -110                    | dBF  |

|                                         | ASCRx_LPM_II = 1                                                                        |      | -115                    | -90                     |      |

| Start-Up Time to Lock                   |                                                                                         |      |                         | 25                      | ms   |

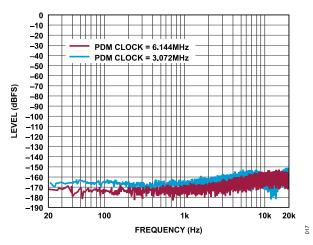

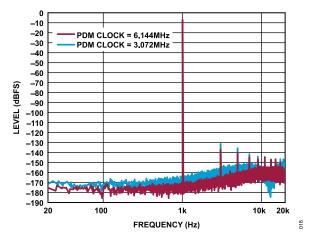

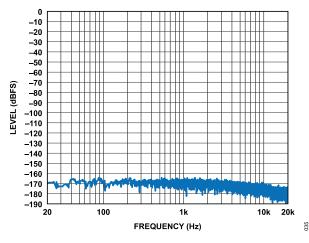

| PDM OUTPUTS                             |                                                                                         |      |                         |                         |      |

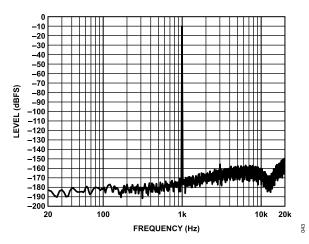

| Dynamic Range                           | 20 Hz to 20 kHz, with A-weighted filter                                                 |      | 126                     |                         | dBFS |

| THD + N                                 | 20 Hz to 20 kHz, –6 dBFS input                                                          |      | -125                    |                         | dBF  |

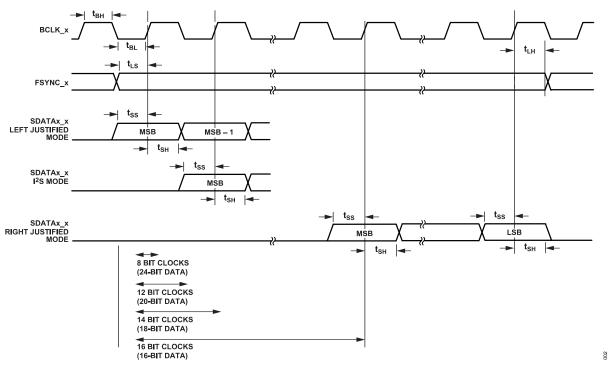

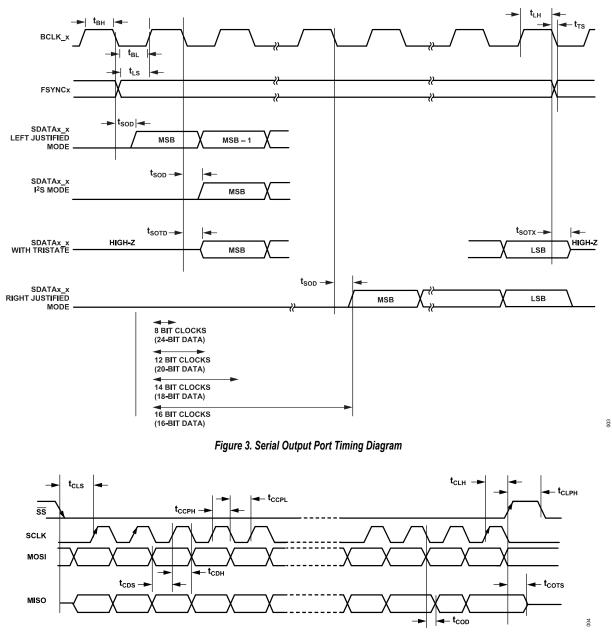

#### DIGITAL TIMING SPECIFICATIONS

$-40^{\circ}$ C < T<sub>A</sub> < +85°C, IOVDD = 1.1 V to 1.8 V, and DVDD = 0.9 V to 1.1 V, unless otherwise noted.

Table 9.

|                          |       | Limit            |      |                                                                 |

|--------------------------|-------|------------------|------|-----------------------------------------------------------------|

| Parameter                | Min   | Max              | Unit | Description                                                     |

| MASTER CLOCK             |       |                  |      | MCLKIN period                                                   |

| t <sub>MPI</sub>         | 0.037 | 33.3             | μs   | 30 kHz to 36 MHz input clock using PLL in integer mode          |

| t <sub>MPF</sub>         | 0.037 | 1.0              | μs   | 30 kHz to 36 MHz input clock using PLL in fractional mode       |

| AUDIO SERIAL PORT        |       |                  |      |                                                                 |

| t <sub>BL</sub>          | 18    |                  | ns   | BCLK_x low pulse width (master and slave modes)                 |

| t <sub>BH</sub>          | 18    |                  | ns   | BCLK_x high pulse width (master and slave modes)                |

| <b>f</b> BCLK            | 0.512 | 24.576           | MHz  | BCLK_x frequency                                                |

| t <sub>LS</sub>          | 3     |                  | ns   | FSYNC_x setup, time to BCLK_x rising (slave mode)               |

| t <sub>LH</sub>          | 5     |                  | ns   | FSYNC_x hold, time from BCLK_x rising (slave mode)              |

| <b>f</b> <sub>SYNC</sub> | 8     | 768 <sup>1</sup> | kHz  | FSYNC_x frequency                                               |

| t <sub>SS</sub>          | 3     |                  | ns   | SDATAI_x setup, time to BCLK_x rising (master and slave modes)  |

| t <sub>SH</sub>          | 10    |                  | ns   | SDATAI_x hold, time from BCLK_x rising (master and slave modes) |

| t <sub>TS</sub>          |       | 6                | ns   | BCLK_x falling to FSYNC_x timing skew (master mode)             |

#### **SPECIFICATIONS**

#### Table 9. (Continued)

|                                             |      | Limit                  |      |                                                                                            |

|---------------------------------------------|------|------------------------|------|--------------------------------------------------------------------------------------------|

| Parameter                                   | Min  | Max                    | Unit | Description                                                                                |

| tsod                                        | 0    | 16                     | ns   | SDATAO_x delay, time from BCLK_x falling (master and slave modes), IOVDD at 1.62 V minimum |

|                                             | 0    | 32                     | ns   | SDATAO_x delay, time from BCLK_x falling (master and slave modes), IOVDD at 1.1 V minimum  |

| t <sub>sotd</sub>                           | 0    | 16                     | ns   | BCLK_x falling to SDATAO_x driven in tristate mode                                         |

| t <sub>sotx</sub>                           | 0    | 16                     | ns   | BCLK_x falling to SDATAO_x tristated in tristate mode                                      |

| SERIAL PERIPHERAL INTEFACE (SPI)<br>PORT    |      |                        |      |                                                                                            |

| f <sub>SCLK</sub>                           |      | 24                     | MHz  | SCLK frequency                                                                             |

| t <sub>CCPL</sub>                           | 15   |                        | ns   | SCLK pulse width low                                                                       |

| t <sub>ССРН</sub>                           | 15   |                        | ns   | SCLK pulse width high                                                                      |

| t <sub>CLS</sub>                            | 4    |                        | ns   | SS setup, time to SCLK rising                                                              |

| t <sub>CLH</sub>                            | 18   |                        | ns   | SS hold, time from SCLK rising                                                             |

| t <sub>CLPH</sub>                           | 10   |                        | ns   | SS pulse width high                                                                        |

| t <sub>CDS</sub>                            | 8    |                        | ns   | MOSI setup, time to SCLK rising                                                            |

| t <sub>CDH</sub>                            | 6    |                        | ns   | MOSI hold, time from SCLK rising                                                           |

| t <sub>COD</sub>                            |      | 17                     | ns   | MISO delay, time from SCLK falling                                                         |

| t <sub>COTS</sub>                           |      | 24                     | ns   | MISO high-Z, time from SS rising                                                           |

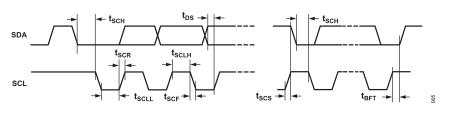

| I <sup>2</sup> C PORT                       |      |                        | _    |                                                                                            |

| f <sub>SCL</sub>                            |      | 1                      | MHz  | SCL frequency                                                                              |

| t <sub>SCLH</sub>                           | 0.26 |                        | μs   | SCL high                                                                                   |

| t <sub>SCLL</sub>                           | 0.5  |                        | μs   | SCL low                                                                                    |

| t <sub>scs</sub>                            | 0.26 |                        | μs   | SCL rise setup time (to SDA falling), relevant for repeated start condition                |

| t <sub>SCR</sub>                            |      | 120                    | ns   | SCL and SDA rise time, C <sub>LOAD</sub> = 400 pF                                          |

| t <sub>SCH</sub>                            | 0.26 |                        | μs   | SCL fall hold time (from SDA falling), relevant for start condition                        |

| t <sub>DS</sub>                             | 50   |                        | ns   | SDA setup time (to SCL rising)                                                             |

| t <sub>SCF</sub>                            |      | 120                    | ns   | SCL and SDA fall time, C <sub>LOAD</sub> = 400 pF                                          |

| t <sub>BFT</sub>                            | 0.5  |                        | μs   | SCL rise setup time (to SDA rising), relevant for stop condition                           |

| QSPI                                        |      |                        |      |                                                                                            |

| fqclk                                       |      | 50 <sup>2</sup>        | MHz  | QSPIM CLK frequency                                                                        |

| UART                                        |      |                        |      |                                                                                            |

|                                             |      | 1.152                  | Mbps | Baud rate                                                                                  |

| GENERAL-PURPOSE INPUT/OUTPUT<br>(GPIO) PINS |      |                        |      |                                                                                            |

| t <sub>GIL</sub>                            |      | 1.5 × 1/f <sub>S</sub> | μs   | MPx input latency, time until high or low value is read by core                            |

| t <sub>RLPW</sub>                           | 20   |                        | ns   | PD low pulse width                                                                         |

|                                             |      |                        |      | · - · · · · · · · · · · · · · · · · · ·                                                    |

| t <sub>CF</sub> <sup>3</sup>                |      | 12                     | ns   | Digital microphone clock fall time                                                         |

| t <sub>CR</sub> <sup>3</sup>                |      | 14                     | ns   | Digital microphone clock rise time                                                         |

| чск<br>t <sub>SETUP</sub>                   | 10   |                        | ns   | Digital microphone data setup time                                                         |

|                                             | 3    |                        | ns   | Digital microphone data hold time                                                          |

| t <sub>HOLD</sub>                           | 5    |                        | 113  |                                                                                            |

# ADAU1860/ADAU1860-1

#### SPECIFICATIONS

#### Table 9. (Continued)

|                              |     | Limit |      |                                    |

|------------------------------|-----|-------|------|------------------------------------|

| Parameter                    | Min | Max   | Unit | Description                        |

| PDM OUTPUT                   |     |       |      |                                    |

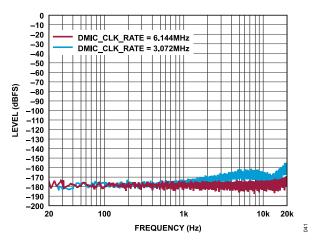

| f <sub>PDM_CLK</sub>         |     |       |      | PDM clock frequency                |

| -                            |     | 3.072 | MHz  | 3 MHz setting                      |

|                              |     | 6.144 | MHz  | 6 MHz setting                      |

| t <sub>CF</sub> <sup>3</sup> |     | 12    | ns   | Digital PDM clock output fall time |

| t <sub>CR</sub> <sup>3</sup> |     | 14    | ns   | Digital PDM clock output rise time |

| t <sub>HOLD</sub>            | 35  | 46    | ns   | PDM data hold time                 |

<sup>1</sup> Stereo, 16 bit per channel only at 768 kHz.

<sup>2</sup> Measured when IOVDD = 1.8 V house temperature.

<sup>3</sup> Digital microphone clock rise and fall times are measured at 2 mA drive strength with 25 pF load.

#### **Digital Timing Diagrams**

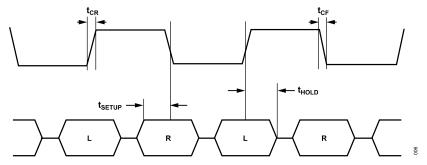

Figure 2. Serial Input Port Timing Diagram

#### SPECIFICATIONS

Figure 4. SPI Port Timing Diagram

Figure 5. I<sup>2</sup>C Port Timing Diagram

#### SPECIFICATIONS

Figure 6. Digital Microphone Timing Diagram

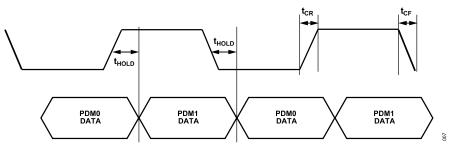

Figure 7. PDM Output Timing Diagram

#### ABSOLUTE MAXIMUM RATINGS

#### Table 10.

| Parameter                                      | Rating                 |

|------------------------------------------------|------------------------|

| Power Supply (AVDD, IOVDD, HPVDD, and HPVDD_L) | –0.3 V to +1.98 V      |

| Digital Supply (DVDD)                          | –0.3 V to +1.21 V      |

| Input Current (Except Supply Pins)             | ±20 mA                 |

| Analog Input Voltage (Signal Pins)             | -0.3 V to AVDD + 0.3 V |

| Digital Input Voltage (Signal Pins)            | -0.3 to IOVDD + 0.3 V  |

| Temperature                                    |                        |

| Operating Range (Case)                         | -40°C to +85°C         |

| Storage Range                                  | –65°C to +150°C        |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  and  $\theta_{JC}$  are determined according to JESD-51-9 on a 4-layer PCB with natural convection cooling.

#### Table 11. Thermal Resistance

| Package Type | θ <sub>JA</sub> 1 | θ <sub>JC</sub> 1 | Unit |

|--------------|-------------------|-------------------|------|

| CB-56-6      | 82.7              | 0.84              | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with two thermal vias. See JEDEC JESD-51.

#### ELECTROSTATIC DISCHARGE (ESD) RATINGS

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

#### ESD Ratings for the ADAU1860/ADAU1860-1

#### Table 12. ADAU1860/ADAU1860-1, 56-Ball WLCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 1000 V                  | 1C    |

| CDM       | 500 V                   | C2A   |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

800

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

|   |                  |                       |                  | ADAU1860//<br>TOP<br>(BALL SIE | VIEW            |                               |                                 |                      |

|---|------------------|-----------------------|------------------|--------------------------------|-----------------|-------------------------------|---------------------------------|----------------------|

|   | 1                | 2                     | 3                | 4                              | 5               | 6                             | 7                               | 8                    |

| A | ROM_BOOT_MODE/   | HPVDD_L               | DVDD             | DGND                           | TCK/<br>MP22    | TMS/<br>MP23                  | TDO/<br>MP24                    | TDI/<br>MP25         |

| в | SDATAO_0/<br>MP5 | BCLK_0/<br>MP3        | DVDD             | DGND                           | IOVDD           | XTALO                         | XTALI/<br>MCLKIN                | QSPIM_CLK/<br>MPT1   |

| с | SDATAL_0/<br>MP6 | FSYNC_0/<br>MP4       | DMIC23/<br>MP2   | DMIC_CLK/<br>MP0               | DMIC01/<br>MP1  | SDA/<br>MISO/<br>UART_CTRL_TX | SCL/<br>SCLK                    | QSPIM_SDIO0/<br>MP13 |

| D | HPVDD_L          | UART_COMM_<br>TX/MP17 | SDATAO_1/<br>MP9 | SDATAL_1/<br>MP10              | BCLK_1/<br>MP7  | ADDR0/SS                      | ADDR1/<br>MOSI/<br>UART_CTRL_RX | QSPIM_SDIO1/<br>MP14 |

| E | HPVDD            | UART_COMM_<br>RX/MP18 | IRQ/MP20         | D                              | FSYNC_1/<br>MP8 | SELFBOOT/<br>MP19             | QSPIM_SDIO3/<br>MP16            | QSPIM_SDIO2/<br>MP15 |

| F | HPGND            | HPOUTP                | REG_EN           | AINP2                          | AINP1           | AINPO                         | AVDD                            | QSPIM_CS/<br>MP12    |

| G | HPOUTN           | AVDD                  | AGND             | CM                             | AINN2           | AINN1                         | AGND                            | AINNO                |

#### Figure 8. Pin Configuration (Top View)

#### Table 13. Pin Function Descriptions

| Ball No. | Mnemonic           | Type <sup>1</sup> | Description                                                                                                                                                                                                         |

|----------|--------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1       | ROM_BOOT_MODE/MP21 | D_10              | ROM Boot-Up Mode. Use Boot-Up Mode 1 when connecting to IOVDD and use Boot-Up Mode 2 when connecting to ground.<br>Multipurpose I/O 21 (MP21).                                                                      |

| A2       | HPVDD_L            | PWR               | Power Supply for the Internal Low Dropout (LDO) Regulator and Headphone Amplifier Power.                                                                                                                            |

| A3       | DVDD               | PWR               | Digital Core Supply. The digital supply can be generated from an on-board regulator or supplied directly from an external supply. In each case, decouple DVDD to DGND with a 1 $\mu$ F and a 0.1 $\mu$ F capacitor. |

| A4       | DGND               | PWR               | Digital Ground. The AGND and DGND pins can be tied directly together in a common ground plane.                                                                                                                      |

| A5       | TCK/MP22           | D_IO              | JTAG Port Clock Input.<br>Multipurpose I/O 22 (MP22).                                                                                                                                                               |

| A6       | TMS/MP23           | D_IO              | JTAG Port Mode Selection.<br>Multipurpose I/O 23 (MP23).                                                                                                                                                            |

| A7       | TDO/MP24           | D_IO              | JTAG Port Data Output.<br>MultipPurpose I/O 24 (MP24).                                                                                                                                                              |

| A8       | TDI/MP25           | D_IO              | JTAG Port Data Input.<br>MultipPurpose I/O 25 (MP25).                                                                                                                                                               |