# ADIN1100BCPZ-R7 Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number ADIN1100BCPZ-R7-DG

Manufacturer Analog Devices Inc.

Manufacturer Product Number ADIN1100BCPZ-R7

Description IC TXRX FULL/HALF 1/1 40LFCSP

Detailed Description 1/1 Transceiver Full, Half Ethernet 40-LFCSP (6x6)

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

8542.39.0001

## **Purchase and inquiry**

| Manufacturer Product Number: | Manufacturer:                          |

|------------------------------|----------------------------------------|

| ADIN1100BCPZ-R7              | Analog Devices Inc.                    |

| Series:                      | Product Status:                        |

|                              | Active                                 |

| Type:                        | Protocol:                              |

| Transceiver                  | Ethernet                               |

| Number of Drivers/Receivers: | Duplex:                                |

| 1/1                          | Full, Half                             |

| Data Rate:                   | Voltage - Supply:                      |

| 10Mbps                       | 1V ~ 1.2V, 1.71V ~3.46V, 3.13V ~ 3.46V |

| Operating Temperature:       | Mounting Type:                         |

| -40°C ~ 105°C (TA)           | Surface Mount                          |

| Package / Case:              | Supplier Device Package:               |

| 40-WFQFN Exposed Pad, CSP    | 40-LFCSP (6x6)                         |

## **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 3 (168 Hours)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

## Data Sheet

## **ADIN1100**

## Robust, Industrial, Low Power 10BASE-T1L PHY

#### **FEATURES**

- ▶ 10BASE-T1L IEEE Standard 802.3cg-2019 compliant

- ▶ Cable reach up to 1700 m with 1.0 V p-p and 2.4 V p-p

- ▶ Supports 1.0 V p-p and 2.4 V p-p transmit levels

- MDI polarity detection and correction

- Supports intrinsic safety applications

- ▶ Low power consumption: 39 mW (dual supply, 1.0 V p-p)

- Diagnostics

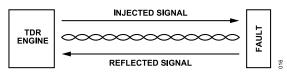

- ▶ Cable fault detection with TDR

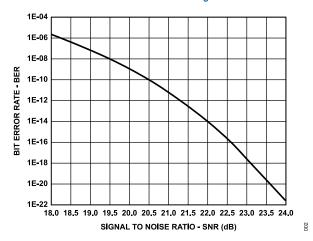

- ▶ Link quality indicator with MSE

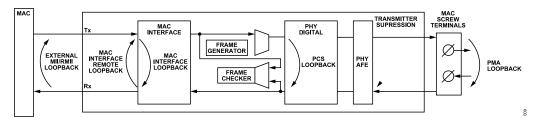

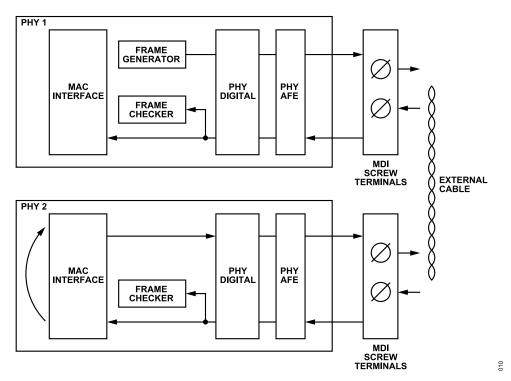

- ▶ Frame generator and checker

- ▶ Multiple loopback modes

- ▶ IEEE test mode support

- ▶ MII, RMII, and RGMII MAC interfaces

- ▶ MDIO management interface

- ▶ Unmanaged configuration using pin strapping

- ▶ 25 MHz crystal or external clock input (50 MHz for RMII)

- ▶ Single or dual supply with 1.8 V or 3.3 V operation

- ▶ 3.3 V, 2.5 V, or 1.8 V MAC interface VDDIO supply

- Integrated power supply monitoring and POR

- ▶ EMC test standards

- ▶ IEC 61000-4-4 EFT (±4 kV)

- ▶ IEC 61000-4-2 ESD (±4 kV contact discharge)

- ▶ IEC 61000-4-2 ESD (±8 kV air discharge)

- ► IEC 61000-4-5 surge (±4 kV)

- ► IEC 61000-4-6 conducted immunity (10 V/m)

- ▶ IEC 61000-4-3 radiated immunity (Class A)

- ► EN 55032 radiated emissions (Class B)

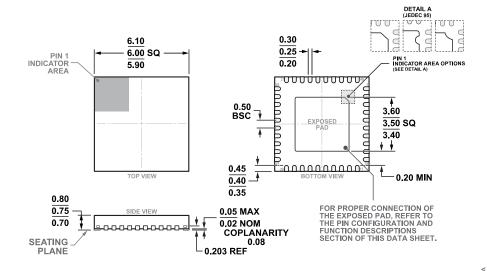

- ▶ Small package: 40-lead, 6 mm × 6 mm LFCSP

- ▶ Temperature range

- ▶ Industrial: -40°C to +85°C

- ► Extended: -40°C to +105°C

#### **APPLICATIONS**

- Process control

- Factory automation

- Building automation

- Field instruments and switches

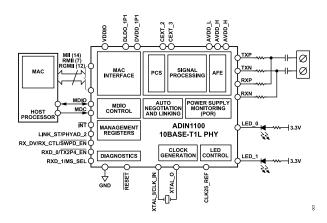

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **GENERAL DESCRIPTION**

The ADIN1100 is a low power, single port, 10BASE-T1L transceiver designed for industrial Ethernet applications and is compliant with the IEEE® 802.3cg-2019™ Ethernet standard for long reach 10 Mbps single pair Ethernet (SPE). The ADIN1100 integrates an Ethernet PHY core with all the associated analog circuitry, input and output clock buffering, the management interface control register and subsystem registers, as well as the MAC interface and control logic to manage the reset, clock control, and pin configuration.

The ADIN1100 supports cable reach of up to 1700 meters with autonegotiation enabled and has ultra low power consumption of 39 mW.

The PHY core supports the 1.0 V p-p operating mode and the 2.4 V p-p operating mode defined in the IEEE 802.3cg standard and can operate from a single power supply rail of 1.8 V or 3.3 V, with the lower voltage option supporting the 1.0 V p-p transmit voltage level.

The ADIN1100 has an integrated voltage supply monitoring circuit and power-on reset (POR) circuitry to improve system level robustness.

The MDIO interface is a 2-wire serial interface for communication between a host processor or MAC and the ADIN1100, thereby allowing access to control and status information in the PHY core management registers. This interface is compatible with both the IEEE 802.3 Standard Clause 22 and Clause 45 management frame structures.

Unmanaged PHY Operation.....27

## **TABLE OF CONTENTS**

Features......1

| Applications                                     | ·                                          |    |

|--------------------------------------------------|--------------------------------------------|----|

| Functional Block Diagram                         | 1 On-Chip Diagnostics                      | 30 |

| General Description                              | 1 Loopback Modes                           | 30 |

| Specifications                                   | . 5 Frame Generator and Checker            | 31 |

| Timing Characteristics                           | .8 Frame Generator and Checker Link Test   | 31 |

| Power-Up Timing                                  | 8 Test Modes                               | 33 |

| Management Interface Timing                      | 8 Time Domain Reflectometry (TDR)          | 33 |

| Absolute Maximum Ratings                         |                                            | 34 |

| Thermal Resistance                               |                                            |    |

| Electrostatic Discharge (ESD) Ratings            |                                            |    |

| ESD Caution                                      |                                            |    |

| Pin Configuration and Function Descriptions      | 10 Component Recommendations               | 40 |

| Typical Performance Characteristics              | 13 Electromagnetic Compatibility (EMC) and |    |

| Theory of Operation                              | 14 Electromagnetic Immunity (EMI)          | 42 |

| Power Supply Domains                             |                                            |    |

| MAC Interface                                    |                                            | 43 |

| Transmit Amplitude Configuration                 | 15 Clause 45                               | 44 |

| Leader/Follower Configuration                    |                                            | 45 |

| Autonegotiation                                  |                                            |    |

| Management Interface                             |                                            |    |

| Reset Operations2                                |                                            |    |

| Status LEDs                                      |                                            |    |

| Link Status Pin2                                 | •                                          |    |

| Power-Down Modes2                                | Component Placement and Routing            | 84 |

| Hardware Configuration Pins2                     |                                            |    |

| Overview2                                        |                                            |    |

| Unmanaged Applications2                          | 24 Outline Dimensions                      | 85 |

| Managed Applications2                            |                                            | 85 |

| Hardware Configuration Pins Functions            |                                            |    |

| Bringing Up 10BASE-T1L Links2                    |                                            |    |

| REVISION HISTORY                                 |                                            |    |

| 1/2025—Rev. B to Rev. C                          |                                            |    |

|                                                  | r (Throughout)                             |    |

|                                                  |                                            |    |

| •                                                |                                            |    |

|                                                  | d Receiver (RX) Latency Parameter, Table 2 |    |

|                                                  |                                            |    |

|                                                  |                                            |    |

|                                                  | ection                                     |    |

| •                                                | Section                                    |    |

| •                                                |                                            |    |

|                                                  |                                            |    |

| •                                                | equentially                                |    |

|                                                  | Section                                    |    |

|                                                  |                                            |    |

| Added Signal-to-Noise Ratio and Bit Error Rate S | Section and Figure 19                      | 35 |

## **TABLE OF CONTENTS**

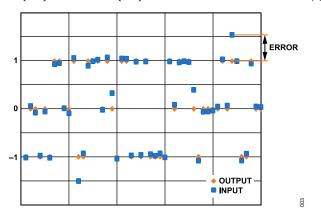

| Added Mean Squared Error at PHY Slicer Section and Figure 20                            | 35 |

|-----------------------------------------------------------------------------------------|----|

| Added MSE Reading Section                                                               |    |

| Added MSE Interpretation Section, Table 27, and Table 28; Renumbered Sequentially       | 36 |

| Added PHY Slicer Spikes and Errors Section                                              |    |

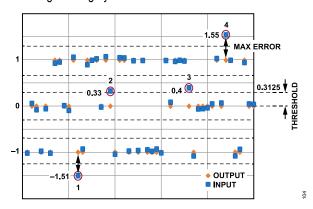

| Added Slicer Maximum Absolute Error Section and Figure 21                               | 36 |

| Added Slicer Error Spike Counter Section                                                |    |

| Added Relevant Register Information Section                                             |    |

| Added Register Configuration Section, Table 29, and Table 30                            | 37 |

| Changes to Table 31 Title                                                               |    |

| Change to Table 113                                                                     | 73 |

| 8/2023—Rev. A to Rev. B                                                                 |    |

| Changes to General Description Section                                                  | 1  |

| 1/2023—Rev. 0 to Rev. A                                                                 |    |

| Changes to Features Section                                                             |    |

| Changes to Clock Input Voltage Range Parameter; Table 1                                 | 5  |

| Changes to Table 2                                                                      |    |

| Changes to Single-Supply Applications Section                                           |    |

| Changes to Long Reach and Trunk/Spur Applications Section                               |    |

| Changes to High Voltage Transmit Level Request Advertisement Section                    |    |

| Changes to Determination of Transmit Level Resolution Section                           |    |

| Change to Table 11                                                                      |    |

| Changes to Master/Slave Advertisement Section                                           |    |

| Changes to Forced Master/Slave Configuration Advertisement Section                      |    |

| Changes to Determination of Master/Slave Configuration Section                          |    |

| Changes to Autonegotiation Fail Section                                                 |    |

| Changes to Power-On Reset Section                                                       |    |

| Changes to Overview Section                                                             |    |

| Changes to Table 13                                                                     |    |

| Changes to LED Pin Multiplexing Section                                                 |    |

| Changes to Power-Down Modes Section                                                     |    |

| Changes to Overview Section and Table 14                                                |    |

| Changes to Table 17                                                                     |    |

| Changes to Transmit Amplitude Section                                                   |    |

| Changes to Set Transmit Amplitude Level Section                                         |    |

| Change to Disable Software Power-Down Mode After Reset Section                          |    |

| Changes to Enable 1.0 V p-p Transmit Level Only Section                                 |    |

| Changes to Set 2.4 V p-p Transmit Level as Preferred Section                            |    |

| Changes to Read Link Partner Advertised Transmit Level Section                          |    |

| Change to Completion of Autonegotiation Section                                         |    |

| Added Time Domain Reflectometry (TDR) Section and Figure 16; Renumbered Sequentially    |    |

| Added Fault Detection with the TDR Engine Section                                       |    |

| Added TDR Offset Calibration Section                                                    |    |

| Added Cable Calibration Section                                                         |    |

| Added Length/Distance to Fault Accuracy Section                                         |    |

| Changes to Component Recommendations Section                                            | 40 |

| Changed Crystal Section to External Crystal Oscillator for RMII and RGMII Modes Section |    |

| Deleted External Clock Input Section and Figure 23; Renumbered Sequentially             | 40 |

## **TABLE OF CONTENTS**

| Added External 25 MHz Clock Input for MII and RGMII Modes Section, Figure 24, and Table 27; |    |

|---------------------------------------------------------------------------------------------|----|

| Renumbered Sequentially                                                                     | 40 |

| Added External 50 MHz Clock Input for RMII Mode Section, Figure 25, and Table 28            | 41 |

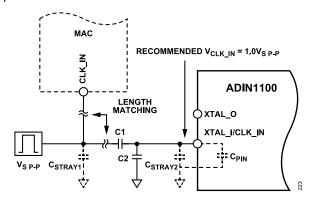

| Added PCB Parasitic Capacitance Considerations Section and Table 29                         | 41 |

| Changed Register Summary Section to MDIO Interface Section                                  | 43 |

| Added Register Summary Section                                                              | 46 |

| Change to Table 44                                                                          | 48 |

| Change to Frame Checker False Carrier Count Register Section                                | 80 |

| Change to Frame Checker Odd Nibble Frame Count Register Section                             | 80 |

| Changes to Ordering Guide                                                                   | 85 |

9/2021—Revision 0: Initial Version

analog.com Rev. C | 4 of 85

## **SPECIFICATIONS**

AVDD\_H = AVDD\_L = VDDIO = 3.3 V; DVDD\_1P1 from internal low dropout (LDO) regulator (DVDD\_1P1 = DLDO\_1P1); all specifications at -40°C to +105°C, unless otherwise noted.

Table 1. General Specifications

| Table 1. General Specifications  Parameter                                           | Min         | Тур   | Max         | Unit  | Test Conditions/Comments                                                                             |

|--------------------------------------------------------------------------------------|-------------|-------|-------------|-------|------------------------------------------------------------------------------------------------------|

| DIGITAL INPUTS/OUTPUTS                                                               |             | 1,7,0 | ША          |       | Applies to MAC interface pins, MDC, MDIO, INT, LINK_ST/PHYAD_2, RESET, and LED_x                     |

| VDDIO = 3.3 V                                                                        |             |       |             |       | _                                                                                                    |

| Input Low Voltage (V <sub>IL</sub> )                                                 |             |       | 0.8         | V     |                                                                                                      |

| Input High Voltage (V <sub>IH</sub> )                                                | 2.0         |       |             | V     |                                                                                                      |

| Output Low Voltage (V <sub>OI</sub> )                                                |             |       | 0.4         | V     | Output low current (I <sub>OL</sub> ) (minimum) = 2 mA                                               |

| Output High Voltage (V <sub>OH</sub> )                                               | 2.4         |       |             | V     | Output high current (I <sub>OH</sub> ) (minimum) = 2 mA                                              |

| VDDIO = 2.5 V                                                                        |             |       |             |       | T 0 (on)                                                                                             |

| $V_{IL}$                                                                             |             |       | 0.7         | V     |                                                                                                      |

| V <sub>IH</sub>                                                                      | 1.7         |       |             | V     |                                                                                                      |

| V <sub>OL</sub>                                                                      |             |       | 0.4         | V     | I <sub>OL</sub> (minimum) = 2 mA                                                                     |

| V <sub>OH</sub>                                                                      | 2.0         |       |             | V     | I <sub>OH</sub> (minimum) = 2 mA                                                                     |

| VDDIO = 1.8 V                                                                        |             |       |             |       | ,                                                                                                    |

| $V_{IL}$                                                                             |             |       | 0.3 × VDDIO | V     |                                                                                                      |

| V <sub>IH</sub>                                                                      | 0.7 × VDDIO |       |             | V     |                                                                                                      |

| V <sub>OL</sub>                                                                      |             |       | 0.2 × VDDIO | V     | I <sub>OL</sub> (minimum) = 2 mA                                                                     |

| V <sub>OH</sub>                                                                      | 0.8 × VDDIO |       |             | V     | I <sub>OH</sub> (minimum) = 2 mA                                                                     |

| RESET Deglitch Time                                                                  | 0.3         | 0.5   | 1           | μs    | ,                                                                                                    |

| LED/LINK STATUS OUTPUT                                                               |             |       |             |       |                                                                                                      |

| Output Drive Current                                                                 |             |       | 8           | mA    | VDDIO = 3.3 V                                                                                        |

|                                                                                      |             |       | 6           | mA    | VDDIO = 2.5 V                                                                                        |

|                                                                                      |             |       | 4           | mA    | VDDIO = 1.8 V                                                                                        |

| CLOCKS                                                                               |             |       |             |       |                                                                                                      |

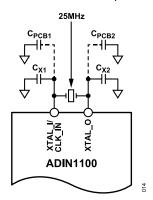

| External Crystal (XTAL)                                                              |             |       |             |       | Requirements for external crystal used on XTAL_I/CLK_IN pin and XTAL_O pin                           |

| Crystal Frequency                                                                    |             | 25    |             | MHz   |                                                                                                      |

| Crystal Frequency Tolerance                                                          | -30         |       | +30         | ppm   |                                                                                                      |

| Crystal Drive Level                                                                  |             | <200  |             | μW    |                                                                                                      |

| Crystal ESR                                                                          |             |       | 60          | Ω     |                                                                                                      |

| $\begin{array}{l} XTAL\_I, XTAL\_O \ Input \ Capacitance \\ (C_{IN,EQ}) \end{array}$ |             | 1.5   |             | pF    | Equivalent parallel differential input capacitance looking into XTAL_I/CLK_IN and XTAL_O pins        |

| Crystal Load Capacitance (C <sub>L</sub> ) <sup>1</sup>                              |             | 10    | 18          | pF    | Including PCB trace capacitance and XTAL_I, XTAL_O C <sub>IN.EQ</sub>                                |

| Start-Up Time                                                                        |             |       | 2           | ms    | Crystal oscillator only                                                                              |

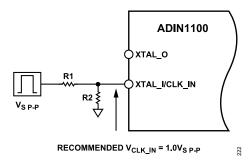

| Clock Input (CLK_IN)                                                                 |             |       |             |       |                                                                                                      |

| Clock Input Frequency                                                                |             | 25    |             | MHz   | Requirements for external clock applied to XTAL_I/CLK_IN pin, media independent interface (MII) mode |

|                                                                                      |             | 50    |             | MHz   | Reduced media independent interface (RMII) mode                                                      |

| Clock Input Voltage Range                                                            | 0.8         |       | 2.5         | V p-p |                                                                                                      |

| Clock Input Duty Cycle                                                               | 45          |       | 55          | %     |                                                                                                      |

| XTAL_I Input Impedance (Z <sub>IN,EQ</sub> )                                         |             |       |             |       |                                                                                                      |

| Driving Point Resistance (R <sub>P</sub> ) <sup>2</sup>                              |             | 6     |             | kΩ    | R <sub>P</sub>   C <sub>P</sub>                                                                      |

| Driving Point Capacitance (C <sub>P</sub> ) <sup>2</sup>                             |             | 3     |             | pF    |                                                                                                      |

| Jitter Tolerance (RMS)                                                               |             |       | 40          | ps    |                                                                                                      |

analog.com Rev. C | 5 of 85

## **SPECIFICATIONS**

Table 1. General Specifications (Continued)

| Parameter              | Min | Тур  | Max | Unit | Test Conditions/Comments |

|------------------------|-----|------|-----|------|--------------------------|

| CLK25_REF Clock Output |     |      |     |      |                          |

| CLK25_REF Frequency    |     | 25   |     | MHz  |                          |

| $V_{OH}$               |     | 1.05 |     | V    | Load = 10 pF             |

| $V_{OL}$               |     | 0    |     | V    | Load = 10 pF             |

| CLK25_REF Duty Cycle   | 45  |      | 55  | %    | Load = 10 pF             |

| LongTerm Jitter (RMS)  |     |      | 40  | ps   |                          |

Load capacitance  $(C_L) = ((C1 \times C2)/(C1 + C2) + C_{STRAY})$ , where  $C_{STRAY}$  is the stray capacitance including routing and package parasitics.

Table 2. 10BASE-T1L Specifications

| Parameter                                  | Min  | Тур              | Max  | Unit | Test Conditions/Comments                                            |

|--------------------------------------------|------|------------------|------|------|---------------------------------------------------------------------|

| POWER REQUIREMENTS                         |      |                  |      |      |                                                                     |

| Supply Voltage Range                       |      |                  |      |      |                                                                     |

| AVDD_H                                     | 3.13 | 3.3              | 3.46 | V    | 2.4 V p-p or 1.0 V p-p transmit level                               |

| AVDD_L                                     | 1.71 | 1.8 or 3.3       | 3.46 | V    |                                                                     |

| AVDD_H, AVDD_L                             | 1.71 | 1.8              | 3.46 | V    | 1.0 V p-p transmit level                                            |

| DVDD_1P1                                   | 1.0  | 1.1              | 1.2  | V    |                                                                     |

| VDDIO                                      | 1.71 | 1.8, 2.5, or 3.3 | 3.46 | V    |                                                                     |

| 1.0 V p-p Transmit Level (Single Supply)   |      |                  |      |      | AVDD_H = AVDD_L = VDDIO = 1.8 V,<br>DVDD_1P1 = DLDO_1P1             |

| AVDD_x Supply Current, I <sub>AVDD</sub>   |      | 25               |      | mA   |                                                                     |

| Power Consumption                          |      | 45               |      | mW   | 100% data throughput, full activity                                 |

|                                            |      | 11               |      | mW   | Software power-down mode                                            |

| 1.0 V p-p Transmit Level (Dual Supply)     |      |                  |      |      | AVDD_H = AVDD_L = VDDIO = 1.8 V,<br>DVDD_1P1 = external 1.1 V       |

| AVDD_x Supply Current, I <sub>AVDD</sub>   |      | 16               |      | mA   |                                                                     |

| DVDD_1P1 Supply Current, I <sub>DVDD</sub> |      | 9                |      | mA   |                                                                     |

| Power Consumption                          |      | 39               |      | mW   | 100% data throughput, full activity                                 |

| 2.4 V p-p Transmit Level (Single Supply)   |      |                  |      |      | AVDD_H = AVDD_L = VDDIO = 3.3 V,<br>DVDD_1P1 = DLDO_1P1             |

| Supply Current, I <sub>AVDD</sub>          |      | 33               |      | mA   |                                                                     |

| Power Consumption                          |      | 109              |      | mW   | 100% data throughput, full activity                                 |

|                                            |      | 22               |      | mW   | Software power-down mode                                            |

| 2.4 V p-p Transmit Level (Dual Supply)     |      |                  |      |      | AVDD_H = 3.3 V, AVDD_L = VDDIO = 1.8 V<br>DVDD_1P1 = DLDO_1P1       |

| AVDD_x Supply Current, I <sub>AVDD</sub>   |      | 16.5             |      | mA   |                                                                     |

| VDDIO Supply Current, I <sub>VDDIO</sub>   |      | 15               |      | mA   |                                                                     |

| Power Consumption                          |      | 81               |      | mW   | 100% data throughput, full activity                                 |

|                                            |      | 11               |      | mW   | Software power-down mode                                            |

| 2.4 V p-p Transmit Level (Triple Supply)   |      |                  |      |      | AVDD_H = 3.3 V, AVDD_L = VDDIO = 1.8 V<br>DVDD_1P1 = external 1.1 V |

| AVDD_x Supply Current, I <sub>AVDD</sub>   |      | 16.5             |      | mA   |                                                                     |

| VDDIO Supply Current, I <sub>VDDIO</sub>   |      | 6                |      | mA   |                                                                     |

| DVDD_1P1 Supply Current, I <sub>DVDD</sub> |      | 9                |      | mA   |                                                                     |

| Power Consumption                          |      | 75               |      | mW   | 100% data throughput, full activity                                 |

| ANALOG INPUTS AND OUTPUTS                  |      |                  |      |      |                                                                     |

| MDI Gain Offset                            | -7.5 |                  | +3.5 | %    |                                                                     |

| TIMING/LATENCY                             |      |                  |      |      |                                                                     |

| MII Latency                                |      |                  |      |      |                                                                     |

analog.com Rev. C | 6 of 85

$<sup>^2</sup>$  R<sub>P</sub> and C<sub>P</sub> are the values of the equivalent parallel RC circuit to ac ground (R<sub>P</sub>||C<sub>P</sub>), modeling the driving point impedance of the XTAL\_I/CLK\_IN pin.

**Data Sheet**

**ADIN1100**

## **SPECIFICATIONS**

## Table 2. 10BASE-T1L Specifications (Continued)

| Parameter             | Min Typ | Max | Unit | Test Conditions/Comments |

|-----------------------|---------|-----|------|--------------------------|

| Transmit (TX) Latency | <1.     | 3   | μs   | 18-bit times             |

| Receiver (RX) Latency | <3.     | 2   | μs   | 32-bit times             |

| Total Latency         | ≤5      |     | μs   |                          |

analog.com Rev. C | 7 of 85

## **TIMING CHARACTERISTICS**

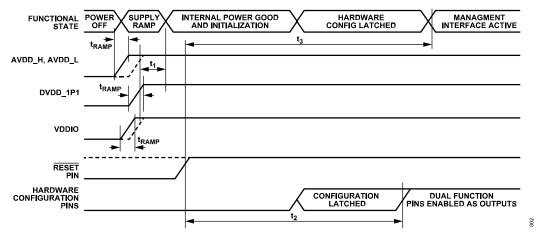

## **POWER-UP TIMING**

Table 3.

| Parameter         | Description                                               | Min | Тур | Max | Unit |

|-------------------|-----------------------------------------------------------|-----|-----|-----|------|

| t <sub>RAMP</sub> | Power supply ramp time                                    |     |     | 40  | ms   |

| $t_1$             | Minimum time interval to internal power good <sup>1</sup> | 20  |     | 43  | ms   |

| $t_2$             | Hardware configuration latch time                         | 6   | 8   | 14  | μs   |

| $t_3$             | Management interface active                               |     |     | 50  | ms   |

<sup>&</sup>lt;sup>1</sup> The minimum time interval is referenced to the last supply to reach its rising threshold. There is no specific power supply sequencing required.

Figure 2. Power-Up Timing

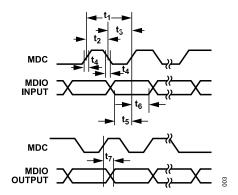

## **MANAGEMENT INTERFACE TIMING**

Table 4.

| Parameter      | Description                   | Min | Тур | Max | Unit |

|----------------|-------------------------------|-----|-----|-----|------|

| t <sub>1</sub> | MDC period                    | 400 |     |     | ns   |

| $t_2$          | MDC high time                 | 100 |     |     | ns   |

| $t_3$          | MDC low time                  | 100 |     |     | ns   |

| $t_4$          | MDC rise or fall time         |     |     | 5   | ns   |

| $t_5$          | MDIO signal setup time to MDC | 10  |     |     | ns   |

| $t_6$          | MDIO signal hold time to MDC  | 10  |     |     | ns   |

| t <sub>7</sub> | MDIO delay time to MDC        |     |     | 300 | ns   |

Figure 3. Management Interface Timing

analog.com Rev. C | 8 of 85

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 5.

| Table 5.                                           |                                       |

|----------------------------------------------------|---------------------------------------|

| Parameter                                          | Rating                                |

| VDDIO to GND                                       | -0.3 V to +4 V                        |

| DVDD_1P1, DLDO_1P1 to GND                          | -0.3 V to +1.35 V                     |

| AVDD_H, AVDD_L to GND                              | -0.3 V to +4 V                        |

| MAC Interface <sup>1</sup> , MDIO, MDC, INT to GND | -0.3 V to VDDIO + 0.3 V               |

| TXN, TXP, RXN, RXP to GND                          | -0.3 V to AVDD + 0.3 V                |

| LED_x, RESET, LINK_ST/PHYAD_2 to GND               | -0.3 V to VDDIO + 0.3 V               |

| XTAL_I/CLK_IN to GND                               | -0.3 V to +2.75 V                     |

| XTAL_O, CLK25_REF to GND                           | -0.3 V to +1.35 V                     |

| Operating Temperature Range (T <sub>A</sub> )      |                                       |

| Industrial                                         | -40°C to +105°C                       |

| Storage Temperature Range                          | -65°C to +150°C                       |

| Junction Temperature (T <sub>J</sub> max)          | 125°C                                 |

| Power Dissipation                                  | $(T_J \text{ max} - T_A)/\theta_{JA}$ |

| Lead Temperature                                   | JEDEC industry standard               |

| Soldering                                          | J-STD-020                             |

See the Pin Configuration and Function Descriptions section for the full list of MAC interface pins.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 6. Thermal Resistance

| Package Type          | $\theta_{JA}^{1}$ | $\theta_{JC}$ | Unit |

|-----------------------|-------------------|---------------|------|

| CP-40-29 <sup>2</sup> | 45                | 22            | °C/W |

- $^{1}$   $\theta_{JA}$  is specified for the worst case conditions, that is, a device soldered in a circuit board for surface-mount packages.

- <sup>2</sup> Test Condition 1: thermal impedance simulated values are based on a JE-DEC 2S2P thermal test board with thermal vias. See JEDEC JESD51.

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charged device model (FICDM) per ANSI/ESDA/JE-DEC JS-002.

## **ESD Ratings**

Table 7. ADIN1100, 40-Lead LFCSP

| ESD Model               | Withstand Threshold (V) | Class |

|-------------------------|-------------------------|-------|

| HBM                     |                         |       |

| TXN, TXP, RXN, RXP Pins | 8000                    | 3B    |

| All Other Pins          | 2000                    | 2     |

| FICDM                   | 1250                    | C3    |

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. C | 9 of 85

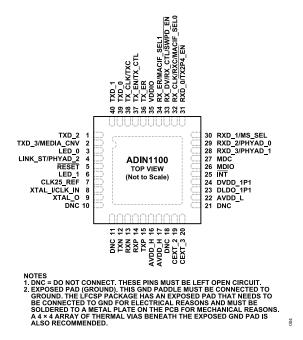

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

Table 8. Pin Function Descriptions

| Pin No.                 | Mnemonic <sup>1</sup> | PU/PD <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Interface         |                       |                    |                                                                                                                                                                                                                                                                                                                                                      |

| 7                       | CLK25_REF             | N/A                | Analog Reference Clock Output. The 25 MHz reference clock from the crystal oscillator is available on the CLK25_REF pin. This pin can be used as an input to another PHY. The 25 MHz clock output is briefly disabled (logic low) following a software reset (25 ms) or a hardware reset (70 ms). See the Reset Operations section for more details. |

| 8                       | XTAL_I/CLK_IN         | N/A                | Input for Crystal (XTAL_I).                                                                                                                                                                                                                                                                                                                          |

|                         |                       |                    | Single-Ended 25 MHz Reference Clock or 50 MHz Clock Input for RMII (CLK_IN).                                                                                                                                                                                                                                                                         |

| 9                       | XTAL_O                | N/A                | Crystal Output. If using a single-ended reference clock on XTAL_I/CLK_IN, leave XTAL_O open circuit. See the External 25 MHz Clock Input for MII and RGMII Modes section.                                                                                                                                                                            |

| Management Interface    |                       |                    |                                                                                                                                                                                                                                                                                                                                                      |

| 25                      | ĪNT                   | PU                 | Management Interface Interrupt Pin Output. Open-drain, active low output. A low on $\overline{\text{INT}}$ indicates an unmasked management interrupt. This pin requires a 1.5 k $\Omega$ pull-up resistor to VDDIO.                                                                                                                                 |

| 26                      | MDIO                  | PU                 | Management Data Input/Output Synchronous to the MDC Clock. This pin is opendrain and requires a 1.5 k $\Omega$ pull-up resistor to VDDIO.                                                                                                                                                                                                            |

| 27                      | MDC                   | PD                 | Management Data Clock Input up to 2.5 MHz.                                                                                                                                                                                                                                                                                                           |

| Reset                   |                       |                    |                                                                                                                                                                                                                                                                                                                                                      |

| 5                       | RESET                 | PU                 | Hardware Reset, Active Low Input. Hold low for >10 µs to reset the device. This pin can be left floating if a hardware reset is not required. See the Hardware Reset section.                                                                                                                                                                        |

| Media Dependent Interfa | ce (MDI)              |                    |                                                                                                                                                                                                                                                                                                                                                      |

| 12                      | TXN                   | N/A                | Transmit Negative Pin.                                                                                                                                                                                                                                                                                                                               |

| 13                      | RXN                   | N/A                | Receive Negative Pin.                                                                                                                                                                                                                                                                                                                                |

| 14                      | RXP                   | N/A                | Receive Positive Pin.                                                                                                                                                                                                                                                                                                                                |

| 15                      | TXP                   | N/A                | Transmit Positive Pin.                                                                                                                                                                                                                                                                                                                               |

analog.com Rev. C | 10 of 85

**ADIN1100**

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 8. Pin Function Descriptions (Continued)

| Pin No.       | Mnemonic <sup>1</sup> | PU/PD <sup>2</sup> | Description                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAC Interface |                       |                    |                                                                                                                                                                                                                                                                                                       |

| 1             | TXD_2                 | PD                 | Reduced Gigabit Media Independent Interface (RGMII)/MII Transmit Data 2 Input. See the MAC Interface section.                                                                                                                                                                                         |

| 2             | TXD_3/MEDIA_CNV       | PD                 | RGMII/MII Transmit Data 3 Input (TXD_3). See the MAC Interface section.  Media Converter Hardware Configuration Pin (MEDIA_CNV).                                                                                                                                                                      |

| 28            | RXD_3/PHYAD_1         | PD                 | RGMII/MII Receive Data 3 Output (RXD_3). See the MAC Interface section. PHY Address Hardware Configuration Pin 1 (PHYAD_1).                                                                                                                                                                           |

| 29            | RXD_2/PHYAD_0         | PD                 | RGMII/MII Receive Data 2 Output (RXD_2). See the MAC Interface section. PHY Address Hardware Configuration Pin 0 (PHYAD_0).                                                                                                                                                                           |

| 30            | RXD_1/MS_SEL          | PD                 | RGMII/RMII/MII Receive Data 1 Output (RXD_1). See the MAC Interface section. Leader/Follower Selection (MS_SEL). Set high for prefer leader selection and low for prefer follower selection. See Table 18.                                                                                            |

| 31            | RXD_0/TX2P4_EN        | PD                 | RGMII/RMII/MII Receive Data 0 Output (RXD_0). See the MAC Interface section.  Transmit Level Amplitude Hardware Configuration Pin (TX2P4_EN). Set high for 1 V p-p transmit amplitude. A low supports both 1 V p-p and 2.4 V p-p transmit amplitudes. See Table 19.                                   |

| 32            | RX_CLK/RXC/MACIF_SEL0 | PD                 | 2.5 MHz MII Receive Clock Output (RX_CLK).  2.5 MHz RGMII Receive Clock Output (RXC).  MAC Interface Selection Hardware Configuration Pin 0 (MACIF_SEL0). See the MAC Interface Selection section.                                                                                                    |

| 33            | RX_DV/RX_CTL/SWPD_EN  | PD                 | RMII/MII Mode Received Data Valid Output (RX_DV). This signal is known as CRS_DV in RMII mode. When asserted high, RX_DV indicates that valid data is present on the RXD_x lines.                                                                                                                     |

|               |                       | PD                 | RGMII Mode Receive Control Signal (RX_CTL). RX_CTL is a combination of the RX_DV and RX_ER signals using both edges of RXC.  Software Power-Down Configuration (SWPD_EN). Set SWPD_EN low to configuration (SWPD_EN).                                                                                 |

| 34            | RX_ER/MACIF_SEL1      | PD                 | the PHY to enter software power-down mode after power-up or reset. See Table ?  RMII/MII Mode Receive Error Detected Output (RX_ER). When asserted high, RX_ER indicates that the PHY has detected a receive error.  MAC Interface Selection Hardware Configuration Pin 1 (MACIF_SEL1). See Table 21. |

| 36            | TX_ER                 | PD                 | RMII/MII Mode Transmit Error Input Detection from the MAC to the PHY.                                                                                                                                                                                                                                 |

| 37            | TX_EN/TX_CTL          | PD                 | RMII/MII Mode Transmit Enable Input from the MAC to the PHY (TX_EN). TX_EN indicates that transmission data is available on the TXD_x lines.                                                                                                                                                          |

|               |                       |                    | RGMII Mode Transmit Control Signal (TX_CTL). TX_CTL is a combination of the TX_EN and RX_ER signals using both edges of TXC.                                                                                                                                                                          |

| 38            | TX_CLK/TXC            | PD                 | 2.5 MHz MII Transmit Clock Output (TX_CLK). 2.5 MHz RGMII Transmit Clock Input (TXC).                                                                                                                                                                                                                 |

| 39            | TXD_0                 | PD                 | RGMII/RMII/MII Transmit Data 0 Input. See the MAC Interface section.                                                                                                                                                                                                                                  |

| 40            | TXD_1                 | PD                 | RGMII/RMII/MII Transmit Data 1 Input. See the MAC Interface section.                                                                                                                                                                                                                                  |

| tatus         |                       |                    |                                                                                                                                                                                                                                                                                                       |

| 3             | LED_0                 | PU                 | General-Purpose, Programmable LED Indicator 0. The LED can be active high or active low. By default, LED_0 is configured to turn on when a link is established and blink when there is activity. See the Status LEDs section.                                                                         |

| 4             | LINK_ST/PHYAD_2       | PD                 | Link Status Output (LINK_ST). LINK_ST indicates whether a valid link has been established. LINK_ST is active high.  PHY Address Hardware Configuration Pin 2 (PHYAD_2).                                                                                                                               |

| 6             | LED_1                 | PD                 | General-Purpose, Programmable LED Indicator 1. The LED can be active high or active low. By default, LED_1 is disabled. See the Status LEDs section.                                                                                                                                                  |

analog.com Rev. C | 11 of 85

**ADIN1100**

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 8. Pin Function Descriptions (Continued)

| Pin No.                      | Mnemonic <sup>1</sup> | PU/PD <sup>2</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDO and Reference Decoupling |                       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 19                           | CEXT_2                | N/A                | External Decoupling for LDO Circuit. Connect a $0.1~\mu F$ capacitor to ground as close as possible to this pin. Do not use this pin as a voltage source for an external circuit.                                                                                                                                                                                                                                       |

| 20                           | CEXT_3                | N/A                | External Decoupling for LDO Circuit. Connect a 1 $\mu$ F capacitor to ground as close as possible to this pin. Do not use this pin as a voltage source for an external circuit.                                                                                                                                                                                                                                         |

| Power and Ground Pins        |                       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16, 17                       | AVDD_H                | N/A                | Analog Supply Voltage for the Various Analog Circuits in the Device. This supply rail can be supplied by 1.8 V to 3.3 V depending on the transmit level configuration. If AVDD_H is 3.3 V, both 1.0 V p-p and 2.4 V p-p transmit operating modes are supported. If AVDD_H is 1.8 V, only 1.0 V p-p transmit operating mode is supported. Connect 0.1 µF and 0.01 µF capacitors to GND as close as possible to this pin. |

| 22                           | AVDD_L                | N/A                | Analog Supply Voltage for the Internal LDO Circuits. This supply rail can be supplied by 1.8 V to 3.3 V. AVDD_L can be connected directly to the AVDD_H rail in long reach applications or alternatively to the VDDIO rail when the device is configured with dual supplies for lower power consumption. Connect 0.1 $\mu$ F and 0.01 $\mu$ F capacitors to GND as close as possible to this pin.                       |

| 23                           | DLDO_1P1              | N/A                | Output from an Internal 1.1 V LDO Circuit. This pin can be connected to DVDD_1P1 to eliminate an additional power supply rail. Connect a 0.68 $\mu$ F capacitor to ground as close as possible to this pin.                                                                                                                                                                                                             |

| 24                           | DVDD_1P1              | N/A                | Input for 1.1 V DVDD_1P1 Supply Rail. When using the internal LDO regulator, connect this pin directly to the DLDO_1P1 pin. Alternatively, an external 1.1 V rail can be provided to the DVDD_1P1 pin for greater power efficiency. Connect a 0.1 µF to ground as close as possible to this pin.                                                                                                                        |

| 35                           | VDDIO                 | N/A                | $3.3$ V, $2.5$ V, or $1.8$ V Digital Power for MDIO and MAC Interface. Connect $0.1~\mu F$ and $0.01~\mu F$ capacitors to GND as close as possible to the pin.                                                                                                                                                                                                                                                          |

| 41                           | EP (GND)              | N/A                | Exposed Pad (Ground). This GND paddle must be connected to ground. The LFCSP package has an exposed pad that needs to be connected to GND for electrical reasons and must be soldered to a metal plate on the PCB for mechanical reasons. A 4 × 4 array of thermal vias beneath the exposed GND pad is also recommended.                                                                                                |

| Other Pins                   |                       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10, 11, 18, 21               | DNC                   | N/A                | Do Not Connect. These pins must be left open circuit.                                                                                                                                                                                                                                                                                                                                                                   |

<sup>1</sup> Where a pin is shared between a functional signal and a hardware configuration pin signal, the hardware configuration pin signal is listed last.

analog.com Rev. C | 12 of 85

<sup>&</sup>lt;sup>2</sup> PU/PD refers to internal/on-chip pull-up or pull-down resistors. All of the hardware configuration pins have internal pull-down resistors. The default mode of operation without any external resistors connected to these pins is shown in Table 14. If an alternative mode of operation is required, use 4.7 kΩ pull-up resistors. N/A means not applicable.

Data Sheet ADIN1100

### **TYPICAL PERFORMANCE CHARACTERISTICS**

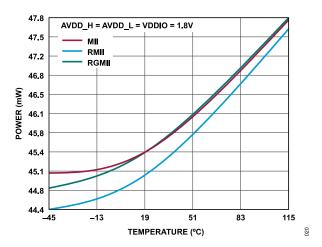

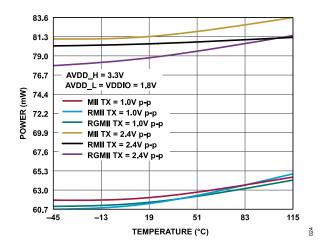

Figure 5. Power vs. Temperature, 1.8 V Single Supply, Internal LDO Circuit, 10BASE-T1L Mode

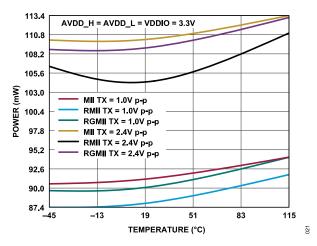

Figure 6. Power vs. Temperature, 3.3 V Single Supply, Internal LDO Circuit, 10BASE-T1L Mode

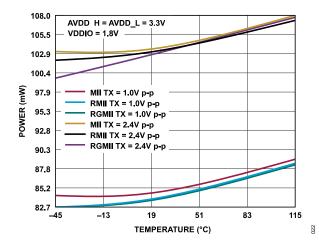

Figure 7. Power vs. Temperature, AVDD\_H = 3.3 V, AVDD\_L = 3.3 V, VDDIO = 1.8 V, Internal LDO Circuit, 10BASE-T1L Mode

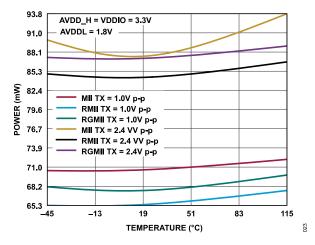

Figure 8. Power vs. Temperature, AVDD\_H = 3.3 V, VDDIO = 3.3 V, AVDD\_L = 1.8 V, Internal LDO Circuit, 10BASE-T1L Mode

Figure 9. Power vs. Temperature, AVDD\_H = 3.3 V, AVDD\_L = VDDIO = 1.8 V, Internal LDO Circuit, 10BASE-T1L Mode

analog.com Rev. C | 13 of 85

The ADIN1100 is a low power, single port 10BASE-T1L Ethernet PHY device, compliant with the IEEE 802.3cg Ethernet standard for long reach, 10 Mbps single pair Ethernet.

The ADIN1100 integrates the following features:

- ▶ PHY core with common analog circuitry

- ▶ Input and output clock buffering

- MDIO interface to control subsystem registers, clock, and software resets

- ▶ MAC interface control logic

- ► Hardware configuration pins

- ► Configurable hardware interrupt pin

- ▶ Two configurable LED pins

#### **POWER SUPPLY DOMAINS**

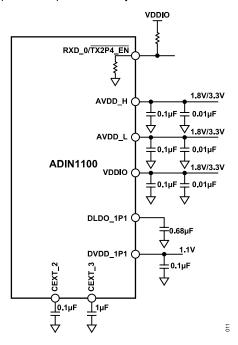

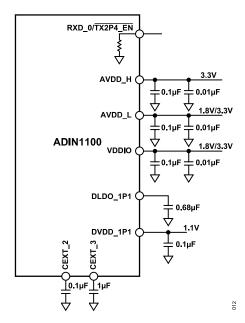

The ADIN1100 has four power supply domains and requires a minimum of one supply rail.

- ▶ AVDD\_H is the analog power supply input for the analog front end (AFE) circuitry in the ADIN1100.

- AVDD\_L is the analog supply voltage for the internal LDO circuits. AVDD\_L can be connected to the AVDD\_H rail in single supply mode, or to an alternative lower voltage rail in dual supplies mode for lower power consumption.

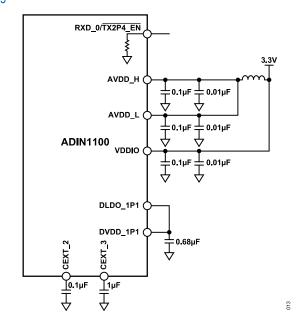

- ▶ DVDD\_1P1 is the 1.1 V digital core power supply input. It can operate from the internal 1.1 V LDO output available on the DLDO\_1P1 pin. Alternatively, DVDD\_1P1 can be driven from an external 1.1 V supply for lower power consumption.

- VDDIO is the digital power supply input for the ADIN1100 MAC interface, MDIO, and digital inputs/outputs (I/Os). It can be connected directly to the AVDD L rail or to an external power rail.

The System Level Power Management section describes various application circuits that can be used as reference.

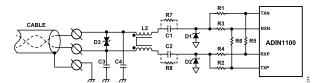

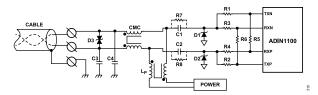

## Single-Supply Applications

In a single-supply application, connect AVDD\_H and AVDD\_L to VDDIO, and in the ADIN1100, use the internal 1.1 V LDO circuit for DVDD\_1P1. The appropriate supply voltage used depends on the end application and cable length. A recommended circuit is shown in the Single-Supply Configuration section.

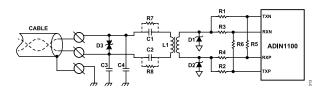

## Long Reach and Trunk/Spur Applications

The 1.0 V p-p transmit operating mode supports the spur use case and can operate at a lower AVDD\_H supply voltage of 1.8 V. The ADIN1100 in this mode supports intrinsic safety applications.

The higher transmit operating mode of 2.4 V p-p supports trunk applications and requires a higher AVDD\_H supply voltage of 3.3 V. This mode can be used for longer cable lengths in industrial Ethernet environments with higher noise levels.

#### MAC INTERFACE

The ADIN1100 provides the option of MII, RMII, or RGMII MAC interfaces. The MAC interface is selected using the hardware configuration pins (RX\_CLK/RXC/MACIF\_SEL0 and RX\_ER/MACIF\_SEL1) or via the management interface (MDIO). The two hardware configuration pins for MAC interface selection strap the ADIN1100 configuration after power-up, hardware reset, or software reset.

By default (hardware configuration pins floating), the MAC interface is configured in RMII mode. See the MAC Interface Selection for more details on how to configure the MAC interface using the hardware configuration pins.

It is recommended to use the hardware configuration pins for the MAC interface selection because the supported interfaces have different clock and pin mapping requirements.

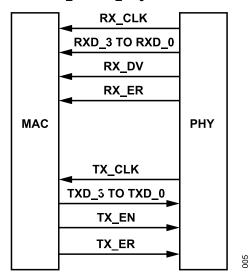

#### **MII Interface Mode**

For the MII receive interface, the ADIN1100 generates a 2.5 MHz reference clock on RX\_CLK to synchronize the RXD\_3 to RXD\_0 receive data signals. RX\_DV indicates to the MAC that valid data is present on the RXD\_3 to RXD\_0 signals. RX\_ER is driven high by the ADIN1100 if an error was detected in the frame that was received from the MDI interface and is being transmitted to the MAC interface.

For the MII transmit interface, the ADIN1100 generates a 2.5 MHz reference clock on TX\_CLK. The MAC transmits data on TXD\_3 to TXD\_0 that is synchronized with TX\_CLK. The MAC asserts TX\_EN high to indicate to the ADIN1100 that transmission data is available on the TXD\_3 to TXD\_0 signal lines.

Figure 10. MII MAC PHY Interface Signals

analog.com Rev. C | 14 of 85

Data Sheet ADIN1100

#### THEORY OF OPERATION

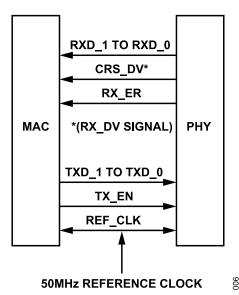

### **RMII Interface Mode**

RMII mode requires an external 50 MHz clock, which can be sourced externally from a MAC chip or a reference clock and applied to the ADIN1100 XTAL\_I/CLK\_IN pin. The 50 MHz clock is used for both the transmit and receive interfaces.

The receive data, RXD\_1 to RXD\_0, transitions synchronously to the reference clock (REF\_CLK). The carrier sense and received data valid signal (CRS\_DV) is a combination of the carrier sense and RX\_DV signals, and is asserted while the receive medium is not idle. CRS\_DV is asserted asynchronously to REF\_CLK and deasserted synchronously.

RX\_ER is also synchronous to the reference clock signal (REF\_CLK) and asserted when an error is detected in the received frame or when a false carrier is detected. RX\_ER assertion on a false carrier can be disabled by software.

Do not configure the MAC interface to RMII in software without ensuring the required 50 MHz clock is available. See MAC Interface Configuration Register for more details on RMII interface parameters.

Figure 11. RMII MAC PHY Interface Signals

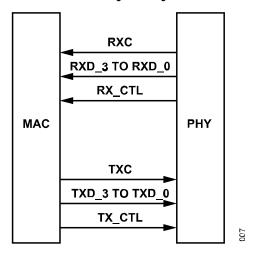

#### **RGMII Interface Mode**

For the RGMII receive interface, the ADIN1100 generates a 2.5 MHz RXC signal to synchronize RXD\_3 to RXD\_0. RX\_CTL is a combination of the RX\_DV and RX\_ER signals (as described in Table 8) using both edges of the RXC signal. The ADIN1100 transmits the RX\_DV signal on the positive edge of RXC and a combination (XOR function) of RX\_DV and RX\_ER on the negative edge of RXC.

For the RGMII transmit interface, the MAC generates a 2.5 MHz reference clock on TXC. The TXC clock is driven by the switch MAC. The MAC transmits the TXD\_3 to TXD\_0 data on both edges

of TXC. TX\_CTL is a combination of the TX\_EN and TX\_ER signals using both edges of TXC. TX\_EN is transmitted on the positive edge of TXC, and a combination (XOR function) of TX\_EN and TX\_ER is transmitted on the negative edge of TXC.

Figure 12. RGMII MAC PHY Interface Signals

#### TRANSMIT AMPLITUDE CONFIGURATION

The ADIN1100 supports two transmit amplitude modes of operation, as follows:

- ▶ 1.0 V p-p and 2.4 V p-p mode (high level)

- ▶ 1.0 V p-p only mode

The high level transmit operating mode allows the ADIN1100 to support both voltage levels. The operating level can then be automatically configured during autonegotiation (if enabled) based on the link partner capabilities. Note that the high level transmit operating mode of 2.4 V p-p requires an AVDD\_H supply voltage of 3.3 V. Otherwise, if the supply voltage is less than 3.3 V, the device may not start up correctly.

The mode of operation is configured through the TX2P4\_EN hardware configuration pin signal (see the Transmit Amplitude section). The ADIN1100 also configures the default value for the transmit level register bits used for the autonegotiation process based on the level configured with the RX\_D0/TX2P4\_EN pin (see the Transmit Amplitude Advertisement section).

The ADIN1100 is configured in high level transmit operating mode by default if the RX\_D0/TX2P4\_EN pin is left floating (internal pull-down resistor).

## LEADER/FOLLOWER CONFIGURATION

The 10BASE-T1L standard uses a leader/follower clock scheme. This scheme is commonly used in full duplex transceiver standards with echo cancellation. One PHY is designated as the leader, and the other PHY as the follower. Autonegotiation is used to determine which PHY is the leader and which is the follower. leader and follower assignment does not generally matter.

analog.com Rev. C | 15 of 85

## **Hardware Configuration**

The ADIN1100 can be configured to prefer follower or prefer leader through the RXD\_1/MS\_SEL hardware configuration pin. The recommendation is to select prefer follower or prefer leader (see the Leader/Follower Preference section). If autonegotiation is disabled, the MS\_SEL hardware configuration pin signal sets the default leader/follower selection. The ADIN1100 is configured in prefer follower by default if the pin is left floating (internal pull-down resistor).

## **Software Configuration**

The leader and follower configuration bit (CFG\_MST) is automatically updated after power-up, hardware reset, or software reset based on the MS\_SEL hardware configuration pin signal level. This bit is only used when autonegotiation is disabled. Otherwise, this bit is set or reset during the autonegotiation process (see the Autonegotiation section).

#### **AUTONEGOTIATION**

The ADIN1100 uses the autonegotiation capability in accordance with IEEE 802.3 Clause 98, providing a mechanism for exchanging information between the local device and link partners to agree to a common mode of operation. Single twisted pair autonegotiation is performed using differential Manchester encoding (DME) pages exchanged between the local device and its link partner. At a high level, the autonegotiation provides the following functions:

- ▶ Transmit

- Receive

- Half duplex

- ▶ Arbitration

During the autonegotiation process, the local device advertises its own capabilities and compares them to those received from the link partner. The arbitration mechanism defines the operating mode selected so that the transmit amplitude mode and leader/follower selection are configured for the linked devices.

If the link is dropped, the autonegotiation process restarts automatically. An autonegotiation restart can also be requested by writing to the autonegotiation restart bit (AN\_RESTART) in the autonegotiation control register (AN\_CONTROL).

The autonegotiation process can take time to complete, depending on the number of pages exchanged, but is always the fastest way to bring up a link. Clause 98 of the IEEE 802.3 standard details the sequence timers and DME pages timing related to autonegotiation.

Autonegotiation is enabled by default for the ADIN1100, and it is strongly recommended to always keep it enabled.

## Transmit Amplitude Advertisement

## **High Voltage Transmit Ability Advertisement**

The B10L\_TX\_LVL\_HI\_ABLE bit configures the default values for the autonegotiation advertisement parameters. This bit is read only and configured based on the TX2P4\_EN hardware configuration pin signal as described in the Transmit Amplitude section. The transmit amplitude advertisement parameters are defined with the following bits:

- ► AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL: advertisement of the 10BASE-T1L high level transmit operating mode ability bit

- ► AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ: advertisement of the 10BASE-T1L high level transmit operating mode request bit

- ▶ B10L\_TX\_LVL\_HI: 10BASE-T1L transmit voltage amplitude control bit

#### Table 9. AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL Settings

| Bit Setting  | Description                                         |

|--------------|-----------------------------------------------------|

| 0            | Support 1.0 V p-p transmit level only               |

| 1            | Support both 1.0 V p-p and 2.4 V p-p transmit level |

| Table 10. AN | _ADV_B10L_TX_LVL_HI_REQ Settings                    |

| Bit Setting  | Description                                         |

| 0            | Request 1.0 V p-p transmit level                    |

| 1            | Request 2.4 V p-p transmit level                    |

## High Voltage Transmit Level Request Advertisement

The ADIN1100 can be configured to advertise a request for the 2.4 V p-p transmit level using the 10BASE-T1L high level transmit operating mode ability advertisement bit (AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL). Note that the 2.4 V p-p transmit level must be enabled using the TX2P4\_EN hardware configuration pin signal to enable the high voltage request advertisement.

#### **Link Partner Transmit Level Advertisement**

The high level transmit information advertised from the link partner can be read using the following bits:

- ▶ AN\_LP\_ADV\_B10L\_TX\_LVL\_HI\_ABL: Link Partner 10BASE-T1L high level transmit operating mode ability

- ► AN\_LP\_ADV\_B10L\_TX\_LVL\_HI\_REQ: Link Partner 10BASE-T1L high level transmit operating mode request

These bits are updated during the autonegotiation process and are valid when the autonegotiation complete register bit (AN\_COM-PLETE) is set.

analog.com Rev. C | 16 of 85

## Transmit Amplitude Resolution

#### Overview

Autonegotiation supports the following features to define the transmit amplitude to use between a local node and its link partner:

- Advertise the high voltage transmit ability from the local node

- Request to use the high voltage transmit level from the local node

- Read the link partner transmit level ability and transmit level request

- Autonegotiation and transmit level operating mode selection

If the ADIN1100 is configured in high voltage mode, the autonegotiation process determines the level to use based on the link partner capabilities.

#### **Determination of Transmit Level Resolution**

For a 10BASE-T1L link, if either the local or remote PHY advertises that it is not capable of supporting the high level (2.4 V p-p) transmit operating mode or if neither the local nor remote PHY advertises a request for high level (2.4 V p-p) transmit operating mode, the result is operation at the 1.0 V p-p transmit level.

If both the local and remote PHYs advertise that they are capable of transmitting in the high level (2.4 V p-p) transmit operating mode

and if either the local or remote PHY advertises a request for high level (2.4 V p-p) transmit operating mode, the result is operation at the 2.4 V p-p transmit level.

Thus, a PHY can ensure that the device must operate at the 1.0 V p-p transmit level. But it can only request operation at the 2.4 V p-p transmit level.

## **Software Configuration**

The ADIN1100 transmit level can also be configured in software using the following 10BASE-T1L autonegotiation advertisement bits:

- AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL: high level transmit operating mode ability bit

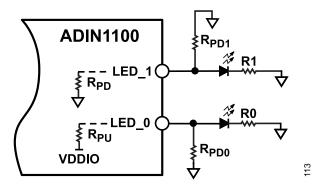

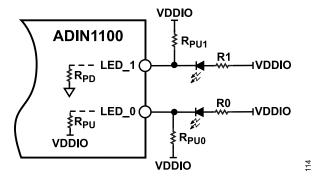

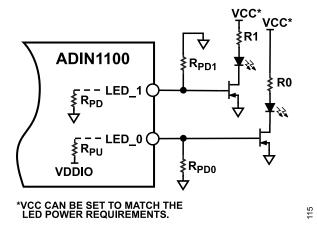

- AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ: high level transmit operating mode request register bits