# MAX16833AUE/V+TQA Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number MAX16833AUE/V+TQA-DG

Manufacturer Analog Devices Inc./Maxim Integrated

Manufacturer Product Number MAX16833AUE/V+TQA

Description IC LED DRIVER CTRLR PWM 16TSSOP

Detailed Description LED Driver IC 1 Output DC DC Controller Flyback, SE

PIC, Step-Down (Buck), Step-Up (Boost) Analog, PW

M Dimming 16-TSSOP-EP

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# **Purchase and inquiry**

| Manufacturer Product Number: | Manufacturer:                                     |

|------------------------------|---------------------------------------------------|

| MAX16833AUE/V+TQA            | Analog Devices Inc./Maxim Integrated              |

| Series:                      | Product Status:                                   |

|                              | Active                                            |

| Type:                        | Topology:                                         |

| DC DC Controller             | Flyback, SEPIC, Step-Down (Buck), Step-Up (Boost) |

| Internal Switch(s):          | Number of Outputs:                                |

| No                           | 1                                                 |

| Voltage - Supply (Min):      | Voltage - Supply (Max):                           |

| 5V                           | 65V                                               |

| Voltage - Output:            | Current - Output / Channel:                       |

|                              |                                                   |

| Frequency:                   | Dimming:                                          |

| 100kHz ~ 1MHz                | Analog, PWM                                       |

| Applications:                | Operating Temperature:                            |

| Lighting                     | -40°C ~ 125°C (TA)                                |

| Grade:                       | Qualification:                                    |

| Automotive                   | AEC-Q100                                          |

| Mounting Type:               | Package / Case:                                   |

| Surface Mount                | 16-TSSOP (0.173", 4.40mm Width) Exposed Pad       |

| Supplier Device Package:     | Base Product Number:                              |

| 16-TSSOP-EP                  | MAX16833                                          |

# **Environmental & Export classification**

8542.39.0001

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

#### **General Description**

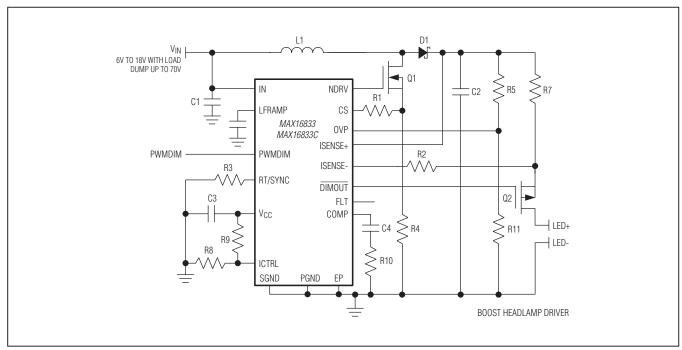

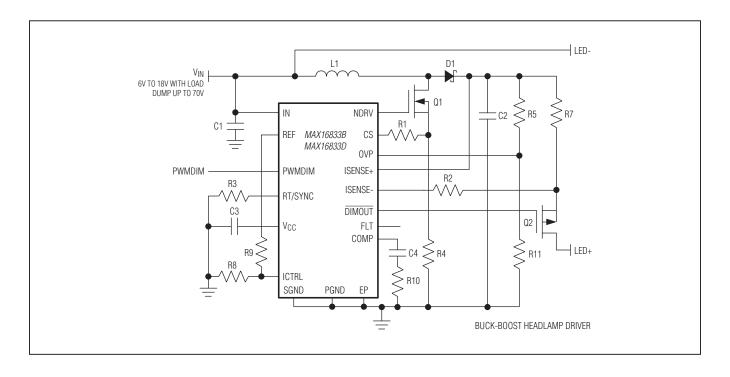

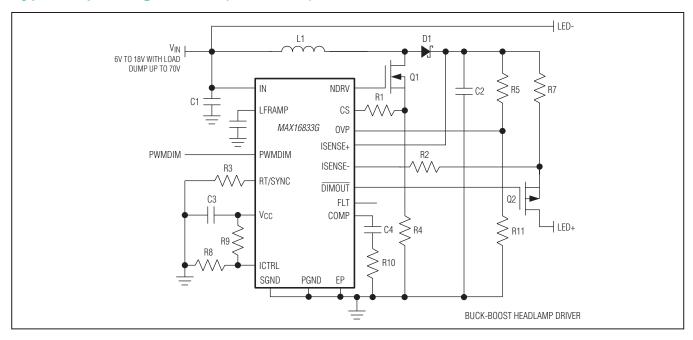

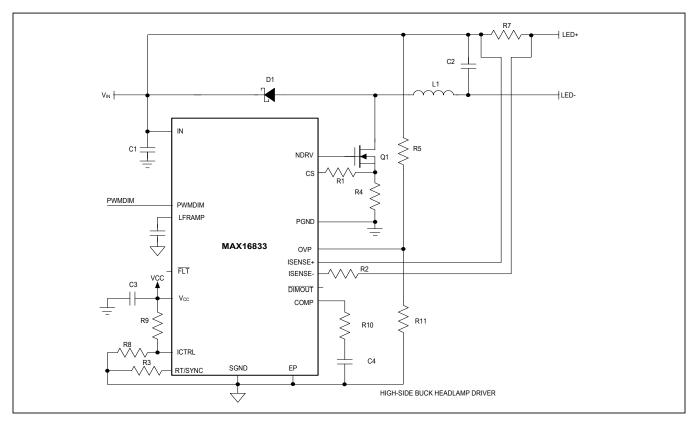

The MAX16833, MAX16833B, MAX16833C, MAX16833D, and MAX16833G are peak current-mode-controlled LED drivers for boost, buck-boost, SEPIC, flyback, and high-side buck topologies. A dimming driver designed to drive an external p-channel in series with the LED string provides wide-range dimming control. This feature provides extremely fast PWM current switching to the LEDs with no transient overvoltage or undervoltage conditions. In addition to PWM dimming, the ICs provide analog dimming using a DC input at ICTRL. The ICs sense the LED current at the high side of the LED string.

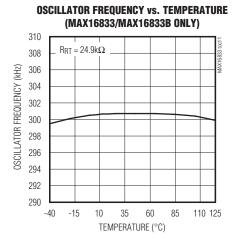

A single resistor from RT/SYNC to ground sets the switching frequency from 100kHz to 1MHz, while an external clock signal capacitively coupled to RT/SYNC allows the ICs to synchronize to an external clock. In the MAX16833/C/G, the switching frequency can be dithered for spread-spectrum applications. The MAX16833B/D instead provide a 1.64V reference voltage with a 2% tolerance.

The ICs operate over a wide 5V-to-65V supply range and include a 3A sink/source gate driver for driving a power MOSFET in high-power LED driver applications. Additional features include a fault-indicator output (FLT) for short or overtemperature conditions and an overvoltage-protection sense input (OVP) for overvoltage protection. High-side current sensing combined with a p-channel dimming MOSFET allow the positive terminal of the LED string to be shorted to the positive input terminal or to the negative input terminal without any damage. This is a unique feature of the ICs.

### **Applications**

- Automotive Exterior Lighting:

High-Beam/Low-Beam/Signal/Position Lights,

Daytime Running Lights (DRLs),

Fog Light and Adaptive Front-Light Assemblies

- Commercial, Industrial, and Architectural Lighting

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Integration Minimizes BOM for High-Brightness LED Driver with a Wide Input Range Saving Space and Cost

- +5V to +65V Wide Input Voltage Range with a Maximum 65V Boost Output

- Integrated High-Side pMOS Dimming MOSFET Driver (Allows Single-Wire Connection to LEDs)

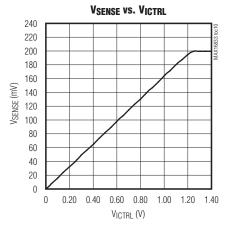

- ICTRL Pin for Analog Dimming

- Integrated High-Side Current-Sense Amplifier

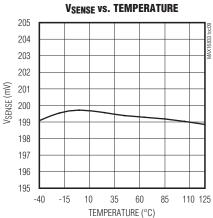

- Full-Scale, High-Side, Current-Sense Voltage of 200mV

- Simple to Optimize for Efficiency, Board Space, and Input Operating Range

- Boost, SEPIC, and Buck-Boost Single-Channel LED Drivers

- 2% Accurate 1.64V Reference (MAX16833B/D)

- Programmable Operating Frequency (100kHz to 1MHz) with Synchronization Capability

- Frequency Dithering for Spread-Spectrum Applications (MAX16833/C/G)

- Thermally Enhanced 5mm x 4.4mm, 16-Pin TSSOP Package with Exposed Pad

- Protection Features and Wide Temperature Range Increase System Reliability

- Short-Circuit, Overvoltage, and Thermal Protection

- Fault-Indicator Output

- -40°C to +125°C Operating Temperature Range

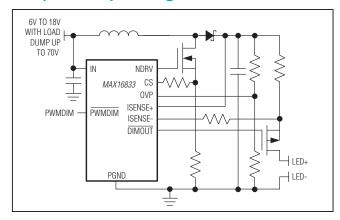

## **Simplified Operating Circuit**

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

#### **Absolute Maximum Ratings**

| IN to PGND                             | -0.3V to +70V     | Peak Current on NDRVQ3A                               |

|----------------------------------------|-------------------|-------------------------------------------------------|

| ISENSE+, ISENSE-, DIMOUT to PGND       | -0.3V to +80V     | Continuous Current on NDRVQ100mA                      |

| DIMOUT to ISENSE+                      | 9V to +0.3V       | Short-Circuit Duration on VCCContinuous               |

| ISENSE- to ISENSE+                     | 0.6V to +0.3V     | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| PGND to SGND                           | 0.3V to +0.3V     | 16-Pin TSSOP (derate 26.1mW/°C above +70°C)2089mW     |

| VCC to PGND                            | 0.3V to +9V       | Operating Temperature Range40°C to +125°C             |

| NDRV to PGND0.3V to                    | $(V_{CC} + 0.3V)$ | Junction Temperature+150°C                            |

| OVP, PWMDIM, COMP, LFRAMP, REF, ICTRL, |                   | Storage Temperature Range65°C to +150°C               |

| RT/SYNC, FLT to SGND                   | 0.3V to +6.0V     | Lead Temperature (soldering, 10s)+300°C               |

| CS to PGND                             | 0.3V to +6.0V     | Soldering Temperature (reflow)+260°C                  |

| Continuous Current on IN               | 100mA             |                                                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Thermal Characteristics (Note 1)**

16 TSSOP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......38.3°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......3°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{IN} = 12V, R_{RT} = 12.4k\Omega, C_{IN} = C_{VCC} = 1\mu F, C_{LFRAMP}/C_{REF} = 0.1\mu F, NDRV = COMP = \overline{DIMOUT} = PWMDIM = \overline{FLT} = unconnected, VOVP = VCS = VPGND = VSGND = 0V, VISENSE+ = VISENSE- = 45V, VICTRL = 1.40V, TA = TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)$

| PARAMETER                     | SYMBOL              | CONDITIONS                                                        | MIN       | TYP  | MAX  | UNITS  |  |  |

|-------------------------------|---------------------|-------------------------------------------------------------------|-----------|------|------|--------|--|--|

| SYSTEM SPECIFICATIONS         |                     |                                                                   |           |      |      |        |  |  |

| Operational Supply Voltage    | V <sub>IN</sub>     |                                                                   | 5         |      | 65   | V      |  |  |

| Supply Current                | l                   | PWMDIM = 0, no switching                                          |           | 1.5  | 2.5  | mA     |  |  |

| Supply Current                | I <sub>INQ</sub>    | Switching                                                         | 2.5 4     |      | 4    | ] IIIA |  |  |

| Undervoltage Lockout (UVLO)   | UVLOR <sub>IN</sub> | V <sub>IN</sub> rising                                            | 4.2       | 4.55 | 4.85 | V      |  |  |

| Undervoltage Lockout (UVLO)   | UVLOFIN             | V <sub>IN</sub> falling, I <sub>VCC</sub> = 35mA                  | 4.05      | 4.3  | 4.65 | V      |  |  |

| UVLO Hysteresis               |                     |                                                                   |           | 250  |      | mV     |  |  |

| Startup Delay                 | tSTART_DELAY        | During power-up                                                   |           | 410  |      | μs     |  |  |

| UVLO Falling Delay            | tFALL DELAY         | During power-down                                                 |           | 3.3  |      | μs     |  |  |

| V <sub>CC</sub> LDO REGULATOR | _                   |                                                                   |           |      |      |        |  |  |

| Pogulator Output Voltage      | V                   | $0.1\text{mA} \le I_{VCC} \le 50\text{mA}, 9V \le V_{IN} \le 14V$ | 6.75 6.95 | 6.05 | 7.15 | V      |  |  |

| Regulator Output Voltage      | V <sub>CC</sub>     | 14V ≤ V <sub>IN</sub> ≤ 65V, I <sub>VCC</sub> = 10mA              | 0.75      | 0.93 |      |        |  |  |

| Dropout Voltage               | V <sub>DOVCC</sub>  | $I_{VCC}$ = 50mA, $V_{IN}$ = 5V                                   |           | 0.15 | 0.35 | V      |  |  |

| Short-Circuit Current         | I <sub>MAXVCC</sub> | $V_{CC} = 0V, V_{IN} = 5V$                                        | 55        | 100  | 150  | mA     |  |  |

| OSCILLATOR (RT/SYNC)          |                     |                                                                   |           |      |      |        |  |  |

| Switching Frequency Range     | f <sub>SW</sub>     |                                                                   | 100       |      | 1000 | kHz    |  |  |

| Bias Voltage at RT/SYNC       | V <sub>RT</sub>     |                                                                   |           | 1    |      | V      |  |  |

| Maximum Duty Cycle            |                     | V <sub>CS</sub> = 0V; MAX16833/MAX16833B only                     | 87.5      | 88.5 | 89.5 |        |  |  |

|                               | D <sub>MAX</sub>    | V <sub>CS</sub> = 0V; MAX16833C/MAX16833D/<br>MAX16833G only      | 93        | 94   | 95   | %      |  |  |

| Oscillator Frequency Accuracy |                     |                                                                   | -5        |      | +5   | %      |  |  |

# **High-Voltage HB LED Drivers with Integrated High-Side Current Sense**

#### **Electrical Characteristics (continued)**

$(V_{IN}=12V,R_{RT}=12.4k\Omega,C_{IN}=C_{VCC}=1\mu F,C_{LFRAMP}/C_{REF}=0.1\mu F,NDRV=COMP=\overline{DIMOUT}=PWMDIM=\overline{FLT}=unconnected,\\ VOVP=V_{CS}=V_{PGND}=V_{SGND}=0V,V_{ISENSE+}=V_{ISENSE-}=45V,V_{ICTRL}=1.40V,T_{A}=T_{J}=-40^{\circ}C to +125^{\circ}C,unless otherwise noted. Typical values are at T_{A}=+25^{\circ}C.) (Note 2)$

| PARAMETER                                        | SYMBOL                   | CONDITIONS                                                            | MIN                | TYP      | MAX                | UNITS |

|--------------------------------------------------|--------------------------|-----------------------------------------------------------------------|--------------------|----------|--------------------|-------|

| Synchronization Logic-High Input                 | V <sub>IH-SYNC</sub>     | VRT rising                                                            | 3.8                |          |                    | V     |

| Synchronization Frequency Range                  | fSYNCIN                  |                                                                       | 1.1f <sub>SW</sub> |          | 1.5f <sub>SW</sub> |       |

| SLOPE COMPENSATION                               |                          |                                                                       |                    |          |                    |       |

| Slope Compensation<br>Current-Ramp Height        | I <sub>SLOPE</sub>       | Ramp peak current added to CS input per switching cycle               | 46                 | 50       | 54                 | μΑ    |

| DITHERING RAMP GENERATOR                         | (LFRAMP) (MA             | AX16833/MAX16833C/MAX16833G only)                                     |                    |          |                    |       |

| Charging Current                                 |                          | V <sub>LFRAMP</sub> = 0V                                              | 80                 | 100      | 120                | μΑ    |

| Discharging Current                              |                          | V <sub>LFRAMP</sub> = 2.2V                                            | 80                 | 100      | 120                | μΑ    |

| Comparator High Trip Threshold                   |                          |                                                                       |                    | 2        |                    | V     |

| Comparator Low Trip Threshold                    |                          |                                                                       |                    | $V_{RT}$ |                    | V     |

| REFERENCE OUTPUT (REF) (MA                       | AX16833B/MAX             | (16833D only)                                                         |                    |          |                    |       |

| Reference Output Voltage                         | V <sub>REF</sub>         | I <sub>REF</sub> = 0 to 80FA                                          | 1.604              | 1.636    | 1.669              | V     |

| ANALOG DIMMING (ICTRL)                           |                          |                                                                       |                    |          |                    |       |

| Input-Bias Current                               | IB <sub>ICTRL</sub>      | V <sub>ICTRL</sub> = 0.62V                                            | 0                  | 35       | 200                | nA    |

| LED CURRENT-SENSE AMPLIFI                        | ER                       |                                                                       |                    |          |                    |       |

| ISENSE+ Input-Bias Current                       | IB <sub>ISENSE+</sub>    | V <sub>ISENSE+</sub> = 65V, V <sub>ISENSE-</sub> = 64.8V              | 200                | 400      | 700                | μΑ    |

| ISENSE+ Input-Bias Current with DIM Low          | IB <sub>ISENSE+OFF</sub> | V <sub>ISENSE+</sub> = 48V, V <sub>ISENSE-</sub> = 48V,<br>PWMDIM = 0 |                    | 200      |                    | μA    |

| ISENSE- Input-Bias Current                       | IB <sub>ISENSE</sub> -   | V <sub>ISENSE+</sub> = 65V, V <sub>ISENSE-</sub> = 64.8V              | 2                  | 5        | 8                  | μA    |

| Voltage Gain                                     | .02.102                  | .52.162                                                               |                    | 6.15     |                    | V/V   |

|                                                  |                          | V <sub>ICTRL</sub> = 1.4V                                             | 195                | 199      | 203                |       |

| Current-Sense Voltage                            | V <sub>SENSE</sub>       | V <sub>ICTRL</sub> = 0.616V                                           | 100                |          | mV                 |       |

|                                                  |                          | V <sub>ICTRL</sub> = 0.2465V                                          | 38.4               | 40       | 41.4               |       |

| Bandwidth                                        | BW                       | AV <sub>DC</sub> - 3dB                                                |                    | 5        |                    | MHz   |

| COMP                                             |                          |                                                                       |                    |          |                    |       |

| Transconductance                                 | GM <sub>COMP</sub>       |                                                                       | 2100               | 3500     | 4900               | μS    |

| Open-Loop DC Gain                                | AV <sub>OTA</sub>        |                                                                       |                    | 75       |                    | dB    |

| COMP Input Leakage                               | I <sub>LCOMP</sub>       |                                                                       | -300               |          | +300               | nA    |

| COMP Sink Current                                | I <sub>SINK</sub>        |                                                                       | 100                | 400      | 700                | μΑ    |

| COMP Source Current                              | ISOURCE                  |                                                                       | 100                | 400      | 700                | μΑ    |

| PWM COMPARATOR                                   |                          |                                                                       |                    |          |                    |       |

| Input Offset Voltage                             | V <sub>OS-PWM</sub>      |                                                                       |                    | 2        |                    | V     |

| Leading-Edge Blanking                            |                          |                                                                       |                    | 50       |                    | ns    |

| Propagation Delay to NDRV                        | t <sub>ON(MIN)</sub>     | Includes leading-edge blanking time with 10mV overdrive               | 55                 | 80       | 110                | ns    |

| CS LIMIT COMPARATOR                              |                          |                                                                       |                    |          |                    |       |

| Current-Limit Threshold                          | V <sub>CS LIMIT</sub>    |                                                                       | 406                | 418      | 430                | mV    |

| CS Limit-Comparator<br>Propagation Delay to NDRV | t <sub>CS_PROP</sub>     | 10mV overdrive (excluding leading-edge blanking time)                 |                    | 30       |                    | ns    |

| Leading-Edge Blanking                            |                          |                                                                       | <u> </u>           | 50       | -                  | ns    |

# **High-Voltage HB LED Drivers with Integrated High-Side Current Sense**

#### **Electrical Characteristics (continued)**

$(V_{IN}=12V,\,R_{RT}=12.4k\Omega,\,C_{IN}=C_{VCC}=1\mu F,\,C_{LFRAMP}/C_{REF}=0.1\mu F,\,NDRV=COMP=\overline{DIMOUT}=PWMDIM=\overline{FLT}=unconnected,\\ V_{OVP}=V_{CS}=V_{PGND}=V_{SGND}=0V,\,V_{ISENSE+}=V_{ISENSE-}=45V,\,V_{ICTRL}=1.40V,\,T_{A}=T_{J}=-40^{\circ}C\ to\ +125^{\circ}C,\,unless\ otherwise\ noted.$  Typical values are at  $T_{A}=+25^{\circ}C.$ ) (Note 2)

| PARAMETER                                                                                                    | SYMBOL                   | CONDITIONS                                                                   | MIN  | TYP   | MAX  | UNITS           |

|--------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------|------|-------|------|-----------------|

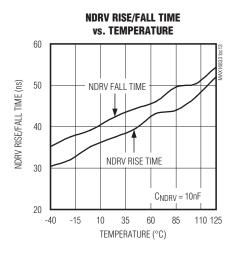

| GATE DRIVER (NDRV)                                                                                           | •                        |                                                                              |      |       |      |                 |

| Peak Pullup Current                                                                                          | I <sub>NDRVPU</sub>      | V <sub>CC</sub> = 7V, V <sub>NDRV</sub> = 0V                                 |      | 3     |      | Α               |

| Peak Pulldown Current                                                                                        | I <sub>NDRVPD</sub>      | V <sub>CC</sub> = 7V, V <sub>NDRV</sub> = 7V                                 |      | 3     |      | Α               |

| Rise Time                                                                                                    | t <sub>r</sub>           | C <sub>NDRV</sub> = 10nF                                                     |      | 30    |      | ns              |

| Fall Time                                                                                                    | t <sub>f</sub>           | C <sub>NDRV</sub> = 10nF                                                     |      | 30    |      | ns              |

| R <sub>DSON</sub> Pulldown nMOS                                                                              | R <sub>NDRVON</sub>      | V <sub>COMP</sub> = 0V, I <sub>SINK</sub> = 100mA                            | 0.25 | 0.6   | 1.1  | I               |

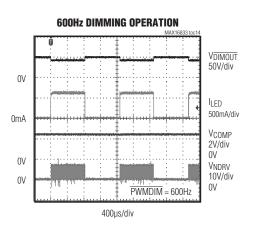

| PWM DIMMING (PWMDIM)                                                                                         |                          |                                                                              |      |       |      |                 |

| ON Threshold                                                                                                 | V <sub>PWMON</sub>       |                                                                              | 1.19 | 1.225 | 1.26 | V               |

| Hysteresis                                                                                                   | V <sub>PWMHY</sub>       |                                                                              |      | 70    |      | mV              |

| Pullup Resistance                                                                                            | R <sub>PWMPU</sub>       |                                                                              | 1.7  | 3     | 4.5  | МΩ              |

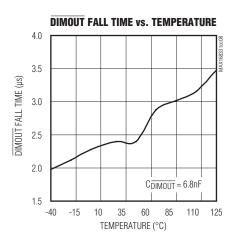

| PWMDIM to LED Turn-Off Time                                                                                  |                          | PWMDIM falling edge to rising edge on DIMOUT, C <sub>DIMOUT</sub> = 7nF      |      | 2     |      | μs              |

| PWMDIM to LED Turn-On Time                                                                                   |                          | PWMDIM rising edge to falling edge on DIMOUT, C <sub>DIMOUT</sub> = 7nF      |      | 3     |      | μs              |

| pMOS GATE DRIVER (DIMOUT)                                                                                    |                          |                                                                              |      |       |      |                 |

| Peak Pullup Current                                                                                          | I <sub>DIMOUTPU</sub>    | V <sub>PWMDIM</sub> = 0V,<br>V <sub>ISENSE+</sub> - V <sub>DIMOUT</sub> = 7V | 25   | 50    | 80   | mA              |

| Peak Pulldown Current                                                                                        | I <sub>DIMOUTPD</sub>    | V <sub>ISENSE+</sub> - V <sub>DIMOUT</sub> = 0V                              | 10   | 25    | 45   | mA              |

| DIMOUT Low Voltage with                                                                                      |                          |                                                                              | -8.7 | -7.4  | -6.3 | V               |

| Respect to V <sub>ISENSE+</sub>                                                                              |                          |                                                                              | -0.7 | -7.4  | -0.3 | V               |

| OVERVOLTAGE PROTECTION (                                                                                     | OVP)                     |                                                                              |      |       |      |                 |

| Threshold                                                                                                    | V <sub>OVPOFF</sub>      | V <sub>OVP</sub> rising                                                      | 1.19 | 1.225 | 1.26 | V               |

| Hysteresis                                                                                                   | V <sub>OVPHY</sub>       |                                                                              |      | 70    |      | mV              |

| Input Leakage                                                                                                | I <sub>LOVP</sub>        | V <sub>OVP</sub> = 1.235V                                                    | -300 |       | +300 | nA              |

| SHORT-CIRCUIT HICCUP MODE                                                                                    | (not present i           | n the MAX16833G)                                                             |      |       |      |                 |

| Short-Circuit Threshold                                                                                      | V <sub>SHORT-HIC</sub>   | (V <sub>ISENSE+</sub> - V <sub>ISENSE-</sub> ) rising                        | 285  | 298   | 310  | mV              |

| Hiccup Time                                                                                                  | tHICCUP                  |                                                                              |      | 8192  |      | Clock<br>Cycles |

| Delay in Short-Circuit Hiccup<br>Activation                                                                  |                          |                                                                              |      | 1     |      | μs              |

| BUCK-BOOST SHORT-CIRCUIT                                                                                     | DETECT                   |                                                                              |      |       |      |                 |

| Buck-Boost Short-Circuit<br>Threshold                                                                        | V <sub>SHORT-BB</sub>    | (V <sub>ISENSE+</sub> - V <sub>IN</sub> ) falling, V <sub>IN</sub> = 12V     | 1.15 | 1.55  | 1.9  | V               |

| Delay in FLT Assertion from<br>Buck-Boost Short-Circuit<br>Condition                                         | t <sub>DEL-BB-SHRT</sub> | Counter increments only when VPWMDIM > VPWMON                                |      | 8192  |      | Clock<br>Cycles |

| Delay in FLT Deassertion After<br>Buck-Boost Short Circuit is<br>Removed (Consecutive Clock-<br>Cycle Count) |                          | Counter increments only when VPWMDIM > VPWMON                                |      | 8192  |      | Clock<br>Cycles |

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

#### **Electrical Characteristics (continued)**

$(V_{IN} = 12V, R_{RT} = 12.4k\Omega, C_{IN} = C_{VCC} = 1\mu F, C_{LFRAMP}/C_{REF} = 0.1\mu F, NDRV = COMP = \overline{DIMOUT} = PWMDIM = \overline{FLT} = unconnected, VOVP = VCS = VPGND = VSGND = 0V, VISENSE+ = VISENSE- = 45V, VICTRL = 1.40V, TA = TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)$

| PARAMETER                    | SYMBOL              | OL CONDITIONS                                          |  | TYP  | MAX | UNITS |

|------------------------------|---------------------|--------------------------------------------------------|--|------|-----|-------|

| OPEN-DRAIN FAULT (FLT)       |                     |                                                        |  |      |     |       |

| Output Voltage Low           | V <sub>OL-FLT</sub> | $V_{IN}$ = 4.75V, $V_{OVP}$ = 2V, and $I_{SINK}$ = 5mA |  | 40   | 200 | mV    |

| Output Leakage Current       |                     | V <sub>FLT</sub> = 5V                                  |  |      | 1   | μA    |

| THERMAL SHUTDOWN             |                     |                                                        |  |      |     |       |

| Thermal-Shutdown Temperature |                     | Temperature rising                                     |  | +160 |     | °C    |

| Thermal-Shutdown Hysteresis  |                     |                                                        |  | 10   |     | °C    |

Note 2: All devices are 100% tested at T<sub>A</sub> = +25°C. Limits over temperature are guaranteed by design.

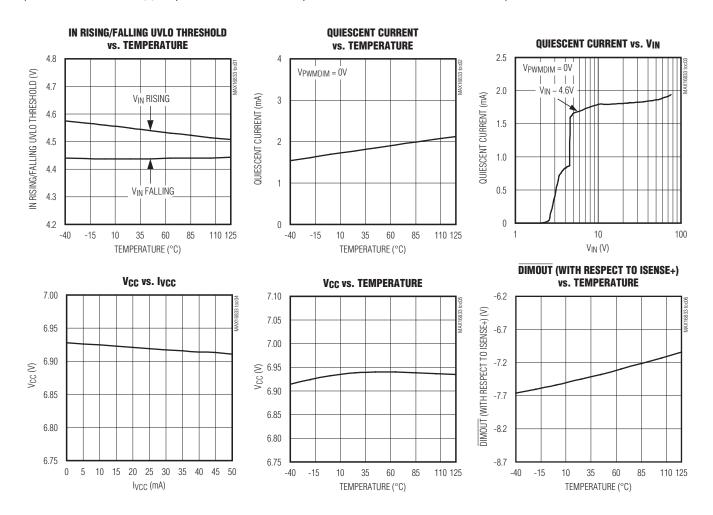

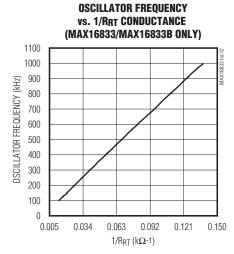

#### **Typical Operating Characteristics**

$(V_{IN} = +12V, C_{VIN} = C_{VCC} = 1\mu F, C_{LFRAMP}/C_{REF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

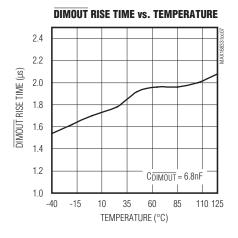

### **Typical Operating Characteristics (continued)**

$(V_{IN} = +12V, C_{VIN} = C_{VCC} = 1\mu F, C_{LFRAMP}/C_{REF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

# **High-Voltage HB LED Drivers with Integrated High-Side Current Sense**

### **Typical Operating Characteristics (continued)**

$(V_{IN} = +12V, C_{VIN} = C_{VCC} = 1\mu F, C_{LFRAMP}/C_{REF} = 0.1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

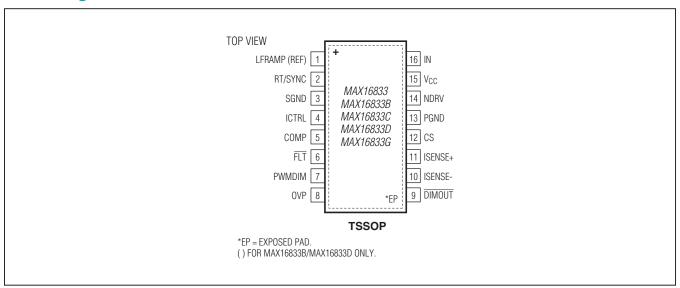

## **Pin Configuration**

# **High-Voltage HB LED Drivers with Integrated High-Side Current Sense**

# **Pin Description**

| PIN                                                | NAME                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFRAMP<br>(MAX16833/<br>MAX16833C/<br>1 MAX16833G) |                                  | Low-Frequency Ramp Output. Connect a capacitor from LFRAMP to ground to program the ramp frequency, or connect to SGND if not used. A resistor can be connected between LFRAMP and RT/SYNC to dither the PWM switching frequency to achieve spread spectrum.                                                                                                                                                                                                            |

|                                                    | REF<br>(MAX16833B/<br>MAX16833D) | 1.64V Reference Output. Connect a 1µF ceramic capacitor from REF to SGND to provide a stable reference voltage. Connect a resistive divider from REF to ICTRL for analog dimming.                                                                                                                                                                                                                                                                                       |

| 2                                                  | RT/SYNC                          | PWM Switching Frequency Programming Input. Connect a resistor ( $R_{RT}$ ) from RT/SYNC to SGND to set the internal clock frequency. Frequency = $(7.350 \times 10^9)/R_{RT}$ for the MAX16833/B. Frequency = $(6.929 \times 10^9)/R_{RT}$ for the MAX16833C/D/G. An external pulse can be applied to RT/SYNC through a coupling capacitor to synchronize the internal clock to the external pulse frequency. The parasitic capacitance on RT/SYNC should be minimized. |

| 3                                                  | SGND                             | Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4                                                  | ICTRL                            | Analog Dimming-Control Input. The voltage at ICTRL sets the LED current level when $V_{ICTRL} < 1.2V$ . For $V_{ICTRL} > 1.4V$ , the internal reference sets the LED current.                                                                                                                                                                                                                                                                                           |

| 5                                                  | COMP                             | Compensation Network Connection. For proper compensation, connect a suitable RC network from COMP to ground.                                                                                                                                                                                                                                                                                                                                                            |

| 6                                                  | FLT                              | Active-Low, Open-Drain Fault Indicator Output. See the Fault Indicator (FLT) section.                                                                                                                                                                                                                                                                                                                                                                                   |

| 7                                                  | PWMDIM                           | PWM Dimming Input. When PWMDIM is pulled low, DIMOUT is pulled high and PWM switching is disabled. PWMDIM has an internal pullup resistor, defaulting to a high state when left unconnected.                                                                                                                                                                                                                                                                            |

| 8                                                  | OVP                              | LED String Overvoltage-Protection Input. Connect a resistive divider between ISENSE+, OVP, and SGND. When the voltage on OVP exceeds 1.23V, a fast-acting comparator immediately stops PWM switching. This comparator has a hysteresis of 70mV.                                                                                                                                                                                                                         |

| 9                                                  | DIMOUT                           | Active-Low External Dimming p-Channel MOSFET Gate Driver                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10                                                 | ISENSE-                          | Negative LED Current-Sense Input. A $100\Omega$ resistor is recommended to be connected between ISENSE- and the negative terminal of the LED current-sense resistor. This preserves the absolute maximum rating of the ISENSE- pin during LED short circuit.                                                                                                                                                                                                            |

| 11                                                 | ISENSE+                          | Positive LED Current-Sense Input. The voltage between ISENSE+ and ISENSE- is proportionally regulated to the lesser of V <sub>ICTRL</sub> or 1.23V.                                                                                                                                                                                                                                                                                                                     |

| 12                                                 | CS                               | Switching Regulator Current-Sense Input. Add a resistor from CS to switching MOSFET current-sense resistor terminal for programming slope compensation.                                                                                                                                                                                                                                                                                                                 |

| 13                                                 | PGND                             | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14                                                 | NDRV                             | External n-Channel MOSFET Gate-Driver Output                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15                                                 | V <sub>CC</sub>                  | 7V Low-Dropout Voltage Regulator Output. Bypass V <sub>CC</sub> to PGND with a 1μF (min) ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                             |

| 16                                                 | IN                               | Positive Power-Supply Input. Bypass IN to PGND with at least a 1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                   |

| _                                                  | EP                               | Exposed Pad. Connect EP to the ground plane for heat sinking. Do not use EP as the only electrical connection to ground.                                                                                                                                                                                                                                                                                                                                                |

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

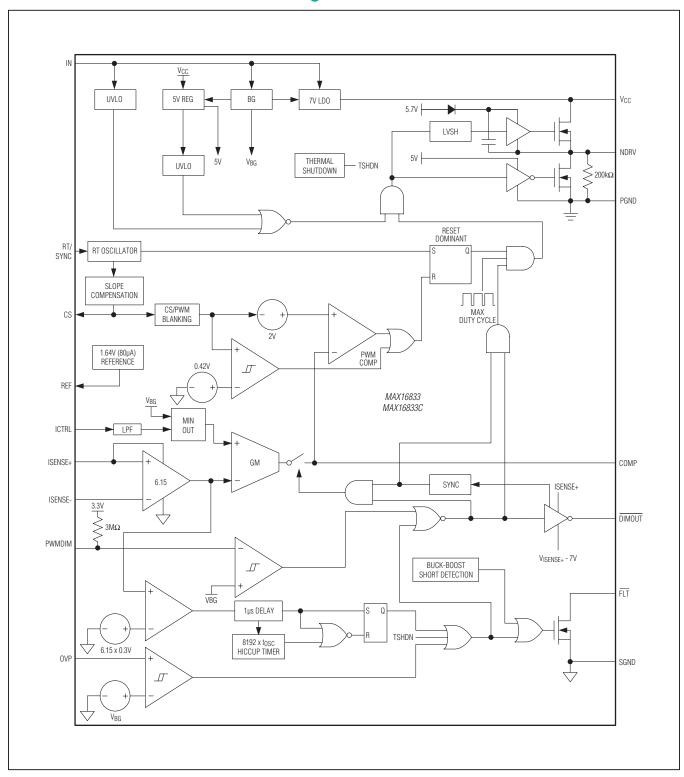

### MAX16833/MAX16833C Functional Diagram

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

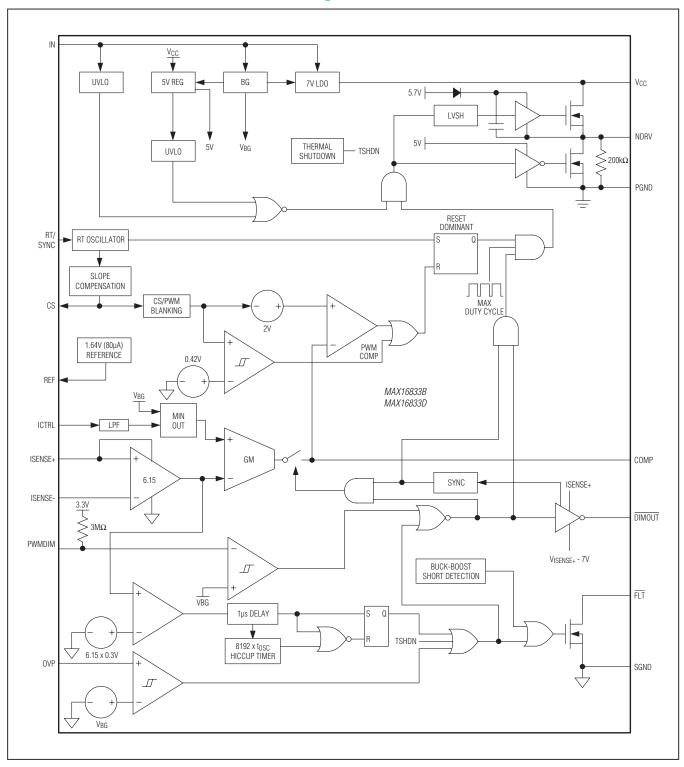

### MAX16833B/MAX16833D Functional Diagram

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

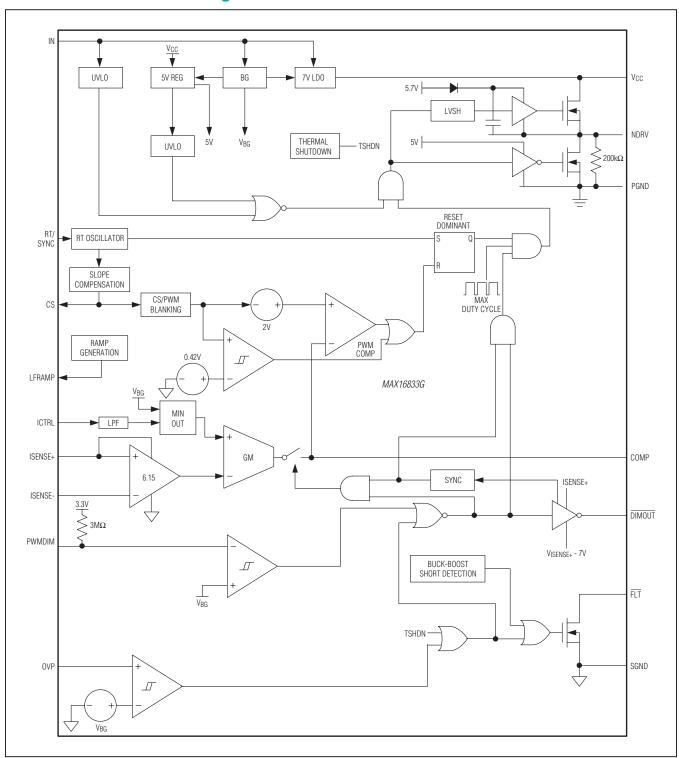

# **MAX16833G Functional Diagram**

# **Detailed Description**

The MAX16833, MAX16833B, MAX16833C, MAX16833D, and MAX16833G are peak current-mode-controlled LED drivers for boost, buck-boost, SEPIC, flyback, and highside buck topologies. A low-side gate driver capable of sinking and sourcing 3A can drive a power MOSFET in the 100kHz to 1MHz frequency range. Constant-frequency peak current-mode control is used to control the duty cycle of the PWM controller that drives the power MOSFET. Externally programmable slope compensation prevents subharmonic oscillations for duty cycles exceeding 50% when the inductor is operating in continuous conduction mode. Most of the power for the internal control circuitry inside the ICs is provided from an internal 5V regulator. The gate drive for the low-side switching MOSFET is provided by a separate V<sub>CC</sub> regulator. A dimming driver designed to drive an external p-channel in series with the LED string provides wide-range dimming control. This dimming driver is powered by a separate unconnected reference -7V regulator. This feature provides extremely fast PWM current switching to the LEDs with no transient overvoltage or undervoltage conditions. In addition to PWM dimming, the ICs provide analog dimming using a DC input at the ICTRL input.

A single resistor from RT/SYNC to ground sets the switching frequency from 100kHz to 1MHz, while an external clock signal capacitively coupled to RT/SYNC allows the ICs to synchronize to an external clock. The switching frequency can be dithered for spread-spectrum applications by connecting the LFRAMP output to RT/SYNC through an external resistor in the MAX16833/C/G. In the MAX16833B/D, the LFRAMP output is replaced by a REF output, which provides a regulated 1.64V, 2% accurate reference that can be used with a resistive divider from REF to ICTRL to set the LED current. The maximum current from the REF output cannot exceed 80µA.

Additional features include a fault-indicator output (FLT) for short, overvoltage, or overtemperature conditions and an overvoltage-protection (OVP) sense input for overvoltage protection. In case of LED string short, for a buck-boost configuration, the short-circuit current is equal to the programmed LED current. In the case of boost configuration, the ICs enter hiccup mode with automatic recovery from short circuit. In the MAX16833G, the hiccup mode is disabled. The MAX16833G should not be used in boost applications.

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

#### **UVLO**

The ICs feature undervoltage lockout (UVLO) using the positive power-supply input (IN). The ICs are enabled when V<sub>IN</sub> exceeds the 4.6V (typ) threshold and are disabled when V<sub>IN</sub> drops below the 4.35V (typ) threshold. The UVLO is internally fixed and cannot be adjusted. There is a startup delay of  $300\mu s$  (typ) + 64 switching clock cycles on power-up after the UVLO threshold is crossed. There is a  $3.3\mu s$  delay on power-down on the falling edge of the UVLO.

#### **Dimming MOSFET Driver (DIMOUT)**

The ICs require an external p-channel MOSFET for PWM dimming. For normal operation, connect the gate of the MOSFET to the output of the dimming driver (DIMOUT). The dimming driver can sink up to 25mA or source up to 50mA of peak current for fast charging and discharging of the p-MOSFET gate. When the PWMDIM signal is high, this driver pulls the p-MOSFET gate to 7V below the ISENSE+ pin to completely turn on the p-channel dimming MOSFET.

#### n-Channel MOSFET Switch Driver (NDRV)

The ICs drive an external n-channel switching MOSFET. NDRV swings between VCC and PGND. NDRV can sink/ source 3A of peak current, allowing the ICs to switch MOSFETs in high-power applications. The average current demanded from the supply to drive the external MOSFET depends on the total gate charge (QG) and the operating frequency of the converter, fsw. Use the following equation to calculate the driver supply current INDRV required for the switching MOSFET:

INDRV = QG x fsw

#### Pulse-Dimming Input (PWMDIM)

The ICs offer a dimming input (PWMDIM) for pulse-width modulating the output current. PWM dimming can be achieved by driving PWMDIM with a pulsating voltage source. When the voltage at PWMDIM is greater than 1.23V, the PWM dimming p-channel MOSFET turns on and the gate drive to the n-channel switching MOSFET is also enabled. When the voltage on PWMDIM drops 70mV below 1.23V, the PWM dimming MOSFET turns off and the n-channel switching MOSFET is also turned off. The COMP capacitor is also disconnected from the internal transconductance amplifier when PWMDIM is low. When left unconnected, a weak internal pullup resistor sets this input to logic-high.

#### **Analog Dimming (ICTRL)**

The ICs offer an analog dimming control input (ICTRL). The voltage at ICTRL sets the LED current level when VICTRL < 1.2V. The LED current can be linearly adjusted from zero with the voltage on ICTRL. For VICTRL > 1.4V, an internal reference sets the LED current. The maximum withstand voltage of this input is 5.5V.

#### Low-Side Linear Regulator (V<sub>CC</sub>)

The ICs feature a 7V low-side linear regulator (VCC). VCC powers up the switching MOSFET driver with sourcing capability of up to 50mA. Use a 1 $\mu$ F (min) low-ESR ceramic capacitor from VCC to PGND for stable operation. The VCC regulator goes below 7V if the input voltage falls below 7V. The dropout voltage for this regulator at 50mA is 0.2V. This means that for an input voltage of 5V, the VCC voltage is 4.8V. The short-circuit current on the VCC regulator is 100mA (typ). Connect VCC to IN if VIN is always less than 7V.

#### LED Current-Sense Inputs (ISENSE±)

The differential voltage from ISENSE+ to ISENSE- is fed to an internal current-sense amplifier. This amplified signal is then connected to the negative input of the transconductance error amplifier. The voltage-gain factor of this amplifier is 6.15.

The offset voltage for this amplifier is  $\leq 1$ mV.

#### **Internal Transconductance Error Amplifier**

The ICs have a built-in transconductance amplifier used to amplify the error signal inside the feedback loop. When the dimming signal is low, COMP is disconnected from the output of the error amplifier and \$\overline{\text{DIMOUT}}\$ goes high. When the dimming signal is high, the output of the error amplifier is connected to COMP and \$\overline{\text{DIMOUT}}\$ goes low. This enables the compensation capacitor to hold the charge when the dimming signal has turned off the internal switching MOSFET gate drive. To maintain the charge on the compensation capacitor CCOMP (C4 in the Typical Operating Circuits), the capacitor should be a low-leakage ceramic type. When the internal dimming signal is enabled, the voltage on the compensation capacitor forces the converter into steady state almost instantaneously.

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

#### Internal Oscillator (RT/SYNC)

The internal oscillators of the ICs are programmable from 100kHz to 1MHz using a single resistor at RT/SYNC. Use the following formula to calculate the switching frequency:

$$\begin{split} f_{OSC} \; (kHz) &= \frac{7350 \; (k\Omega)}{R_{RT}(k\Omega)} \; \text{for the MAX16833/B} \\ f_{OSC} \; (kHz) &= \frac{6929 (k\Omega)}{R_{RT}(k\Omega)} \; \text{for the MAX16833C/D/G} \end{split}$$

where RRT is the resistor from RT/SYNC to SGND.

Synchronize the oscillator with an external clock by AC-coupling the external clock to the RT/SYNC input. For fOSC between 200kHz and 1MHz, the capacitor used for the AC-coupling should satisfy the following relation:

$$C_{SYNC} \le \frac{9.8624 \times 10^{-6}}{R_{RT}} - 0.144 \times 10^{-9} \text{ farads}$$

where RRT is in k $\Omega$ . For fOSC below 200GHz, CSYNC  $\leq$  268nF.

The pulse width for the synchronization pulse should satisfy the following relations:

$$\frac{t_{PW}}{t_{CLK}} < \frac{0.5}{V_S} \quad \text{and} \quad \frac{t_{PW}}{t_{CLK}} < \left(1 - \frac{1.05 \times t_{CLK}}{t_{OSC}}\right)$$

$$3.4V < \left(0.8 - \frac{t_{PW}}{t_{CLK}}V_S\right) + V_S < 5V$$

where tpw is the synchronization source pulse width, tCLK is the synchronization clock time period, tOSC is the free-running oscillator time period, and Vs is the synchronization pulse-voltage level.

Ensure that the external clock signal frequency is at least 1.1 x fosc, where fosc is the oscillator frequency set by RRT. A typical pulse width of 200ns can be used for proper synchronization of a frequency up to 250kHz. A rising external clock edge (sync) is interpreted as a synchronization input. If the sync signal is lost, the internal oscillator takes control of the switching rate returning the switching frequency to that set by RRT. This maintains output regulation even with intermittent sync signals.

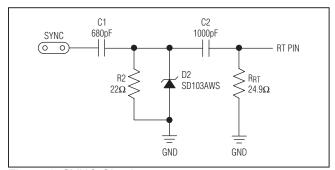

Figure 1 shows the frequency-synchronization circuit suitable for applications where a 5V amplitude pulse with 20% to 80% duty cycle is available as the synchronization source. This circuit can be used for SYNC frequencies in the 100kHz to 1MHz range. C1 and R2 act as a differentiator that reduces the input pulse width to suit the ICs' RT/ SYNC input. D2 bypasses the negative current through C1 at the falling edge of the SYNC source to limit the minimum voltage at the RT/SYNC pin. The differentiator output is AC-coupled to the RT/SYNC pin through C2.

The output impedance of the SYNC source should be low enough to drive the current through R2 on the rising edge. The rise/fall times of the SYNC source should be less than 50ns to avoid excessive voltage drop across C1 during the rise time. The amplitude of the SYNC source can be between 4V and 5V. If the SYNC source amplitude is 5V and the rise time is less than 20ns, then the maximum peak voltage at RT/SYNC pin can get close to 6V. Under such conditions, it is desirable to use a resistor in series with C1 to reduce the maximum voltage at the RT/SYNC pin. For proper synchronization, the peak SYNC pulse voltage at RT/SYNC pin should exceed 3.8V.

# Frequency Dithering (LFRAMP/MAX16833/MAX16833C/MAX16833G)

The MAX16833/MAX16833C/MAX16833G feature a low-frequency ramp output. Connect a capacitor from LFRAMP to ground to program the ramp frequency. Connect to SGND if not used. A resistor can be connected between LFRAMP and RT/SYNC to dither the PWM switching frequency to achieve spread spectrum. A lower value resistor provides a larger amount of frequency dithering. The LFRAMP voltage is a triangular waveform between 1V (typ) and 2V (typ). The ramp frequency is given by:

$$f_{LFRAMP}(Hz) \ = \frac{50FA}{C_{LFRAMP}(F)}$$

Figure 1. SYNC Circuit

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

# Voltage-Reference Output (REF/MAX16833B/MAX16833D)

The MAX16833B/D have a 2% accurate 1.64V reference voltage on the REF output. Connect a 1µF ceramic capacitor from REF to SGND to provide a stable reference voltage. This reference can supply up to  $80\mu A$ . This output can drive a resistive divider to the ICTRL input for analog dimming. The resistance from REF to ground should be greater than  $20.5k\Omega$ .

#### **Switching MOSFET Current-Sense Input (CS)**

CS is part of the current-mode control loop. The switching control uses the voltage on CS, set by RCS (R4 in the Typical Operating Circuits) and RSLOPE (R1 in the Typical Operating Circuits), to terminate the on-pulse width of the switching cycle, thus achieving peak current-mode control. Internal leading-edge blanking of 50ns is provided to prevent premature turn-off of the switching MOSFET in each switching cycle. Resistor RCS is connected between the source of the n-channel switching MOSFET and PGND.

During switching, a current ramp with a slope of 50FA x fsw is sourced from the CS input. This current ramp, along with resistor RSLOPE, programs the amount of slope compensation.

#### Overvoltage-Protection Input (OVP)

OVP sets the overvoltage-threshold limit across the LEDs. Use a resistive divider between ISENSE+ to OVP and SGND to set the overvoltage-threshold limit. An internal overvoltage-protection comparator senses the differential voltage across OVP and SGND. If the differential voltage is greater than 1.23V, NDRV goes low,  $\overline{\text{DIMOUT}}$  goes high, and  $\overline{\text{FLT}}$  asserts. When the differential voltage drops by 70mV, NDRV is enabled,  $\overline{\text{DIMOUT}}$  goes low, and  $\overline{\text{FLT}}$  deasserts.

### Fault Indicator (FLT)

The ICs feature an active-low, open-drain fault indicator  $(\overline{\text{FLT}})$ .  $\overline{\text{FLT}}$  goes low when one of the following conditions occur:

- Overvoltage across the LED string

- Short-circuit condition across the LED string

- Overtemperature condition

FLT goes high when the fault condition ends.

#### **Thermal Protection**

The ICs feature thermal protection. When the junction temperature exceeds +160°C, the ICs turn off the external power MOSFETs by pulling the NDRV low and DIMOUT high. External MOSFETs are enabled again after the junction temperature has cooled by 10°C. This results in a cycled output during continuous thermal-overload conditions. Thermal protection protects the ICs in the event of fault conditions.

#### **Short-Circuit Protection**

#### **Boost Configuration (MAX16833/B/C/D only)**

In the boost configuration, if the LED string is shorted it causes the (ISENSE+ to ISENSE-) voltage to exceed 300mV. If this condition occurs for  $\geq$  1 $\mu$ s, the ICs activates the hiccup timer for 8192 clock cycles during which:

- NDRV goes low and DIMOUT goes high.

- The error amplifier is disconnected from COMP.

- FLT is pulled to SGND.

After the hiccup time has elapsed, the ICs retry. During this retry period,  $\overline{\text{FLT}}$  is latched and is reset only if there is no short detected after 20µs of retrying. The MAX16833G does not have the hiccup protection and should not be used for boost applications.

#### **Buck-Boost Configuration**

In the case of the buck-boost configuration, once an LED string short occurs, the behavior is different. The ICs maintain the programmed current across the short. In this case, the short is detected when the voltage between ISENSE+ and IN falls below 1.5V. A buck-boost short fault starts an up counter and  $\overline{\text{FLT}}$  is asserted only after the counter has reached 8192 clock cycles consecutively. If for any reason (VISENSE+ - VIN > 1.5V), the counter starts down counting, resulting in  $\overline{\text{FLT}}$  being deasserted only after 8192 consecutive clock cycles of (VISENSE+ - VIN > 1.5V) condition.

#### **Exposed Pad**

The ICs' package features an exposed thermal pad on its underside that should be used as a heatsink. This pad lowers the package's thermal resistance by providing a direct heat-conduction path from the die to the PCB. Connect the exposed pad and GND to the system ground using a large pad or ground plane, or multiple vias to the ground plane layer.

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

### **Applications Information**

#### **Setting the Overvoltage Threshold**

The overvoltage threshold is set by resistors R5 and R11 (see the Typical Operating Circuits). The overvoltage circuit in the ICs is activated when the voltage on OVP with respect to GND exceeds 1.23V. Use the following equation to set the desired overvoltage threshold:

$$V_{OV} = 1.23V (R5 + R11)/R11$$

#### **Programming the LED Current**

Normal sensing of the LED current should be done on the high side where the LED current-sense resistor is connected to the boost output. The other side of the LED current-sense resistor goes to the source of the p-channel dimming MOSFET if PWM dimming is desired. The LED current is programmed using R7. When VICTRL > 1.23V, the internal reference regulates the voltage across R7 to 200mV:

$$I_{LED} = \frac{200mV}{R7}$$

The LED current can also be programmed using the voltage on ICTRL when V<sub>ICTRL</sub> < 1.2V (analog dimming). The voltage on ICTRL can be set using a resistive divider from the REF output in the case of the MAX16833B/D. The current is given by:

$$I_{LED} = \frac{V_{ICTRL}}{R7 \times 6.15}$$

where:

$$V_{ICTRL} = \frac{V_{REF} \times R8}{(R8 + R9)}$$

where V<sub>REF</sub> is 1.64V and resistors R8 and R9 are in ohms. At higher LED currents, there can be noticeable ripple on the voltage across R7. High-ripple voltages can cause a noticeable difference between the programmed value of the LED current and the measured value of the LED current. To minimize this error, the ripple voltage across R7 should be less than 40mV.

#### **Inductor Selection**

#### **Boost Configuration**

In the boost converter (see the Typical Operating Circuits), the average inductor current varies with the line voltage. The maximum average current occurs at the lowest line voltage. For the boost converter, the average inductor current is equal to the input current. Calculate maximum duty cycle using the following equation:

$$D_{MAX} = \frac{V_{LED} + V_{D} - V_{INMIN}}{V_{LED} + V_{D} - V_{FET}}$$

where V<sub>LED</sub> is the forward voltage of the LED string in volts, V<sub>D</sub> is the forward drop of rectifier diode D1 in volts (approximately 0.6V), V<sub>INMIN</sub> is the minimum input-supply voltage in volts, and V<sub>FET</sub> is the average drain-to-source voltage of the MOSFET Q1 in volts when it is on. Use an approximate value of 0.2V initially to calculate D<sub>MAX</sub>. A more accurate value of the maximum duty cycle can be calculated once the power MOSFET is selected based on the maximum inductor current.

Use the following equations to calculate the maximum average inductor current ILAVG, peak-to-peak inductor current ripple DIL, and peak inductor current ILP in amperes:

$$IL_{AVG} = \frac{I_{LED}}{1 - D_{MAX}}$$

Allowing the peak-to-peak inductor ripple to be DIL, the peak inductor current is given by:

$$IL_P = IL_{AVG} + \frac{\Delta I_L}{2}$$

The inductance value (L) of inductor L1 in henries (H) is calculated as:

$$L = \frac{\left(V_{INMIN} - V_{FET}\right) \times D_{MAX}}{f_{SW} \times \Delta I_{L}}$$

where fsW is the switching frequency in Hertz,  $V_{INMIN}$  and  $V_{FET}$  are in volts, and  $DI_L$  is in amperes.

Choose an inductor that has a minimum inductance greater than the calculated value. The current rating of the inductor should be higher than ILP at the operating temperature.

#### **Buck-Boost Configuration**

In the buck-boost LED driver (see the Typical Operating Circuits), the average inductor current is equal to

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

the input current plus the LED current. Calculate the maximum duty cycle using the following equation:

$$D_{MAX} = \frac{V_{LED} + V_{D}}{V_{LED} + V_{D} + V_{INMIN} - V_{FET}}$$

where V<sub>LED</sub> is the forward voltage of the LED string in volts, V<sub>D</sub> is the forward drop of rectifier diode D1 (approximately 0.6V) in volts, V<sub>INMIN</sub> is the minimum input supply voltage in volts, and V<sub>FET</sub> is the average drain-to-source voltage of the MOSFET Q1 in volts when it is on. Use an approximate value of 0.2V initially to calculate D<sub>MAX</sub>. A more accurate value of maximum duty cycle can be calculated once the power MOSFET is selected based on the maximum inductor current.

Use the equations below to calculate the maximum average inductor current ILAVG, peak-to-peak inductor current ripple DIL, and peak inductor current ILP in amperes:

$$IL_{AVG} = \frac{I_{LED}}{1 - D_{MAX}}$$

Allowing the peak-to-peak inductor ripple to be DIL:

$$IL_P = IL_{AVG} + \frac{\Delta I_L}{2}$$

where ILP is the peak inductor current.

The inductance value (L) of inductor L1 in henries is calculated as:

$$L = \frac{\left(V_{INMIN} - V_{FET}\right) \times D_{MAX}}{f_{SW} \times \Delta I_{I}}$$

where fsw is the switching frequency in Hertz,  $V_{INMIN}$  and  $V_{FET}$  are in volts, and  $DI_L$  is in amperes. Choose an inductor that has a minimum inductance greater than the calculated value.

#### **High-Side Buck Configuration**

In the high-side buck LED driver, the average inductor current is the same as the LED current. The peak inductor current occurs at the maximum input line voltage where the duty cycle is at the minimum:

$$D_{MIN} = (V_{LED} + V_{D})/(V_{INMAX} - V_{FET})$$

where  $V_{LED}$  is the forward voltage of the LED string in volts,  $V_D$  is the forward drop of rectifier diode D1 (~0.6V) in volts,  $V_{INMAX}$  is the maximum input supply voltage in volts, and  $V_{FET}$  is the average drain-

to-source voltage of MOSFET N1 in volts when it is on. Use an approximate value of 0.2V initially to calculate  $D_{MIN}$ . The maximum peak-to-peak inductor ripple ( $\Delta IL$ ) occurs at the maximum input line. The peak inductor current is given by:

$$I_{LP} = I_{LED} + 0.5 \times \Delta IL$$

The inductance value (L) of inductor L1 in henries is calculated as follows:

$$L = (V_{INMAX} - V_{FET} - V_{LED}) \times D_{MIN}/(f_{SW} \times \Delta IL)$$

where  $f_{SW}$  is the switching frequency in Hertz,  $V_{INMAX}$  and  $V_{FET}$  are in volts, and  $\Delta IL$  is in amperes. Choose an inductor that has a minimum inductance greater than the calculated value.

#### Peak Current-Sense Resistor (R4)

The value of the switch current-sense resistor R4 for the boost and buck-boost configurations is calculated as follows:

$$R4 = \frac{0.418V - V_{SC}}{IL_{P}} \Omega$$

where ILp is the peak inductor current in amperes and VSC is the peak slope compensation voltage.

#### **Slope Compensation**

Slope compensation should be added to converters with peak current-mode control operating in continuous-conduction mode with more than 50% duty cycle to avoid current-loop instability and subharmonic oscillations. The minimum amount of slope compensation that is required for stability is:

VSCMIN = 0.5 (inductor current downslope - inductor current upslope) x R4

In the ICs, the slope-compensating ramp is added to the current-sense signal before it is fed to the PWM comparator. Connect a resistor (R1) from CS to the inductor current-sense resistor terminal to program the amount of slope compensation.

The ICs generate a current ramp with a slope of  $50\mu\text{A/}$  tosc for slope compensation. The current-ramp signal is forced into the external resistor (R1) connected between CS and the source of the external MOSFET, thereby adding a programmable slope compensating voltage (VSCOMP) at the current-sense input CS. Therefore:

$$dV_{SC}/dt = (R1 \times 50\mu A)/t_{OSC}$$

in V/s

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

The minimum value of the slope-compensation voltage that needs to be added to the current-sense signal at peak current and at minimum line voltage is:

$$SC_{MIN} = \frac{(D_{MAX} \times (V_{LED} - 2V_{INMIN}) \times R4)}{2 \times L_{MIN} \times f_{SW}} (V) Boost$$

$$SC_{MIN} = \frac{(D_{MAX} \times (V_{LED} - V_{INMIN}) \times R4)}{2 \times L_{MIN} \times f_{SW}} \text{ (V)} Buck-boost$$

For high-side buck LED driver:

$$SC_{MIN} = \frac{(D_{MAX} \times (2V_{LED} - V_{INMIN}) \times R_{SC})}{2 \times L_{MIN} \times f_{SW}} (V)$$

where fsW is the switching frequency, DMAX is the maximum duty cycle, which occurs at low line, VINMIN is the minimum input voltage, and LMIN is the minimum value of the selected inductor. For adequate margin, the slope-compensation voltage is multiplied by a factor of 1.5. Therefore, the actual slope-compensation voltage is given by:

From the previous formulas, it is possible to calculate the value of R4 as:

For boost configuration:

$$R4 = \frac{0.418V}{IL_P + 0.75D_{MAX} \frac{V_{LED} - 2V_{INMIN}}{L_{MIN}f_{SW}}}$$

For buck-boost configuration:

$$R4 = \frac{0.418V}{IL_P + 0.75D_{MAX} \frac{V_{LED} - V_{INMIN}}{L_{MIN}f_{SW}}}$$

For high-side buck configuration:

$$R4 = \frac{0.418V}{IL_P + 0.75D_{MAX} \frac{2V_{LED} - V_{INMIN}}{L_{MIN}f_{SW}}}$$

The minimum value of the slope-compensation resistor (R1) that should be used to ensure stable operation at minimum input supply voltage can be calculated as:

For boost configuration:

$$R1 = \frac{(V_{LED} - 2V_{INMIN}) \times R4 \times 1.5}{2 \times L_{MIN} \times f_{SW} \times 50 \mu A}$$

For buck-boost configuration:

$$R1 = \frac{(V_{LED} - V_{INMIN}) \times R4 \times 1.5}{2 \times L_{MIN} \times f_{SW} \times 50 \mu A}$$

For high-side buck configuration:

$$R1 = \frac{(2V_{LED} - V_{INMIN}) \times R4 \times 1.5}{2 \times L_{MIN} \times f_{SW} \times 50 \mu A}$$

where fsw is the switching frequency in Hertz,  $V_{INMIN}$  is the minimum input voltage in volts,  $V_{LED}$  is the LED voltage in volts,  $D_{MAX}$  is the maximum duty cycle,  $I_{LP}$  is the peak inductor current in amperes, and  $L_{MIN}$  is the minimum value of the selected inductor in henries.

#### **Output Capacitor**

The function of the output capacitor is to reduce the output ripple to acceptable levels. The ESR, ESL, and the bulk capacitance of the output capacitor contribute to the output ripple. In most applications, the output ESR and ESL effects can be dramatically reduced by using low-ESR ceramic capacitors. To reduce the ESL and ESR effects, connect multiple ceramic capacitors in parallel to achieve the required bulk capacitance. To minimize audible noise generated by the ceramic capacitors during PWM dimming, it could be necessary to minimize the number of ceramic capacitors on the output. In these cases, an additional electrolytic or tantalum capacitor provides most of the bulk capacitance.

#### **Boost and Buck-Boost Configurations**

The calculation of the output capacitance is the same for both boost and buck-boost configurations. The output ripple is caused by the ESR and the bulk capacitance of the output capacitor if the ESL effect is considered negligible. For simplicity, assume that the contributions from ESR and the bulk capacitance are equal, allowing 50% of the ripple for the bulk capacitance. The capacitance is given by:

$$C_{OUT} \ge \frac{I_{LED} \times 2 \times D_{MAX}}{V_{OUTRIPPLE} \times f_{SW}}$$

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

where I<sub>LED</sub> is in amperes, C<sub>OUT</sub> is in farads, f<sub>SW</sub> is in Hertz, and V<sub>OUTRIPPLE</sub> is in volts. The remaining 50% of allowable ripple is for the ESR of the output capacitor.

Based on this, the ESR of the output capacitor is given by:

$$\mathsf{ESR}_{COUT} < \frac{\mathsf{V}_{OUTRIPPLE}}{(\mathsf{IL}_{P} \times 2)} (\Omega)$$

where ILP is the peak-inductor current in amperes. Use the equation below to calculate the RMS current rating of the output capacitor:

$$I_{COUT(RMS)} = \sqrt{IL_{AVG}^2D_{MAX}(1-D_{MAX})}$$

The output capacitor for the high-side buck configuration is chosen such that most of the ripple current through the inductor is shunted through the output capacitor. The inductor ripple current splits into the output capacitance and the LEDs. The proportionality depends on the impedance of the output capacitor at the switching frequency and the dynamic resistance of the LEDs. Typically, capacitance is sized such that 10% of the inductor ripple current flows into the LEDs. For most applications, an output capacitance of  $1\mu F$  to  $2.2\mu F$  should be sufficient.

#### **Input Capacitor**

The input-filter capacitor bypasses the ripple current drawn by the converter and reduces the amplitude of high-frequency current conducted to the input supply. The ESR, ESL, and the bulk capacitance of the input capacitor contribute to the input ripple. Use a low-ESR input capacitor that can handle the maximum input RMS ripple current from the converter. For the boost configuration, the input current is the same as the inductor current. For buck-boost configuration, the input current is the inductor current minus the LED current. However, for both configurations, the ripple current that the input filter capacitor has to supply is the same as the inductor ripple current with the condition that the output filter capacitor should be connected to ground for buckboost configuration. This reduces the size of the input capacitor, as the input current is continuous with maximum QDIL/2. Neglecting the effect of LED current ripple, the calculation of the input capacitor for boost, as well as buck-boost configurations is the same.

Neglecting the effect of the ESL, the ESR, and the bulk capacitance at the input contribute to the input-voltage ripple. For simplicity, assume that the contributions from the ESR and the bulk capacitance are equal. This allows 50% of the ripple for the bulk capacitance. The capacitance is given by:

$$C_{IN} \ge \frac{\Delta I_L}{4 \times \Delta V_{IN} \times f_{SW}}$$

where DIL is in amperes, CIN is in farads, fsW is in Hertz, and DVIN is in volts. The remaining 50% of allowable ripple is for the ESR of the input capacitor. Based on this, the ESR of the input capacitor is given by:

$$\mathsf{ESR}_{CIN} < \frac{\Delta V_{IN}}{\Delta I_{I} \times 2}$$

where DIL is in amperes, ESRCIN is in ohms, and DVIN is in volts. Use the equation below to calculate the RMS current rating of the input capacitor:

$$I_{CIN}(RMS) = \frac{\Delta I_L}{2\sqrt{3}}$$

In buck mode, the input capacitor has large pulsed currents due to the current flowing in the freewheeling diode when the switching MOSFET is off. It is very important to consider the ripple-current rating of the input capacitor in this application.

For low-ESR input capacitors, size C<sub>IN</sub> using the following formula:

$$C_{IN} = \frac{I_{LOAD}}{f_{SW} \times \Delta V_{IN\_RIPPLE}} \quad x \quad \frac{V_{OUT}}{V_{IN}}$$

# Selection of Power Semiconductors Switching MOSFET

The switching MOSFET (Q1) should have a voltage rating sufficient to withstand the maximum output voltage together with the diode drop of rectifier diode D1 and any possible overshoot due to ringing caused by parasitic inductances and capacitances. Use a MOSFET with a drain-to-source voltage rating higher than that calculated by the following equations.

#### **Boost Configuration**

$$V_{DS} = (V_{LED} + V_{D}) \times 1.2$$

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

where V<sub>DS</sub> is the drain-to-source voltage in volts and V<sub>D</sub> is the forward drop of rectifier diode D1. The factor of 1.2 provides a 20% safety margin.

#### **Buck-Boost Configuration**

where  $V_{DS}$  is the drain-to-source voltage in volts and  $V_{D}$  is the forward drop of rectifier diode D1. The factor of 1.2 provides a 20% safety margin.

The RMS current rating of the switching MOSFET Q1 is calculated as follows for boost and buck-boost configurations:

$$I_{DRMS} = 1.3 \times (\sqrt{(IL_{AVG})^2 \times D_{MAX}})$$

where IDRMS is the MOSFET Q1's drain RMS current in amperes.

The MOSFET Q1 dissipates power due to both switching losses and conduction losses. The conduction losses in the MOSFET are calculated as follows:

where RDSON is the on-resistance of Q1 in ohms, PCOND is in watts, and ILAVG is in amperes. Use the following equations to calculate the switching losses in the MOSFET.

#### **Boost Configuration**

$$P_{SW} = \left(\frac{IL_{AVG} \times V_{LED}^{2} \times C_{GD} \times f_{SW}}{2}\right)$$

$$\times \left(\frac{1}{IG_{ON}} + \frac{1}{IG_{OFF}}\right)$$

#### **Buck-Boost Configuration**

$$\begin{aligned} P_{SW} = & \left( \frac{IL_{AVG} \times (V_{LED} + V_{INMAX})^2 \times C_{GD} \times f_{SW}}{2} \right) \\ & \times \left( \frac{1}{IG_{ON}} + \frac{1}{IG_{OFF}} \right) \end{aligned}$$

where IGON and IGOFF are the gate currents of the MOSFET Q1 in amperes when it is turned on and turned off, respectively, V<sub>LED</sub> and V<sub>INMAX</sub> are in volts, IL<sub>AVG</sub> is in amperes, f<sub>SW</sub> is in Hertz, and C<sub>GD</sub> is the gate-to-drain MOSFET capacitance in farads.

#### **Rectifier Diode**

Use a Schottky diode as the rectifier (D1) for fast switching and to reduce power dissipation. The selected Schottky diode must have a voltage rating 20% above the maximum converter output voltage. The maximum converter output voltage is VLED in boost configuration and VLED + VINMAX in buck-boost configuration.

The current rating of the diode should be greater than ID in the following equation:

$$ID = ILAVG x (1 - DMAX) x 1.5$$

#### **Dimming MOSFET**

Select a dimming MOSFET (Q2) with continuous current rating at the operating temperature higher than the LED current by 30%. The drain-to-source voltage rating of the dimming MOSFET must be higher than V<sub>LED</sub> by 20%.

#### **Feedback Compensation**

The LED current-control loop comprising the switching converter, the LED current amplifier, and the error amplifier should be compensated for stable control of the LED current. The switching converter small-signal transfer function has a right-half-plane (RHP) zero for both boost and buck-boost configurations as the inductor current is in continuous conduction mode. The RHP zero adds a 20dB/decade gain together with a 90-degree phase lag, which is difficult to compensate. The easiest way to avoid this zero is to roll off the loop gain to 0dB at a frequency less than 1/5 the RHP zero frequency with a -20dB/decade slope.

The worst-case RHP zero frequency ( $f_{ZRHP}$ ) is calculated as follows:

#### **Boost Configuration**

$$f_{ZRHP} = \frac{V_{LED} \times (1 - D_{MAX})^2}{2\pi \times L \times I_{LED}}$$

#### **Buck-Boost Configuration**

$$f_{ZRHP} = \frac{V_{LED} \times (1 - D_{MAX})^2}{2\pi \times L \times I_{LED} \times D_{MAX}}$$

where fzrhp is in Hertz, VLED is in volts, L is the inductance value of L1 in henries, and ILED is in amperes.

# High-Voltage HB LED Drivers with Integrated High-Side Current Sense

The switching converter small-signal transfer function also has an output pole for both boost and buck-boost configurations. The effective output impedance that determines the output pole frequency together with the output filter capacitance is calculated as follows:

#### **Boost Configuration**

$$R_{OUT} = \frac{(R_{LED} + R7) \times V_{LED}}{(R_{LED} + R7) \times I_{LED} + V_{LED}}$$

#### **Buck-Boost Configuration**

$$R_{OUT} = \frac{(R_{LED} + R7) \times V_{LED}}{(R_{LED} + R7) \times I_{LED} \times D_{MAX} + V_{LED}}$$