# MAX6866UK46D3S+T Datasheet

www.digi-electronics.com

DiGi Electronics Part Number Manufacturer Manufacturer Product Number Description Detailed Description MAX6866UK46D3S+T-DG Analog Devices Inc./Maxim Integrated MAX6866UK46D3S+T IC SUPERVISOR 1 CHANNEL SOT23-5 Supervisor Push-Pull, Totem Pole 1 Channel SOT-2 3-5

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# Purchase and inquiry

| Manufacturer Product Number:   | Manufacturer:                        |

|--------------------------------|--------------------------------------|

| MAX6866UK46D3S+T               | Analog Devices Inc./Maxim Integrated |

| Series:                        | Product Status:                      |

| -                              | Obsolete                             |

| DiGi-Electronics Programmable: | Туре:                                |

| Not Verified                   | Simple Reset/Power-On Reset          |

| Number of Voltages Monitored:  | Voltage - Threshold:                 |

| 1                              | 4.625V                               |

| Output:                        | Reset:                               |

| Push-Pull, Totem Pole          | Active Low                           |

| Reset Timeout:                 | Operating Temperature:               |

| 150ms Minimum                  | -40°C ~ 85°C (TA)                    |

| Mounting Type:                 | Package / Case:                      |

| Surface Mount                  | SC-74A, SOT-753                      |

| Supplier Device Package:       | Base Product Number:                 |

| SOT-23-5                       | MAX6866                              |

# **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

### **General Description**

The MAX6854/MAX6855/MAX6856/MAX6858/MAX6860–MAX6869 ultra-low-current (170nA, typ) microprocessor ( $\mu$ P) supervisory circuits combine voltage monitoring, watchdog timer, and manual reset input functions in a 5-pin SOT23 package. These devices assert a reset signal whenever the monitored voltage drops below the factory-trimmed reset threshold voltage, manual reset is asserted, or the watchdog timer expires. The reset output remains asserted for a minimum timeout period after V<sub>CC</sub> rises above the reset threshold and manual reset is deasserted. Factory-trimmed reset threshold voltages are offered from +1.575V to +4.625V in approximately 100mV increments (see the *Threshold Suffix Guide*). Each device is offered with six minimum reset timeout options, ranging from 10ms to 1200ms.

The MAX6854/MAX6855/MAX6856/MAX6858/MAX6860– MAX6869 are offered in a variety of configurations (see the *Selector Guide*). The MAX6854/MAX6855/MAX6856/ MAX6861–MAX6869 provide a manual reset input, MR. The MAX6864–MAX6869 offer a watchdog timer that monitors activity at the WDI input to prevent code execution errors. The MAX6864–MAX6869 offer watchdog timeout options of 3.3s or 209s (typ). The MAX6861/ MAX6862/MAX6863 feature a pin-selectable reset delay period of 10ms or 150ms (min). Push-pull active-low, push-pull active-high, and open-drain active-low reset outputs are available.

### **Applications**

Portable/Battery-Powered Equipment

PDAs/Cell Phones

MP3 Players/Pagers

Glucose Monitors/Patient Monitors

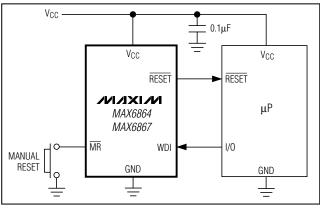

# **Typical Operating Circuit**

### \_Features

- Ultra-Low 170nA (typ) Supply Current

- Reset Thresholds from +1.575V to +4.625V in Approximately 100mV Increments

- Six Minimum Reset Timeout Period Options from 10ms to 1200ms

- Manual Reset Option

- Watchdog Timer Option

- Pin-Selectable 10ms/150ms (min) Reset Timeout Period (MAX6861/MAX6862/MAX6863)

- ♦ Immune to Short V<sub>CC</sub> Transients

- ♦ Guaranteed Reset Valid to V<sub>CC</sub> = +1.1V

- Three Reset <u>Output</u> Options: Push-Pull RESET Push-Pull RESET Open-Drain RESET

- No External Components

- Small 5-Pin SOT23 Package

- Pin Compatible to the TPS3836/TPS3837/TPS3838 (MAX6861/MAX6862/MAX6863)

### **Ordering Information**

| PART <sup>†</sup> | TEMP RANGE     | PIN-PACKAGE |

|-------------------|----------------|-------------|

| MAX6854UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6855UKDT       | -40°C to +85°C | 5 SOT23-5   |

†Insert reset threshold suffix (see Table 2, Threshold Suffix Guide) after UK. Insert the number corresponding to the desired reset timeout period (see Table 4, Reset Timeout Period) after D.

**Note:** Sample stock is generally held on standard versions only (see Table 5, Standard Versions Table). Standard versions have an order increment of 2500 pieces. Nonstandard versions have an order increment of 10,000 pieces. Contact factory for availability of nonstandard versions.

Devices are available in both leaded and lead-free packaging. Specify lead-free by replacing "-T" with "+T" when ordering.

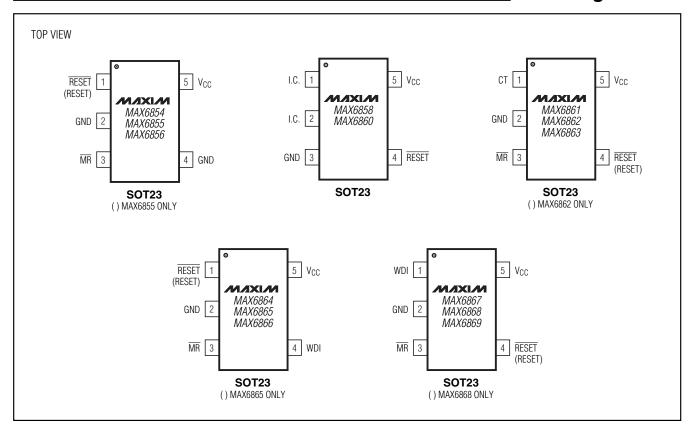

Pin Configurations and Selector Guide appear at end of data sheet.

Ordering Information continued at end of data sheet.

#

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 1.2V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise specified. Typical values are at } V_{CC} = 2.5V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                           | SYMBOL            | COND                                                                                                         | ITIONS               | MIN                       | ТҮР             | МАХ                       | UNITS            |

|-------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|-----------------|---------------------------|------------------|

| Supply Voltage                      |                   | T <sub>A</sub> ≥0°C                                                                                          |                      | 1.1                       |                 | 5.5                       | v                |

| Supply Voltage                      | Vcc               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                                |                      | 1.2                       |                 | 5.5                       | v                |

|                                     |                   | V <sub>CC</sub> > V <sub>TH</sub> , no load,                                                                 | $V_{CC} = 5.0V$      |                           | 210             | 400                       | nA               |

| Supply Current                      |                   | reset output                                                                                                 | $V_{CC} = 3.3V$      |                           | 190             | 380                       |                  |

| Supply Current                      | ICC               | deasserted (Note 2)                                                                                          | $V_{CC} = 1.8V$      |                           | 170             | 370                       |                  |

|                                     |                   | V <sub>CC</sub> < V <sub>TH</sub> , no load, r                                                               | eset output asserted |                           | 7               | 15                        | μA               |

| V <sub>CC</sub> Reset Threshold     | V <sub>TH</sub>   | V <sub>CC</sub> falling (see Table                                                                           | e 2)                 | V <sub>TH</sub> -<br>2.5% | V <sub>TH</sub> | V <sub>TH</sub> +<br>2.5% | V                |

| Reset Threshold Hysteresis          | V <sub>HYST</sub> | Reset asserted to res                                                                                        | et deasserted        |                           | 0.5             |                           | %V <sub>TH</sub> |

|                                     |                   |                                                                                                              | D1                   | 10                        | 15              | 25                        |                  |

|                                     |                   |                                                                                                              | D2                   | 40                        | 60              | 80                        | ms               |

| Reset Timeout Period                | t==               | $V_{CC} = V_{TH} + 150 mV$                                                                                   | D3                   | 150                       | 225             | 300                       |                  |

| Reset Timeout Penod                 | t <sub>RP</sub>   | (Figures 2 and 3)                                                                                            | D4                   | 1200                      | 1800            | 2400                      |                  |

|                                     |                   |                                                                                                              | D5                   | 300                       | 450             | 600                       |                  |

|                                     |                   |                                                                                                              | D6                   | 600                       | 900             | 1200                      |                  |

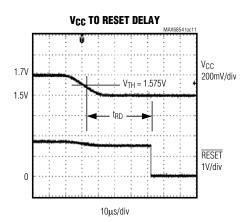

| V <sub>CC</sub> to Reset Delay      | <sup>t</sup> RD   | V <sub>CC</sub> falling from (V <sub>TH</sub> + 100mV) to<br>(V <sub>TH</sub> - 100mV) at 10mV/µs            |                      |                           | 40              |                           | μs               |

|                                     |                   | $V_{CC} \ge 1.1V$ , $I_{SINK} = 5$<br>RESET asserted, $T_A \ge 100$                                          |                      |                           |                 | 0.3                       |                  |

|                                     | Vol               | $V_{CC} \ge 1.2V$ , $I_{SINK} = 100\mu A$ ,<br>RESET asserted                                                |                      |                           |                 | 0.3                       |                  |

| RESET Output Voltage                |                   | $V_{CC} \ge 2.12V$ , $I_{SINK} = 1.2mA$ ,<br>RESET asserted                                                  |                      |                           |                 | 0.3                       | V                |

|                                     |                   | $V_{CC} \ge 1.71V$ , $I_{SOURCE} = 200\mu A$ ,<br>RESET deasserted, push-pull RESET only                     |                      | 0.8 x V <sub>CC</sub>     |                 |                           |                  |

|                                     | V <sub>OH</sub>   | $V_{CC} \ge 2.38V$ , $I_{SOURCE} = 500\mu A$ ,<br>RESET deasserted, push-pull RESET only $0.8 \times V_{CC}$ |                      |                           |                 |                           |                  |

| Open-Drain RESET Leakage<br>Current | ILKG              | RESET deasserted                                                                                             |                      |                           |                 | 25                        | nA               |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 1.2V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise specified. Typical values are at } V_{CC} = 2.5V, T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER               | SYMBOL           | CONDITIONS                                                                           | MIN                   | ТҮР | MAX                   | UNITS |

|-------------------------|------------------|--------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

|                         |                  | $V_{CC} \ge 1.1V$ , $I_{SOURCE} = 10\mu A$ ,<br>RESET asserted, $T_A \ge 0^{\circ}C$ | 0.8 × V <sub>CC</sub> |     |                       |       |

|                         | Ver              | $V_{CC} \ge 1.2V$ , $I_{SOURCE} = 10\mu A$ , RESET asserted                          | 0.8 x V <sub>CC</sub> |     |                       |       |

|                         | Vон              | $V_{CC} \ge 1.53V$ , $I_{SOURCE} = 200\mu A$ , RESET asserted                        | 0.8 x V <sub>CC</sub> |     |                       | v     |

| RESET Output Voltage    |                  | $V_{CC} \ge 2.12V$ , $I_{SOURCE} = 500\mu A$ , RESET asserted                        | 0.8 x V <sub>CC</sub> |     |                       | V     |

|                         | Vo               | $V_{CC} \ge 1.71V$ , $I_{SINK} = 500\mu A$ , RESET deasserted                        |                       |     | 0.3                   |       |

|                         | V <sub>OL</sub>  | $V_{CC} \ge 2.38V$ , $I_{SINK} = 1.2mA$ , RESET deasserted                           |                       |     | 0.3                   |       |

| CT Input Current        |                  | $CT = GND \text{ or } V_{CC}$                                                        |                       |     | 20                    | nA    |

| CT Input Voltage        | VIH              |                                                                                      | 0.8 × V <sub>CC</sub> |     |                       | V     |

| CT input voltage        | VIL              |                                                                                      |                       |     | 0.2 x V <sub>CC</sub> | v     |

| MANUAL RESET INPUT      |                  |                                                                                      |                       |     |                       | -     |

| MR Input Voltage        | VIH              |                                                                                      | 0.7 x V <sub>CC</sub> |     |                       | V     |

| Witt input Voltage      | VIL              |                                                                                      |                       |     | 0.3 x V <sub>CC</sub> | v     |

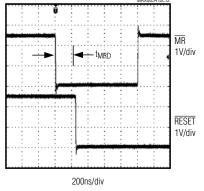

| MR Minimum Pulse Width  | t <sub>MPW</sub> |                                                                                      | 1                     |     |                       | μs    |

| MR Glitch Rejection     |                  |                                                                                      |                       | 200 |                       | ns    |

| MR to Reset Delay       | t <sub>MRD</sub> |                                                                                      |                       | 250 |                       | ns    |

| MR Pullup Resistance    |                  |                                                                                      | 5                     | 10  | 20                    | kΩ    |

| WATCHDOG TIMER (MAX6864 | -MAX6869)        |                                                                                      |                       |     |                       |       |

| WDI Input Voltage       | VIH              |                                                                                      | 0.7 x V <sub>CC</sub> |     |                       | v     |

|                         | VIL              |                                                                                      |                       |     | 0.3 x V <sub>CC</sub> | v     |

| WDI Input Current       |                  | WDI = GND or $V_{CC}$                                                                |                       |     | 20                    | nA    |

| WDI Pulse Width         | twdi             | (Note 3)                                                                             | 150                   |     |                       | ns    |

| Watchdog Timeout Period | t <sub>WD</sub>  | S                                                                                    | 1.5                   | 3.3 | 7.75                  | s     |

|                         | 400              | L                                                                                    | 95                    | 209 | 487                   | Ŭ     |

**Note 1:** Devices are tested at  $T_A = +25^{\circ}$ C. Specifications for  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C are guaranteed by design.

Note 2: For the MAX6864–MAX6869, the watchdog period is 1s with tRISE and tFALL < 50ns.

Note 3: Guaranteed by design.

4

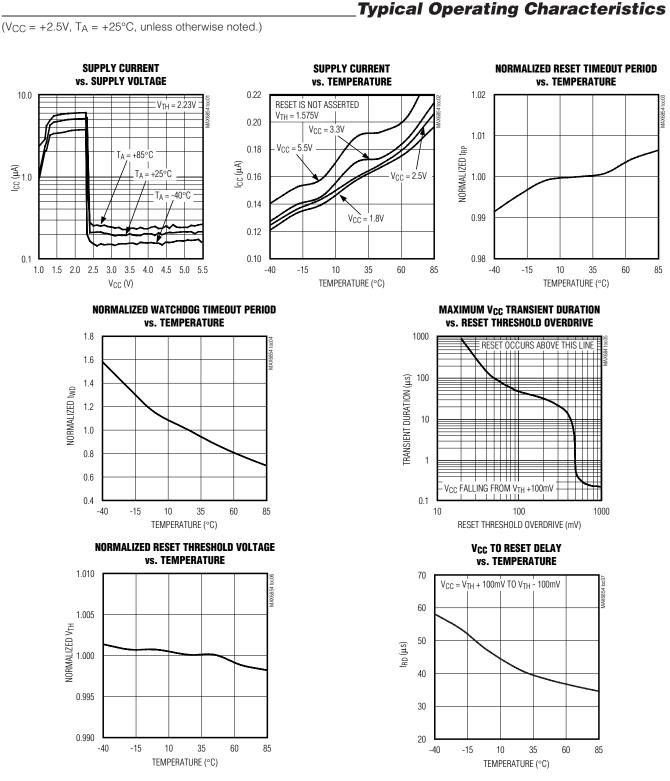

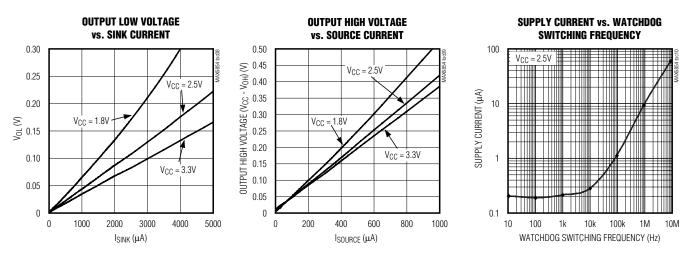

### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = +2.5V,  $T_A$  = +25°C, unless otherwise noted.)

MANUAL RESET DELAY

MAX6854/MAX6855/MAX6856/MAX6858/MAX6860-MAX6869

### \_MAX6854/MAX6855/MAX6856 Pin Description

| PI                  | N       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6854/<br>MAX6856 | MAX6855 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1                   | _       | RESET           | Active-Low Open-Drain or Push-Pull Reset Output. RESET transitions from high to low when V <sub>CC</sub> drops below the selected reset threshold or $\overline{\text{MR}}$ is pulled low. RESET remains low for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold and $\overline{\text{MR}}$ deasserts. Push-pull RESET outputs are referenced to V <sub>CC</sub> . Open-drain RESET outputs require an external pullup resistor. |

| 2, 4                | 2, 4    | GND             | Ground. Connect all GND inputs to the same potential.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                   | 3       | MR              | Active-Low Manual Reset Input. Drive $\overline{\text{MR}}$ low to initiate a reset. The reset output remains asserted while $\overline{\text{MR}}$ is held low and for the reset timeout period after $\overline{\text{MR}}$ transitions high. Leave $\overline{\text{MR}}$ unconnected or connect to V <sub>CC</sub> if unused. $\overline{\text{MR}}$ is internally pulled up to V <sub>CC</sub> through 10k $\Omega$ .                                         |

| 5                   | 5       | V <sub>CC</sub> | Supply Voltage. Input for $V_{CC}$ reset monitor. For noisy systems, bypass $V_{CC}$ with a 0.1 $\mu F$ capacitor to GND.                                                                                                                                                                                                                                                                                                                                          |

| _                   | 1       | RESET           | Active-High Push-Pull Reset Output. RESET transitions from low to high when V <sub>CC</sub> drops below the selected reset threshold or $\overline{\text{MR}}$ is pulled low. RESET remains high for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold and $\overline{\text{MR}}$ deasserts. RESET is referenced to V <sub>CC</sub> .                                                                                              |

| PIN                 |                 |                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX6858/<br>MAX6860 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                        |  |

| 1, 2                | I.C.            | Internally Connected. For increased noise immunity, connect I.C. to GND.                                                                                                                                                                                                                                                                                        |  |

| 3                   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                          |  |

| 4                   | RESET           | Active-Low Open-Drain or Push-Pull Reset Output. RESET transitions from high to low when $V_{CC}$ drops below the selected reset threshold. RESET remains low for the reset timeout period after $V_{CC}$ exceeds the device reset threshold. Push-pull RESET outputs are referenced to $V_{CC}$ . Opendrain RESET outputs require an external pullup resistor. |  |

| 5                   | V <sub>CC</sub> | Supply Voltage. Input for $V_{CC}$ reset monitor. For noisy systems, bypass $V_{CC}$ with a 0.1 $\mu F$ capacitor to GND.                                                                                                                                                                                                                                       |  |

# MAX6858/MAX6860 Pin Description

# MAX6861/MAX6862/MAX6863 Pin Description

| PI                  | N       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6861/<br>MAX6863 | MAX6862 | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1                   | 1       | СТ    | Reset Timeout Select Input. Connect CT low to select the D1 reset timeout output period (see Tables 1 and 4). Connect CT high (normally $V_{CC}$ ) to select the D3 reset timeout period.                                                                                                                                                                                                                                                                          |

| 2                   | 2       | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3                   | 3       | MR    | Active-Low Manual Reset Input. Drive $\overline{\text{MR}}$ low to initiate a reset. The reset output remains asserted while $\overline{\text{MR}}$ is held low and for the reset timeout period after $\overline{\text{MR}}$ transitions high. Leave $\overline{\text{MR}}$ unconnected or connect to V <sub>CC</sub> if unused. $\overline{\text{MR}}$ is internally pulled up to V <sub>CC</sub> through 10k $\Omega$ .                                         |

| 4                   | _       | RESET | Active-Low Open-Drain or Push-Pull Reset Output. RESET transitions from high to low when V <sub>CC</sub> drops below the selected reset threshold or $\overline{\text{MR}}$ is pulled low. RESET remains low for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold and $\overline{\text{MR}}$ deasserts. Push-pull RESET outputs are referenced to V <sub>CC</sub> . Open-drain RESET outputs require an external pullup resistor. |

| 5                   | 5       | Vcc   | Supply Voltage. Input for $V_{CC}$ reset monitor. For noisy systems, bypass $V_{CC}$ with a 0.1 $\mu F$ capacitor to GND.                                                                                                                                                                                                                                                                                                                                          |

| _                   | 4       | RESET | Active-High Push-Pull Reset Output. RESET transitions from low to high when V <sub>CC</sub> drops below the selected reset threshold or $\overline{\text{MR}}$ is pulled low. RESET remains high for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold and $\overline{\text{MR}}$ deasserts. RESET is referenced to V <sub>CC</sub> .                                                                                              |

| PI                  | N       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6864/<br>MAX6866 | MAX6865 | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1                   | _       | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Active-Low Open-Drain or Push-Pull Reset Output. RESET transitions from high to low when V <sub>CC</sub> drops below the selected reset threshold, $\overline{\text{MR}}$ is pulled low, or the watchdog timer expires. RESET remains low for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold, $\overline{\text{MR}}$ deasserts, or after the watchog timer expires. Push-pull RESET outputs are referenced to V <sub>CC</sub> . Open-drain RESET outputs require an external pullup resistor. |

| 2                   | 2       | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3                   | 3       | $\overline{\text{MR}} \qquad \qquad \text{Active-Low Manual Reset Input. Drive } \overline{\text{MR}} \text{ low to initiate a reset. The reset or remains asserted while } \overline{\text{MR}} \text{ is held low and for the reset timeout period after transitions high. Leave } \overline{\text{MR}} \text{ unconnected or connect to } V_{CC} \text{ if unused. } \overline{\text{MR}} \text{ is internally pulled up to } V_{CC} \text{ through } 10\text{k}\Omega.$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4                   | 4       | WDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Watchdog Input. If WDI remains high or low for longer than the watchdog timeout period, the internal watchdog timer expires, and a reset is triggered for the reset timeout period. The internal watchdog timer clears whenever reset is asserted, the manual reset is asserted, or WDI sees a rising or falling edge.                                                                                                                                                                                                           |

| 5                   | 5       | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Supply Voltage. Input for $V_{CC}$ reset monitor. For noisy systems, bypass $V_{CC}$ with a 0.1 $\mu F$ capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                        |

| _                   | 1       | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Active-High Push-Pull Reset Output. RESET transitions from low to high when V <sub>CC</sub> drops below the selected reset threshold, $\overline{\text{MR}}$ is pulled low, or the watchdog timer expires. RESET remains high for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold, $\overline{\text{MR}}$ deasserts, or after the watchdog timer expires. RESET is referenced to V <sub>CC</sub> .                                                                                             |

### MAX6864/MAX6865/MAX6866 Pin Description

# MAX6867/MAX6868/MAX6869 Pin Description

| PI                  | N       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6867/<br>MAX6869 | MAX6868 | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                   | 1       | WDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Watchdog Input. If WDI remains high or low for longer than the watchdog timeout period, the internal watchdog timer expires, and a reset is triggered for the reset timeout period. The internal watchdog timer clears whenever reset is asserted, the manual reset is asserted, or WDI sees a rising or falling edge.                                                                                                                                                                                                            |

| 2                   | 2       | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                   | 3       | $\overline{\text{MR}} \qquad \qquad \text{Active-Low Manual Reset Input. Drive } \overline{\text{MR}} \text{ low to initiate a reset. The reservation remains asserted while } \overline{\text{MR}} \text{ is held low and for the reset timeout period a transitions high. Leave } \overline{\text{MR}} \text{ unconnected or connect to } V_{\text{CC}} \text{ if unused. } \overline{\text{MR}} \text{ internally pulled up to } V_{\text{CC}} \text{ through } 10\text{k}\Omega. \\ \end{aligned}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4                   | _       | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Active-Low Open-Drain or Push-Pull Reset Output. RESET transitions from high to low when V <sub>CC</sub> drops below the selected reset threshold, $\overline{\text{MR}}$ is pulled low, or the watchdog timer expires. RESET remains low for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold, $\overline{\text{MR}}$ deasserts, or after the watchdog timer expires. Push-pull RESET outputs are referenced to V <sub>CC</sub> . Open-drain RESET outputs require an external pullup resistor. |

| 5                   | 5       | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supply Voltage. Input for $V_{CC}$ reset monitor. For noisy systems, bypass $V_{CC}$ with a 0.1 $\mu F$ capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                         |

| _                   | 4       | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Active-High Push-Pull Reset Output. RESET transitions from low to high when V <sub>CC</sub> drops below the selected reset threshold, $\overline{\text{MR}}$ is pulled low, or the watchdog timer expires. RESET remains high for the reset timeout period after V <sub>CC</sub> exceeds the device reset threshold, $\overline{\text{MR}}$ deasserts, or after the watchdog timer expires. RESET is referenced to V <sub>CC</sub> .                                                                                              |

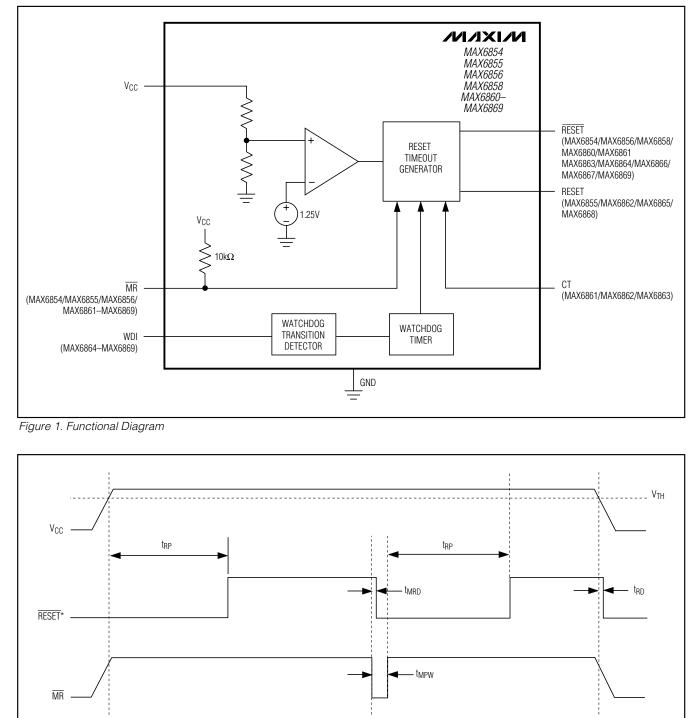

Figure 2. RESET Timing Relationship

\*RESET IS THE INVERSE OF RESET.

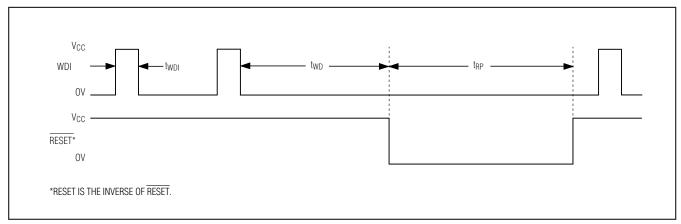

Figure 3. Detailed Watchdog Input Timing Relationship

### **Detailed Description**

#### **RESET**/RESET Output

A  $\mu$ P's reset input starts the  $\mu$ P in a known state. The MAX6854/MAX6855/MAX6856/MAX6858/MAX6860–MAX6869  $\mu$ P supervisory circuits assert a reset to prevent code-execution errors during power-up, power-down, and brownout conditions. The MAX6854/MAX6855/MAX6856/MAX6858/MAX6860–MAX6869 reset output is guaranteed to be valid for V<sub>CC</sub> down to 1.1V.

Whenever V<sub>CC</sub> falls below the reset threshold, the reset output asserts low for RESET and high for RESET. Once V<sub>CC</sub> exceeds the reset threshold, an internal timer keeps the reset output asserted for the specified reset timeout period, then after this interval the reset output deasserts (see Figure 2).

#### **Manual Reset Input**

Many µP-based products require manual reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. The MAX6854/ MAX6855/MAX6856/MAX6861-MAX6869 feature an MR input. A logic low on MR asserts a reset. Reset remains asserted while MR is low and for the timeout period, t<sub>RP</sub>, after MR returns high. The devices provide an internal 10k $\Omega$  pullup from  $\overline{\mathsf{MR}}$  to V<sub>CC</sub>. Leave  $\overline{\mathsf{MR}}$ unconnected or connect to V<sub>CC</sub> if unused. MR can be driven with CMOS logic levels or with open-drain/collector outputs. Connect a normally open momentary switch from MR to GND to implement a manual reset function; external debounce circuitry is not required. If MR is driven by long cables or the device is used in a noisy environment, connect a 0.1 $\mu$ F capacitor from MR to GND to provide additional noise immunity.

#### Watchdog Input

The MAX6864–MAX6869's watchdog timer circuitry monitors the  $\mu$ P's activity. If the  $\mu$ P does not toggle (low-to-high or high-to-low) the watchdog input (WDI) within the watchdog timeout period (t<sub>WDI</sub>), reset asserts for the reset timeout period (t<sub>RP</sub>). The internal timer is cleared when reset asserts, when manual reset is asserted, or by a rising or falling edge on WDI. The watchdog input detects pulses as short as 150ns. While reset is asserted the watchdog timer does not count. As soon as reset deasserts, the watchdog timer resumes counting (Figure 3).

### \_Applications Information

# Selecting the Reset Timeout Period

The reset timeout period for the MAX6854/MAX6855/ MAX6856/MAX6858/MAX6860/MAX6864–MAX6869 is fixed (see Table 4). The MAX6861/MAX6862/MAX6863 feature a reset timeout select input, CT. Connect CT according to Table 1 to select between the available 10ms and 150ms (min) reset timeout periods. The timeout period can be changed while a reset timeout period is in progress, but will not update until the reset timeout period has expired.

# Table 1. MAX6861/MAX6862/MAX6863Reset Timeout Period Selection

| CT CONNECTION | MIN | ТҮР | МАХ | UNITS |  |

|---------------|-----|-----|-----|-------|--|

| LOW           | 10  | 15  | 25  | 100.0 |  |

| HIGH          | 150 | 225 | 300 | ms    |  |

#### **Transient Immunity**

In addition to issuing a reset to the  $\mu$ P during power-up, power-down, and brownout conditions, the MAX6854/MAX6855/MAX6856/MAX6858/MAX6860–MAX6869 are relatively immune to short-duration supply transients, or glitches. The Maximum V<sub>CC</sub> Transient Duration vs. Reset Threshold Overdrive graph in the *Typical Operating Characteristics* shows this relationship.

The area below the curve of the graph is the region in which these devices typically do not generate a reset pulse. This graph was generated using a falling pulse applied to V<sub>CC</sub>, starting 100mV above the actual reset threshold, V<sub>TH</sub>, and ending below this threshold (reset-threshold overdrive). As the magnitude of the transient increases, the maximum allowable pulse width decreases. Typically, a 100mV V<sub>CC</sub> transient duration of 40µs or less does not cause a reset.

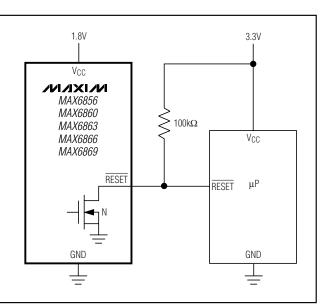

#### Interfacing to Other Voltages for Logic Compatibility

The open-drain RESET output can be used to interface to a  $\mu$ P with other logic levels. As shown in Figure 4, the open-drain output can be connected to voltages from 0 to 5.5V.

Generally, the pullup resistor connected to  $\overrightarrow{\text{RESET}}$  connects to the supply voltage that is being monitored at the IC's V<sub>CC</sub> input. However, some systems use the

open-drain output to level-shift from the monitored supply to reset circuitry powered by another supply voltage. Keep in mind that as the supervisor's  $V_{CC}$  decreases, so does the IC's ability to sink current at RESET.

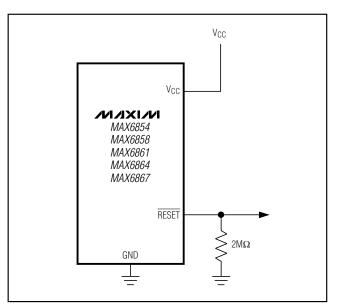

#### Ensuring a Valid **RESET** Down to V<sub>CC</sub> = 0V (Push-Pull RESET)

When V<sub>CC</sub> falls below 1.1V, RESET's current-sinking capability declines drastically. The high-impedance CMOS logic inputs connected to RESET can drift to undetermined voltages. This presents no problems in most applications, since most  $\mu$ Ps and other circuitry do not operate with V<sub>CC</sub> below 1.1V.

In those applications where RESET must be valid down to 0, add a pulldown resistor between RESET and GND for the MAX6854/MAX6858/MAX6861/MAX6864/ MAX6867 push-pull outputs. The resistor sinks any stray leakage currents, holding RESET low (Figure 5). Choose a pulldown resistor that accommodates leakages, such that RESET is not significantly loaded and is capable of pulling to GND. The external pulldown cannot be used with the open-drain reset outputs.

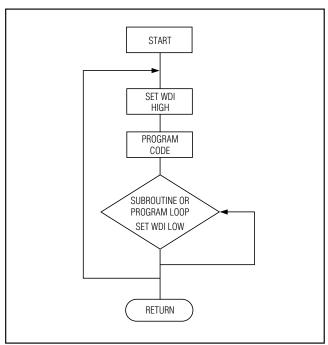

#### Watchdog Software Considerations

One way to help the watchdog timer monitor software execution more closely is to set and reset the watchdog

Figure 4. Interfacing with Other Voltage Levels

Figure 5. Ensuring RESET Valid to VCC = Ground

input at different points in the program, rather than pulsing the watchdog input high-low-high or low-highlow. This technique avoids a stuck loop, in which the watchdog timer would continue to be reset inside the loop, keeping the watchdog from timing out.

Figure 6 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the beginning of every subroutine or loop, then set high again when the program returns to the beginning. If the program should hang in any subroutine, the problem would quickly be corrected, since the I/O is continually set low and the watchdog timer is allowed to time out, causing a reset or interrupt to be issued.

Figure 6. Watchdog Flow Diagram

### Table 2. Threshold Suffix Guide

|        |                    |           | Garao  |       |

|--------|--------------------|-----------|--------|-------|

| SUFFIX | V <sub>CC</sub> TH | RESHOLD F | ALLING |       |

| SUFFIX | MIN                | TYP M     | MAX    | UNITS |

| 46     | 4.509              | 4.625     | 4.741  |       |

| 45     | 4.388              | 4.500     | 4.613  |       |

| 44     | 4.266              | 4.375     | 4.484  |       |

| 43     | 4.193              | 4.300     | 4.408  |       |

| 42     | 4.095              | 4.200     | 4.305  |       |

| 41     | 3.998              | 4.100     | 4.203  |       |

| 40     | 3.900              | 4.000     | 4.100  |       |

| 39     | 3.802              | 3.900     | 3.998  |       |

| 38     | 3.705              | 3.800     | 3.895  |       |

| 37     | 3.608              | 3.700     | 3.793  |       |

| 36     | 3.510              | 3.600     | 3.690  |       |

| 35     | 3.413              | 3.500     | 3.588  |       |

| 34     | 3.315              | 3.400     | 3.485  |       |

| 33     | 3.218              | 3.300     | 3.383  |       |

| 32     | 3.120              | 3.200     | 3.280  |       |

| 31     | 2.998              | 3.075     | 3.152  |       |

| 30     | 2.925              | 3.000     | 3.075  | V     |

| 29     | 2.852              | 2.925     | 2.998  |       |

| 28     | 2.730              | 2.800     | 2.870  |       |

| 27     | 2.633              | 2.700     | 2.768  |       |

| 26     | 2.559              | 2.625     | 2.691  |       |

| 25     | 2.438              | 2.500     | 2.563  |       |

| 24     | 2.340              | 2.400     | 2.460  |       |

| 23     | 2.255              | 2.313     | 2.371  |       |

| 225    | 2.180              | 2.235     | 2.290  |       |

| 22     | 2.133              | 2.188     | 2.243  |       |

| 21     | 2.048              | 2.100     | 2.153  |       |

| 20     | 1.950              | 2.000     | 2.050  |       |

| 19     | 1.853              | 1.900     | 1.948  |       |

| 18     | 1.755              | 1.800     | 1.845  |       |

| 17     | 1.623              | 1.665     | 1.707  |       |

| 16     | 1.536              | 1.575     | 1.614  |       |

# Table 3. Watchdog Timeout

| SUFFIX | WATCHDOG TIMEOUT PERIOD |     |      |       |  |

|--------|-------------------------|-----|------|-------|--|

| SUFFIX | MIN                     | TYP | MAX  | UNITS |  |

| S      | 1.5                     | 3.3 | 7.75 |       |  |

| L      | 95                      | 209 | 487  | S     |  |

| TIMEOUT | RESET TIMEOUT PERIODS |      |      |       |  |

|---------|-----------------------|------|------|-------|--|

| OPTION  | MIN                   | TYP  | MAX  | UNITS |  |

| D1      | 10                    | 15   | 25   |       |  |

| D2      | 40                    | 60   | 80   |       |  |

| D3      | 150                   | 225  | 300  |       |  |

| D4      | 1200                  | 1800 | 2400 | ms    |  |

| D5      | 300                   | 450  | 600  |       |  |

| D6      | 600                   | 900  | 1200 |       |  |

### Table 4. Reset Timeout Periods

### **Table 5. Standard Versions**

| PART           | TOP MARK |  |

|----------------|----------|--|

| MAX6854UK16D3  | AEFS     |  |

| MAX6854UK23D3  | AEFY     |  |

| MAX6854UK26D3  | AEFZ     |  |

| MAX6854UK29D3  | AEGA     |  |

| MAX6854UK31D3  | AEGB     |  |

| MAX6856UK16D3  | AEGR     |  |

| MAX6856UK23D3  | AEGS     |  |

| MAX6856UK26D3  | AEGT     |  |

| MAX6856UK29D3  | AEGU     |  |

| MAX6856UK31D3  | AEGV     |  |

| MAX6861UK17    | AEKO     |  |

| MAX6861UK225   | AEKS     |  |

| MAX6861UK26    | AEKP     |  |

| MAX6861UK29    | AEKQ     |  |

| MAX6862UK17    | AEOS     |  |

| MAX6862UK225   | AEOT     |  |

| MAX6862UK26    | AEOU     |  |

| MAX6862UK29    | AEOV     |  |

| MAX6863UK17    | AEOW     |  |

| MAX6863UK225   | AEOX     |  |

| MAX6863UK26    | AEOY     |  |

| MAX6863UK29    | AEOZ     |  |

| MAX6864UK16D3S | AEGC     |  |

| MAX6864UK23D3S | AEGD     |  |

| MAX6864UK26D3S | AEGE     |  |

| MAX6864UK29D3S | AEGF     |  |

| MAX6864UK31D3S | AEGG     |  |

| MAX6866UK16D3S | AEGW     |  |

| MAX6866UK23D3S | AEGX     |  |

| MAX6866UK26D3S | AEGY     |  |

| MAX6866UK29D3S | AEFT     |  |

| MAX6866UK31D3S | AEGZ     |  |

### **Ordering Information (continued)**

| PART <sup>†</sup> | TEMP RANGE     | PIN-PACKAGE |

|-------------------|----------------|-------------|

| MAX6856UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6858UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6860UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6861UKT        | -40°C to +85°C | 5 SOT23-5   |

| MAX6862UKT        | -40°C to +85°C | 5 SOT23-5   |

| MAX6863UKT        | -40°C to +85°C | 5 SOT23-5   |

| MAX6864UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6865UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6866UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6867UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6868UKDT       | -40°C to +85°C | 5 SOT23-5   |

| MAX6869UKDT       | -40°C to +85°C | 5 SOT23-5   |

† Insert reset threshold suffix (see Table 2, Threshold Suffix Guide) after UK. Insert the number corresponding to the desired reset timeout period (see Table 4, Reset Timeout Period) after D. Insert the letter corresponding to the desired watchdog timeout period (S or L, see Table 3) into the blank following the reset timeout period suffix for the MAX6864–MAX6869.

**Note:** Sample stock is generally held on standard versions only (see Table 5, Standard Versions Table). Standard versions have an order increment of 2500 pieces. Nonstandard versions have an order increment of 10,000 pieces. Contact factory for availability of nonstandard versions.

Devices are available in both leaded and lead-free packaging. Specify lead-free by replacing "-T" with "+T" when ordering.

Pin Configurations

### **Selector Guide**

|         |                         | RESET OUTPL              | JT                       |              |              |    |

|---------|-------------------------|--------------------------|--------------------------|--------------|--------------|----|

| PART    | PUSH-PULL<br>ACTIVE LOW | PUSH-PULL<br>ACTIVE HIGH | OPEN-DRAIN ACTIVE<br>LOW | MR           | WDI          | СТ |

| MAX6854 |                         | _                        | _                        | $\checkmark$ |              |    |

| MAX6855 | —                       | $\checkmark$             | —                        | $\checkmark$ | —            | _  |

| MAX6856 | —                       | —                        |                          | $\checkmark$ | —            | _  |

| MAX6858 |                         | _                        | _                        | _            | _            | _  |

| MAX6860 | —                       | _                        |                          | —            | _            | _  |

| MAX6861 |                         | _                        | _                        | $\checkmark$ | _            |    |

| MAX6862 | —                       |                          | —                        | $\checkmark$ | —            |    |

| MAX6863 | —                       | —                        | $\checkmark$             | $\checkmark$ | —            |    |

| MAX6864 |                         | _                        | _                        | $\checkmark$ | $\checkmark$ |    |

| MAX6865 | _                       |                          | _                        | $\checkmark$ | $\checkmark$ | _  |

| MAX6866 | —                       | —                        |                          | $\checkmark$ | $\checkmark$ | _  |

| MAX6867 |                         | —                        | _                        | $\checkmark$ | $\checkmark$ | _  |

| MAX6868 | —                       |                          | _                        | $\checkmark$ | $\checkmark$ | _  |

| MAX6869 | _                       |                          | $\checkmark$             | $\checkmark$ | $\checkmark$ | _  |

**Chip Information**

TRANSISTOR COUNT: 2848 PROCESS: BICMOS

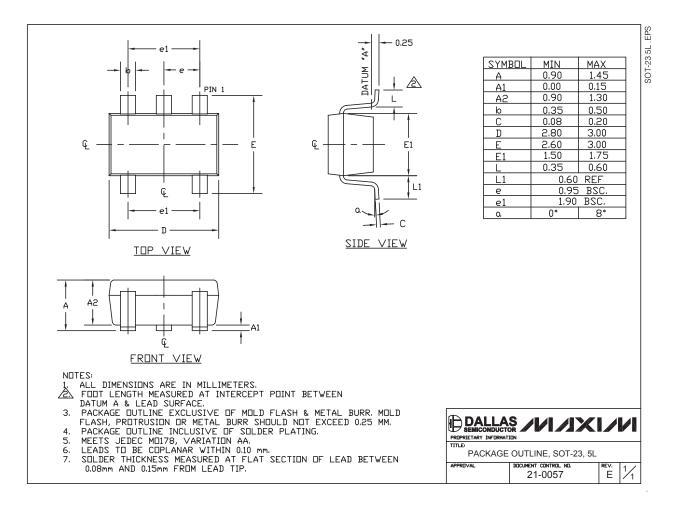

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

MAX6854/MAX6855/MAX6856/MAX6858/MAX6860-MAX6869

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2005 Maxim Integrated Products

Printed USA *MAXIM* is a registered trademark of Maxim Integrated Products, Inc.

# **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <section-header></section-header>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Marchine     Marchine       Marchine     M | Market M<br>Market Market Mark | Marchine     Marchine     Image: Control of the sector of the sec |  |

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.