## 74HCT646D,653 Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number 74HCT646D,653-DG

Manufacturer NXP USA Inc.

Manufacturer Product Number 74HCT646D,653

Description IC TXRX NON-INVERT 5.5V 24SO

Detailed Description Transceiver, Non-Inverting 1 Element 8 Bit per Elem

ent 3-State Output 24-SO

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

## **Purchase and inquiry**

| Manufacturer Product Number: | Manufacturer:                  |

|------------------------------|--------------------------------|

| 74HCT646D,653                | NXP USA Inc.                   |

| Series:                      | Product Status:                |

| 74HCT                        | Obsolete                       |

| Logic Type:                  | Number of Elements:            |

| Transceiver, Non-Inverting   | 1                              |

| Number of Bits per Element:  | Input Type:                    |

| 8                            |                                |

| Output Type:                 | Current - Output High, Low:    |

| 3-State                      | 6mA, 6mA                       |

| Voltage - Supply:            | Operating Temperature:         |

| 4.5V ~ 5.5V                  | -40°C ~ 125°C (TA)             |

| Mounting Type:               | Package / Case:                |

| Surface Mount                | 24-SOIC (0.295", 7.50mm Width) |

| Supplier Device Package:     | Base Product Number:           |

| 24-50                        | 74HCT646                       |

## **Environmental & Export classification**

8542.39.0001

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <a href="http://www.nxp.com">http://www.nxp.com</a>, <a href="http://www.semiconductors.philips.com/">http://www.nxp.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>)

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use salesaddresses@nexperia.com (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

## INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

- The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

- The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

# **74HC/HCT646**Octal bus transceiver/register; 3-state

Product specification

File under Integrated Circuits, IC06

September 1993

#### Octal bus transceiver/register; 3-state

#### **74HC/HCT646**

#### **FEATURES**

- Independent register for A and B buses

- Multiplexed real-time and stored data

- · Output capability: bus driver

- I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

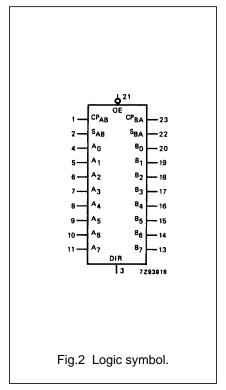

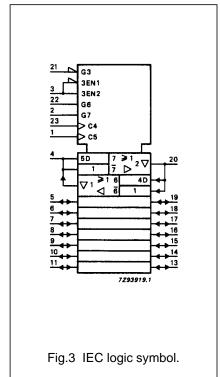

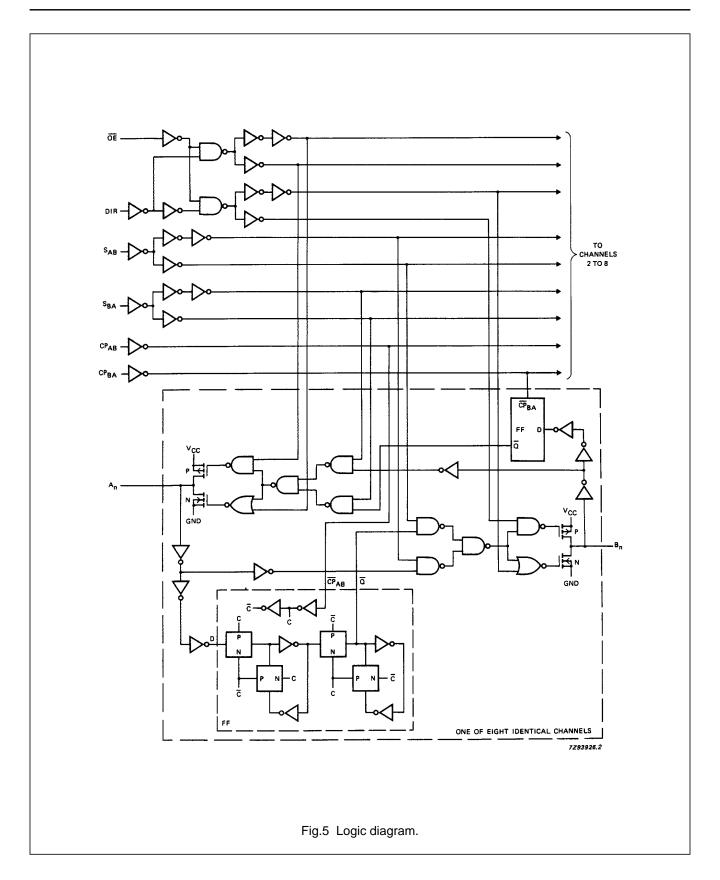

The 74HC/HCT646 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

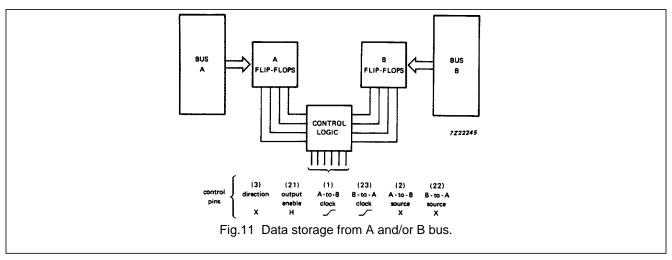

The 74HC/HCT646 consist of bus transceiver circuits with 3-state outputs, D-type flip-flops, and control circuitry arranged for multiplexed transmission of data directly from the internal registers. Data on the "A" or "B" bus will be

clocked into the registers as the appropriate clock ( $CP_{AB}$  and  $CP_{BA}$ ) goes to a HIGH logic level. Output enable ( $\overline{OE}$ ) and direction (DIR) inputs are provided to control the transceiver function. In the transceiver mode, data present at the high-impedance port may be stored in either the "A" or "B" register, or in both. The select source inputs ( $S_{AB}$  and  $S_{BA}$ ) can multiplex stored and real-time (transparent mode) data. The direction (DIR) input determines which bus will receive data when  $\overline{OE}$  is active (LOW). In the isolation mode ( $\overline{OE}$  = HIGH), "A" data may be stored in the "B" register and/or "B" data may be stored in the "A" register.

When an output function is disabled, the input function is still enabled and may be used to store and transmit data. Only one of the two buses, A or B, may be driven at a time.

The "646" is functionally identical to the "648", but has non-inverting data paths.

#### **QUICK REFERENCE DATA**

$GND = 0 V; T_{amb} = 25 °C; t_r = t_f = 6 ns$

| SYMBOL                              | PARAMETER                                                                            | CONDITIONS                                    | TYF | UNIT  |     |

|-------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|-----|-------|-----|

| STIVIBUL                            | PARAMETER                                                                            | CONDITIONS                                    | НС  | CIVIT |     |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay A <sub>n</sub> , B <sub>n</sub> to B <sub>n</sub> , A <sub>n</sub> | C <sub>L</sub> = 15 pF; V <sub>CC</sub> = 5 V | 11  | 13    | ns  |

| f <sub>max</sub>                    | maximum clock frequency                                                              |                                               | 69  | 85    | MHz |

| C <sub>I</sub>                      | input capacitance                                                                    |                                               | 3.5 | 3.5   | pF  |

| C <sub>PD</sub>                     | power dissipation capacitance per channel                                            | notes 1 and 2                                 | 30  | 33    | pF  |

#### **Notes**

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$P_D = C_{PD} \times V_{CC}^2 \times f_i + \sum (C_L \times V_{CC}^2 \times f_o)$  where:

f<sub>i</sub> = input frequency in MHz

f<sub>o</sub> = output frequency in MHz

$\sum (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs}$

C<sub>L</sub> = output load capacitance in pF

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I = GND$  to  $V_{CC}$ For HCT the condition is  $V_I = GND$  to  $V_{CC} - 1.5$  V

#### **ORDERING INFORMATION**

See "74HC/HCT/HCU/HCMOS Logic Package Information".

## Octal bus transceiver/register; 3-state

## 74HC/HCT646

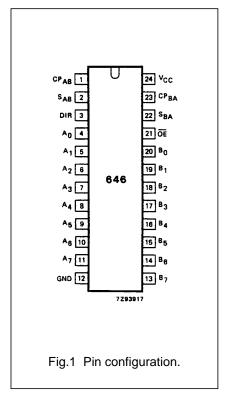

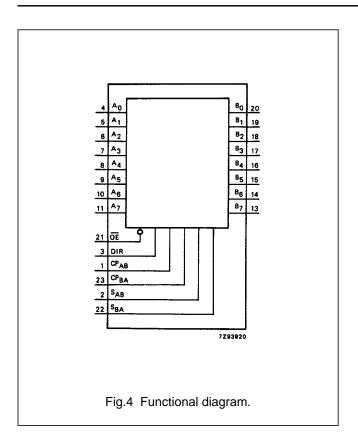

#### **PIN DESCRIPTION**

| PIN NO.                        | SYMBOL                           | NAME AND FUNCTION                                |

|--------------------------------|----------------------------------|--------------------------------------------------|

| 1                              | CP <sub>AB</sub>                 | A to B clock input (LOW-to-HIGH, edge-triggered) |

| 2                              | S <sub>AB</sub>                  | select A to B source input                       |

| 3                              | DIR                              | direction control input                          |

| 4, 5, 6, 7, 8, 9, 10, 11       | A <sub>0</sub> to A <sub>7</sub> | A data inputs/outputs                            |

| 12                             | GND                              | ground (0 V)                                     |

| 20, 19, 18, 17, 16, 15, 14, 13 | B <sub>0</sub> to B <sub>7</sub> | B data inputs/outputs                            |

| 21                             | ŌĒ                               | output enable input (active LOW)                 |

| 22                             | S <sub>BA</sub>                  | select B to A source input                       |

| 23                             | CP <sub>BA</sub>                 | B to A clock input (LOW-to-HIGH, edge-triggered) |

| 24                             | V <sub>CC</sub>                  | positive supply voltage                          |

## Octal bus transceiver/register; 3-state

### 74HC/HCT646

#### **FUNCTION TABLE**

|        |        | INPL             | JTS <sup>(1)</sup> |                 |                 | DATA                             | DATA I/O (2) FUNCTION            |                                                  |  |

|--------|--------|------------------|--------------------|-----------------|-----------------|----------------------------------|----------------------------------|--------------------------------------------------|--|

| ŌĒ     | DIR    | CP <sub>AB</sub> | CPBA               | S <sub>AB</sub> | S <sub>BA</sub> | A <sub>0</sub> to A <sub>7</sub> | B <sub>0</sub> to B <sub>7</sub> | FUNCTION                                         |  |

| H<br>H | X<br>X | H or L<br>↑      | H or L<br>↑        | X<br>X          | X<br>X          | input                            | input                            | isolation<br>store A and B data                  |  |

| L<br>L | L<br>L | X<br>X           | X<br>H or L        | X<br>X          | L<br>H          | output                           | input                            | real-time B data to A bus stored B data to A bus |  |

| L<br>L | H<br>H | X<br>H or L      | X<br>X             | L<br>H          | X<br>X          | input                            | output                           | real-time A data to B bus stored A data to B bus |  |

#### **Notes**

- 1. H = HIGH voltage level

- L = LOW voltage level

- X = don't care

- ↑ = LOW-to-HIGH level transition

- 2. The data output functions may be enabled or disabled by various signals at the  $\overline{\text{OE}}$  and DIR inputs. Data input functions are always enabled, i.e., data at the bus inputs will be stored on every LOW-to-HIGH transition on the clock inputs.

## Octal bus transceiver/register; 3-state

## 74HC/HCT646

## Octal bus transceiver/register; 3-state

74HC/HCT646

#### DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: bus driver

I<sub>CC</sub> category: MSI

#### **AC CHARACTERISTICS FOR 74HC**

$GND = 0 \text{ V; } t_r = t_f = 6 \text{ ns; } C_L = 50 \text{ pF}$

|                                     |                                                                                           |                 | T <sub>amb</sub> (°C) |                 |                     |                 |                 |                 |     | TEST CONDITIONS   |                 |  |

|-------------------------------------|-------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------|---------------------|-----------------|-----------------|-----------------|-----|-------------------|-----------------|--|

| 0)(140.01                           | DADAMETED                                                                                 |                 | 74HC                  |                 |                     |                 |                 |                 |     |                   |                 |  |

| SYMBOL                              | PARAMETER                                                                                 | +25             |                       |                 | -40 to +85   -40 to |                 |                 | to +125         |     | V <sub>CC</sub>   | WAVEFORMS       |  |

|                                     |                                                                                           | min.            | typ.                  | max.            | min.                | max.            | min.            | max.            |     | (*)               |                 |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay A <sub>n</sub> ,B <sub>n</sub> to B <sub>n</sub> ,A <sub>n</sub>        |                 | 39<br>14<br>11        | 135<br>27<br>23 |                     | 170<br>34<br>29 |                 | 205<br>41<br>35 | ns  | 2.0<br>4.5<br>6.0 | Fig.6           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP <sub>AB</sub> ,CP <sub>BA</sub> to B <sub>n</sub> ,A <sub>n</sub> |                 | 66<br>24<br>19        | 220<br>44<br>37 |                     | 275<br>55<br>47 |                 | 330<br>66<br>56 | ns  | 2.0<br>4.5<br>6.0 | Fig.7           |  |

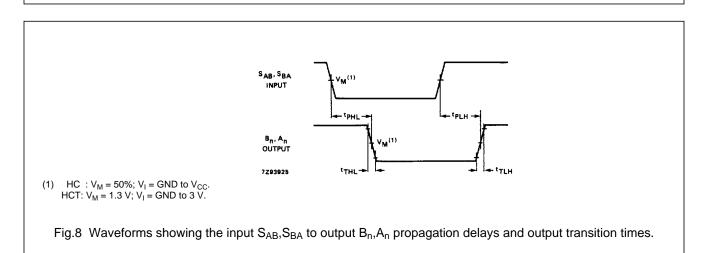

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay S <sub>AB</sub> ,S <sub>BA</sub> to B <sub>n</sub> ,A <sub>n</sub>      |                 | 55<br>20<br>16        | 190<br>38<br>32 |                     | 240<br>48<br>41 |                 | 285<br>57<br>48 | ns  | 2.0<br>4.5<br>6.0 | Fig.8           |  |

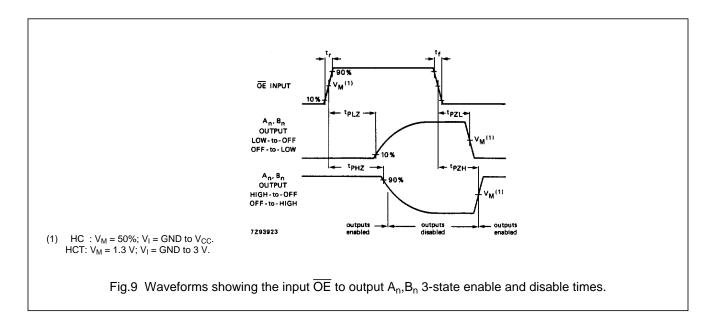

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time OE to A <sub>n</sub> ,B <sub>n</sub>                           |                 | 47<br>17<br>14        | 175<br>35<br>30 |                     | 220<br>44<br>37 |                 | 265<br>53<br>45 | ns  | 2.0<br>4.5<br>6.0 | Fig.9           |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time $\overline{OE}$ to $A_n,B_n$                                  |                 | 58<br>21<br>17        | 175<br>35<br>30 |                     | 220<br>44<br>37 |                 | 265<br>53<br>45 | ns  | 2.0<br>4.5<br>6.0 | Fig.9           |  |

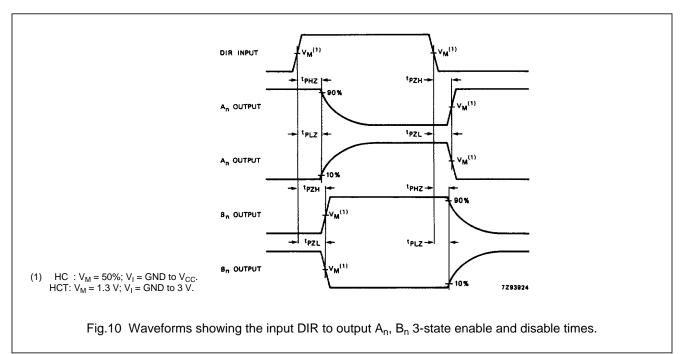

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time DIR to A <sub>n</sub> ,B <sub>n</sub>                          |                 | 50<br>18<br>14        | 175<br>35<br>30 |                     | 220<br>44<br>37 |                 | 265<br>53<br>45 | ns  | 2.0<br>4.5<br>6.0 | Fig.10          |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time DIR to A <sub>n</sub> ,B <sub>n</sub>                         |                 | 50<br>18<br>14        | 175<br>35<br>30 |                     | 220<br>44<br>37 |                 | 265<br>53<br>45 | ns  | 2.0<br>4.5<br>6.0 | Fig.10          |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                                                    |                 | 14<br>5<br>4          | 60<br>12<br>10  |                     | 75<br>15<br>13  |                 | 90<br>18<br>15  | ns  | 2.0<br>4.5<br>6.0 | Fig.6 and Fig.8 |  |

| t <sub>W</sub>                      | clock pulse width<br>HIGH or LOW<br>CP <sub>AB</sub> or CP <sub>BA</sub>                  | 80<br>16<br>14  | 25<br>9<br>7          |                 | 100<br>24<br>20     |                 | 120<br>24<br>20 |                 | ns  | 2.0<br>4.5<br>6.0 | Fig.7           |  |

| t <sub>su</sub>                     | set-up time A <sub>n</sub> ,B <sub>n</sub> to CP <sub>AB</sub> ,CP <sub>BA</sub>          | 60<br>12<br>10  | -3<br>-1<br>-1        |                 | 75<br>15<br>13      |                 | 90<br>18<br>15  |                 | ns  | 2.0<br>4.5<br>6.0 | Fig.7           |  |

| t <sub>h</sub>                      | hold time<br>A <sub>n</sub> ,B <sub>n</sub> to CP <sub>AB</sub> ,CP <sub>BA</sub>         | 35<br>7<br>6    | 6<br>2<br>2           |                 | 45<br>9<br>8        |                 | 55<br>11<br>9   |                 | ns  | 2.0<br>4.5<br>6.0 | Fig.7           |  |

| f <sub>max</sub>                    | maximum clock pulse<br>frequency                                                          | 6.0<br>30<br>35 | 21<br>63<br>75        |                 | 4.8<br>24<br>28     |                 | 4.0<br>20<br>24 |                 | MHz | 2.0<br>4.5<br>6.0 | Fig.7           |  |

## Octal bus transceiver/register; 3-state

74HC/HCT646

#### DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: bus driver

I<sub>CC</sub> category: MSI

#### Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT                             | UNIT LOAD COEFFICIENT |

|-----------------------------------|-----------------------|

| S <sub>AB</sub> , S <sub>BA</sub> | 0.60                  |

| $A_0$ to $A_7$ and $B_0$ to $B_7$ | 0.75                  |

| INPUT                               | UNIT LOAD COEFFICIENT |

|-------------------------------------|-----------------------|

| CP <sub>AB</sub> , CP <sub>BA</sub> | 1.50                  |

| ŌĒ                                  | 1.50                  |

| DIR                                 | 1.25                  |

## Octal bus transceiver/register; 3-state

## 74HC/HCT646

#### **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                                                           |       |      | •    | Γ <sub>amb</sub> (° | C)   |             |      |      | TEST CONDITIONS |                 |  |

|-------------------------------------|-------------------------------------------------------------------------------------------|-------|------|------|---------------------|------|-------------|------|------|-----------------|-----------------|--|

| CAMBOI                              | DADAMETED                                                                                 | 74HCT |      |      |                     |      |             |      |      |                 |                 |  |

| SYMBOL                              | PARAMETER                                                                                 | +25   |      |      | -40 to +85          |      | -40 to +125 |      | UNIT | V <sub>CC</sub> | WAVEFORMS       |  |

|                                     |                                                                                           | min.  | typ. | max. | min.                | max. | min.        | max. |      | (',             |                 |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay A <sub>n</sub> ,B <sub>n</sub> to B <sub>n</sub> ,A <sub>n</sub>        |       | 16   | 30   |                     | 38   |             | 45   | ns   | 4.5             | Fig.6           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>CP <sub>AB</sub> ,CP <sub>BA</sub> to B <sub>n</sub> ,A <sub>n</sub> |       | 23   | 44   |                     | 55   |             | 66   | ns   | 4.5             | Fig.7           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay S <sub>AB</sub> ,S <sub>BA</sub> to B <sub>n</sub> ,A <sub>n</sub>      |       | 26   | 46   |                     | 58   |             | 69   | ns   | 4.5             | Fig.8           |  |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time<br><del>OE</del> to A <sub>n</sub> ,B <sub>n</sub>             |       | 21   | 40   |                     | 50   |             | 60   | ns   | 4.5             | Fig.9           |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time<br>OE to A <sub>n</sub> ,B <sub>n</sub>                       |       | 20   | 35   |                     | 44   |             | 53   | ns   | 4.5             | Fig.9           |  |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time DIR to A <sub>n</sub> ,B <sub>n</sub>                          |       | 21   | 40   |                     | 50   |             | 60   | ns   | 4.5             | Fig.10          |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time DIR to A <sub>n</sub> ,B <sub>n</sub>                         |       | 21   | 35   |                     | 44   |             | 53   | ns   | 4.5             | Fig.10          |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                                                    |       | 5    | 12   |                     | 15   |             | 18   | ns   | 4.5             | Fig.6 and Fig.8 |  |

| t <sub>W</sub>                      | clock pulse width<br>HIGH or LOW<br>CP <sub>AB</sub> or CP <sub>BA</sub>                  | 16    | 8    |      | 20                  |      | 24          |      | ns   | 4.5             | Fig.7           |  |

| t <sub>su</sub>                     | set-up time<br>A <sub>n</sub> ,B <sub>n</sub> to CP <sub>AB</sub> ,CP <sub>BA</sub>       | 12    | 3    |      | 15                  |      | 18          |      | ns   | 4.5             | Fig.7           |  |

| t <sub>h</sub>                      | hold time<br>A <sub>n</sub> ,B <sub>n</sub> to CP <sub>AB</sub> ,CP <sub>BA</sub>         | 5     | 1    |      | 5                   |      | 5           |      | ns   | 4.5             | Fig.7           |  |

| f <sub>max</sub>                    | maximum clock pulse frequency                                                             | 30    | 77   |      | 24                  |      | 20          |      | MHz  | 4.5             | Fig.7           |  |

## Octal bus transceiver/register; 3-state

#### 74HC/HCT646

#### **AC WAVEFORMS**

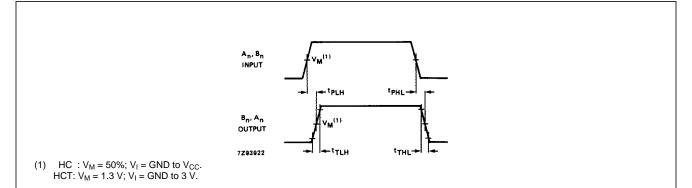

Fig.6 Waveforms showing the input A<sub>n</sub>, B<sub>n</sub> to output B<sub>n</sub>, A<sub>n</sub> propagation delays and the output transition times.

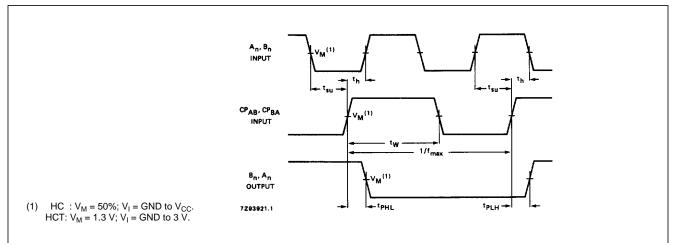

Fig.7 Waveforms showing the  $A_n$ ,  $B_n$  to  $CP_{AB}$ ,  $CP_{BA}$  set-up and hold times, clock  $CP_{AB}$ ,  $CP_{BA}$  pulse width, maximum clock pulse frequency and the  $CP_{AB}$ ,  $CP_{BA}$  to output  $B_n$ ,  $A_n$  propagation delays.

## Octal bus transceiver/register; 3-state

#### 74HC/HCT646

## Octal bus transceiver/register; 3-state

## 74HC/HCT646

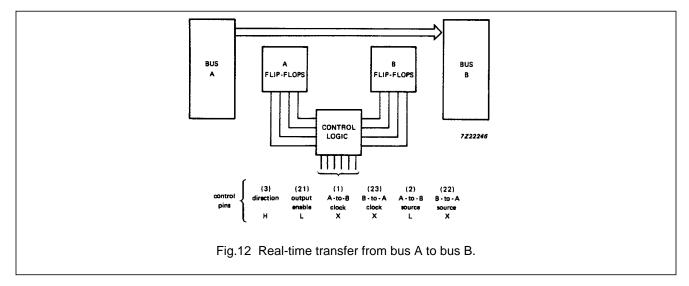

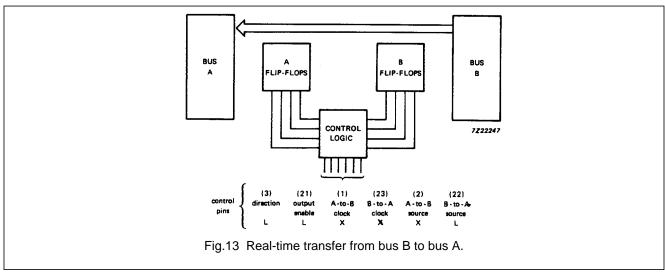

#### **APPLICATION INFORMATION**

## Octal bus transceiver/register; 3-state

74HC/HCT646

#### **PACKAGE OUTLINES**

See "74HC/HCT/HCU/HCMOS Logic Package Outlines".

### **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com