# TDA8024AT/C1,112 Datasheet

DiGi Electronics Part Number Manufacturer Manufacturer Product Number Description Detailed Description TDA8024AT/C1,112-DG NXP USA Inc. TDA8024AT/C1,112 IC SMART CARD INTERFACE 28SOIC Interface

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# Purchase and inquiry

| Manufacturer Product Number: | Manufacturer:   |

|------------------------------|-----------------|

| TDA8024AT/C1,112             | NXP USA Inc.    |

| Series:                      | Product Status: |

| *                            | Obsolete        |

| Base Product Number:         |                 |

| TDA802                       |                 |

|                              |                 |

# **Environmental & Export classification**

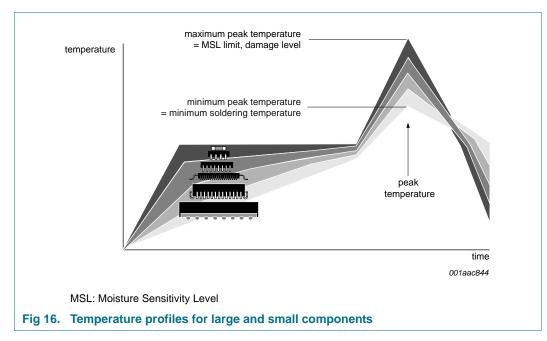

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

**TDA8024** Standard smart card interface Rev. 4.0 — 3 June 2016

**Product data sheet**

# 1. General description

The TDA8024 is a complete and cost-efficient analog interface for asynchronous 3 V or 5 V smart cards. It can be placed between the card and the microcontroller to perform all supply, protection and control functions. Very few external components are required. The TDA8024AT is a direct replacement for the TDA8004AT.

More information can be obtained from the NXP internet site (<u>www.nxp.com</u>) and from *"Application note AN10141"*.

#### CAUTION

This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices.

Such precautions are described in the ANSI/ESD S20.20, IEC/ST 61340-5, JESD625-A or equivalent standards.

# 2. Features and benefits

- IC card interface

- 3 V or 5 V supply for the IC (V<sub>DD</sub> and GND)

- Three specifically protected half-duplex bidirectional buffered I/O lines to card contacts C4, C7 and C8

- DC-to-DC converter for V<sub>CC</sub> generation separately powered from a 5 V  $\pm$  20% supply (V<sub>DDP</sub> and PGND)

- 3 V or 5 V ± 5% regulated card supply voltage (V<sub>CC</sub>) with appropriate decoupling has the following capabilities:

- $I_{CC}$  < 80 mA at  $V_{DDP}$  = 4 V to 6.5 V

- Handles current spikes of 40 nAs up to 20 MHz

- Controls rise and fall times

- Filtered overload detection at approximately 120 mA

- Thermal and short-circuit protection on all card contacts

- Automatic activation and deactivation sequences; initiated by software or by hardware in the event of a short-circuit, card take-off, overheating, V<sub>DD</sub> or V<sub>DDP</sub> drop-out

- Enhanced ESD protection on card side (>6 kV)

- 26 MHz integrated crystal oscillator

- Clock generation for cards up to 20 MHz (divided by 1, 2, 4 or 8 through CLKDIV1 and CLKDIV2 signals) with synchronous frequency changes

- Non-inverted control of RST via pin RSTIN

- ISO 7816, GSM11.11 and EMV (payment systems) compatibility

# **TDA8024**

### Standard smart card interface

- Supply supervisor for spike-killing during power-on and power-off and Power-on reset (threshold fixed internally or externally by a resistor bridge); not for TDA8024AT

- Built-in debounce on card presence contacts

- One multiplexed status signal OFF

# 3. Applications

- IC card readers for banking

- Electronic payment

- Identification

- Pay TV

# 4. Quick reference data

#### Table 1. Quick reference data

| Symbol                       | Parameter                                                 | Conditions                                                                 | Min  | Тур | Max  | Unit |  |

|------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------|------|-----|------|------|--|

| Power supplie                | S                                                         |                                                                            |      |     |      |      |  |

| V <sub>DD</sub>              | supply voltage                                            |                                                                            | 2.7  | -   | 6.5  | V    |  |

| V <sub>DDP</sub>             | DC-to-DC converter                                        | V <sub>CC</sub> = 5 V;  I <sub>CC</sub>   < 80 mA                          | 4.0  | 5.0 | 6.5  | V    |  |

|                              | supply voltage                                            | $V_{CC} = 5 \text{ V};  I_{CC}  < 20 \text{ mA}$                           | 3.0  | -   | 6.5  | V    |  |

| I <sub>DD</sub>              | supply current                                            | V <sub>DD</sub> = 3.3 V; f <sub>XTAL</sub> = 10 MHz                        |      |     |      |      |  |

|                              |                                                           | card inactive                                                              | -    | -   | 1.2  | mA   |  |

|                              |                                                           | card active; $f_{CLK} = f_{XTAL}$ ;<br>$C_L = 30 \text{ pF}$               | -    | -   | 1.5  | mA   |  |

| I <sub>DDP</sub>             | DC-to-DC converter                                        | $V_{DDP} = 5 \text{ V};  f_{XTAL} = 10 \text{ MHz}$                        |      |     |      |      |  |

|                              | supply current                                            | inactive mode                                                              | -    | -   | 0.1  | mA   |  |

|                              |                                                           | active mode; $f_{CLK} = f_{XTAL}$ ;<br>$C_L = 30 \text{ pF};  I_{CC}  = 0$ | -    | -   | 10   | mA   |  |

| Card supply                  |                                                           |                                                                            | 1    |     |      |      |  |

| V <sub>CC</sub>              | card suppy voltage                                        | 5 V card:                                                                  |      |     |      |      |  |

|                              | (including ripple voltage)                                | card active;  I <sub>CC</sub>   < 80 mA DC                                 | 4.75 | 5.0 | 5.25 | V    |  |

|                              |                                                           | card active; current pulses $I_p = 40 \text{ nAs}$                         | 4.65 | 5.0 | 5.25 | V    |  |

|                              |                                                           | 3 V card:                                                                  | 1    |     |      |      |  |

|                              |                                                           | card active;  I <sub>CC</sub>   < 65 mA DC                                 | 2.85 | 3.0 | 3.15 | V    |  |

|                              |                                                           | card active; current pulses $I_p = 40 \text{ nAs}$                         | 2.76 | 3.0 | 3.20 | V    |  |

| V <sub>CC(ripple)(p-p)</sub> | ripple voltage on V <sub>CC</sub><br>(peak-to-peak value) | $f_{ripple} = 20 \text{ kHz to } 200 \text{ MHz}$                          | -    | -   | 350  | mV   |  |

| Icc                          | card supply current                                       | $V_{CC} = 0$ to 5 V                                                        | -    | -   | 80   | mA   |  |

|                              |                                                           | $V_{CC} = 0$ to 3 V                                                        | -    | -   | 65   | mA   |  |

# **TDA8024**

Standard smart card interface

| Symbol           | Parameter               | Conditions                                         | Min | Тур | Max  | Unit     |

|------------------|-------------------------|----------------------------------------------------|-----|-----|------|----------|

| General          |                         |                                                    | ·   |     |      | <b>!</b> |

| t <sub>de</sub>  | deactivation time       |                                                    | 50  | 80  | 100  | μS       |

| P <sub>tot</sub> | total power dissipation | continuous operation;<br>$T_{amb} = -25$ to +85 °C | -   | -   | 0.56 | W        |

| T <sub>amb</sub> | ambient temperature     |                                                    | -25 | -   | +85  | °C       |

#### Table 1. Quick reference data ...continued

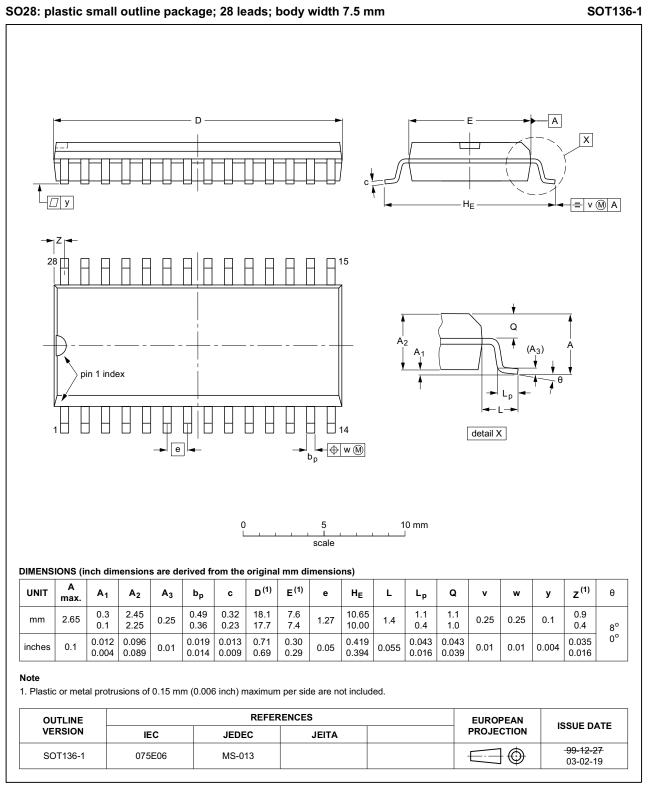

# 5. Ordering information

### Table 2.Ordering information

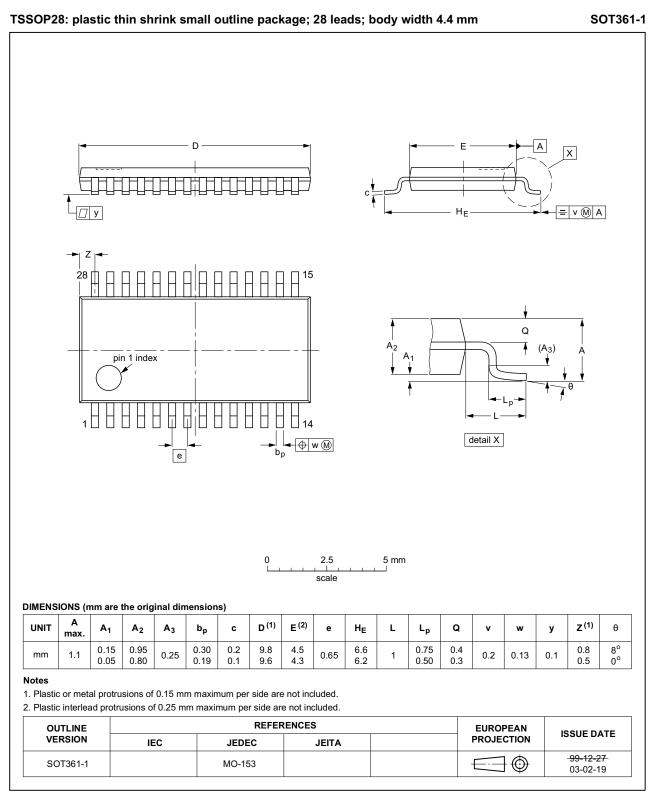

| Type number     | Package |                                                                                     |          |  |  |  |  |

|-----------------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|--|

|                 | Name    | Description                                                                         | Version  |  |  |  |  |

| TDA8024T/C1     | SO28    | plastic small outline package; 28 leads; body width 7.5 mm                          | SOT136-1 |  |  |  |  |

| TDA8024AT/C1    | SO28    | plastic small outline package; 28 leads; body width 7.5 mm                          | SOT136-1 |  |  |  |  |

| TDA8024TT/C1    | TSSOP28 | plastic thin shrink small outline package; 28 leads; body width 4.4 mm, gold wires  | SOT361-1 |  |  |  |  |

| TDA8024TT/C1/S1 | TSSOP28 | plastic thin shrink small outline package; 28 leads; body width 4.4 mm, copper wire | SOT361-1 |  |  |  |  |

# **TDA8024**

Standard smart card interface

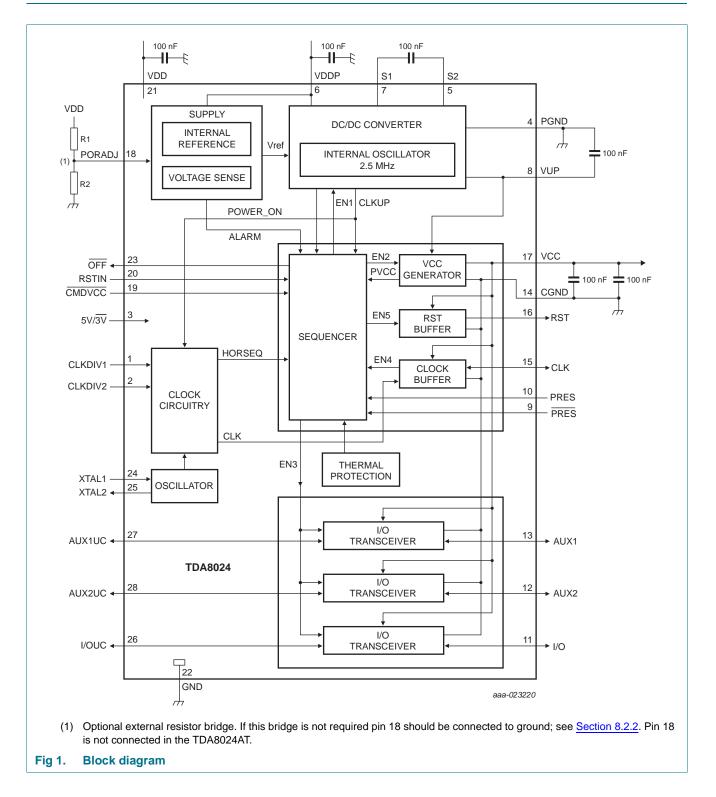

# 6. Block diagram

4 of 33

**TDA8024**

Standard smart card interface

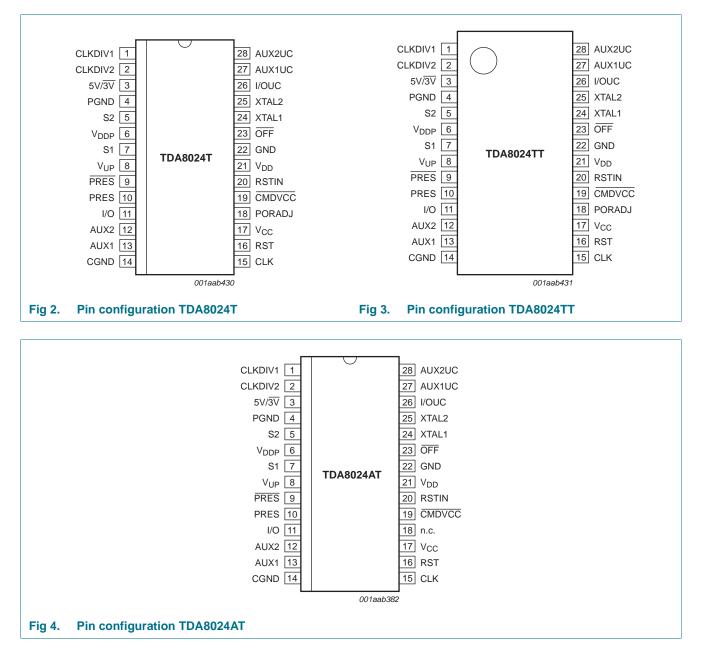

# 7. Pinning information

# 7.1 Pinning

5 of 33

# **TDA8024**

#### Standard smart card interface

# 7.2 Pin description

| Symbol            | Pin | Туре | Description                                                                                                                                                                                            |

|-------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKDIV1           | 1   | 1    | CLK frequency selection input 1                                                                                                                                                                        |

| CLKDIV2           | 2   | I    | CLK frequency selection input 2                                                                                                                                                                        |

| 5V/ <del>3V</del> | 3   | I    | card supply voltage selection input; V <sub>CC</sub> = 5 V (HIGH) or V <sub>CC</sub> = 3 V (LOW)                                                                                                       |

| PGND              | 4   | S    | DC-to-DC converter power supply ground                                                                                                                                                                 |

| S2                | 5   | I/O  | DC-to-DC converter capacitor; connected between pins S1 and S2; C = 100 nF with ESR < 100 m $\Omega$                                                                                                   |

| V <sub>DDP</sub>  | 6   | S    | DC-to-DC converter power supply voltage                                                                                                                                                                |

| S1                | 7   | I/O  | DC-to-DC converter capacitor; connected between pins S1 and S2; C = 100 nF with ESR < 100 m $\Omega$                                                                                                   |

| V <sub>UP</sub>   | 8   | I/O  | DC-to-DC converter output decoupling capacitor connection; C = 100 nF with ESR < 100 m $\Omega$ must be connected between $V_{UP}$ and PGND                                                            |

| PRES              | 9   | I    | card presence contact input (active LOW); if PRES or<br>PRES is active, the card is considered 'present' and a<br>built-in debounce feature of 8 ms (typ.) is activated                                |

| PRES              | 10  | I    | card presence contact input (active HIGH); if PRES or<br>PRES is active, the card is considered 'present' and a<br>built-in debounce feature of 8 ms (typ.) is activated                               |

| I/O               | 11  | I/O  | data line to/from card reader contact C7; integrated 11 $k\Omega$ pull-up resistor to $V_{CC}$                                                                                                         |

| AUX2              | 12  | I/O  | data line to/from card reader contact C8; integrated 11 $k\Omega$ pull-up resistor to $V_{CC}$                                                                                                         |

| AUX1              | 13  | I/O  | data line to/from card reader contact C4; integrated 11 $k\Omega$ pull-up resistor to $V_{CC}$                                                                                                         |

| CGND              | 14  | S    | card signal ground                                                                                                                                                                                     |

| CLK               | 15  | I/O  | card clock to/from card reader contact C3                                                                                                                                                              |

| RST               | 16  | 0    | card reset output from card reader contact C2                                                                                                                                                          |

| V <sub>CC</sub>   | 17  | S    | card supply voltage to card reader contact C1; decoupled to CGND via 2 $\times$ 100 nF or 100 + 220 nF capacitors with ESR < 100 m $\Omega^{[1]}$                                                      |

| PORADJ            | 18  | I    | Power-on reset threshold adjustment input for changing the reset threshold with an external resistor bridge; doubles the width of the POR pulse when used; this pin is not connected for the TDA8024AT |

| CMDVCC            | 19  | I    | input from the host to start activation sequence (active LOW)                                                                                                                                          |

| RSTIN             | 20  | I    | card reset input from the host                                                                                                                                                                         |

| V <sub>DD</sub>   | 21  | S    | supply voltage                                                                                                                                                                                         |

| GND               | 22  | S    | ground                                                                                                                                                                                                 |

| OFF               | 23  | 0    | NMOS interrupt output to the host (active LOW); 20 k $\Omega$ integrated pull-up resistor to V <sub>DD</sub>                                                                                           |

| XTAL1             | 24  | I    | crystal connection or input for external clock                                                                                                                                                         |

TDA8024 Product data sheet

#### Standard smart card interface

TDA8024

| Table 3.         Pin descriptioncontinued |     |      |                                                                                  |  |  |  |  |

|-------------------------------------------|-----|------|----------------------------------------------------------------------------------|--|--|--|--|

| Symbol                                    | Pin | Туре | Description                                                                      |  |  |  |  |

| XTAL2                                     | 25  | 0    | crystal connection (leave open-circuit if external clock source is used)         |  |  |  |  |

| I/OUC                                     | 26  | I/O  | host data I/O line; integrated 11 k $\Omega$ pull-up resistor to $V_{\text{DD}}$ |  |  |  |  |

| AUX1UC                                    | 27  | I/O  | auxiliary data line to/from the host; integrated 11 $k\Omega$ pull-up            |  |  |  |  |

| AUX2UC                                    | 28  | I/O  | resistor to V <sub>DD</sub>                                                      |  |  |  |  |

[1] The noise margin on  $V_{CC}$  will be higher with the 220 nF capacitor.

# 8. Functional description

Throughout this document it is assumed that the reader is familiar with ISO7816 terminology.

## 8.1 **Power supply**

The supply pins for the IC are  $V_{DD}$  and GND.  $V_{DD}$  should be in the range of 2.7 V to 6.5 V. All signals interfacing with the system controller are referred to  $V_{DD}$ , therefore  $V_{DD}$  should also supply the system controller. All card reader contacts remain inactive during power-on or power-off.

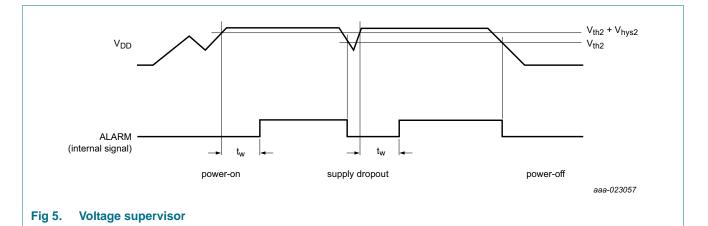

The internal circuits are maintained in the reset state until  $V_{DD}$  reaches  $V_{th2} + V_{hys2}$  and for the duration of the internal Power-on reset pulse,  $t_W$  (see Figure 5). When  $V_{DD}$  falls below  $V_{th2}$ , an automatic deactivation of the contacts is performed.

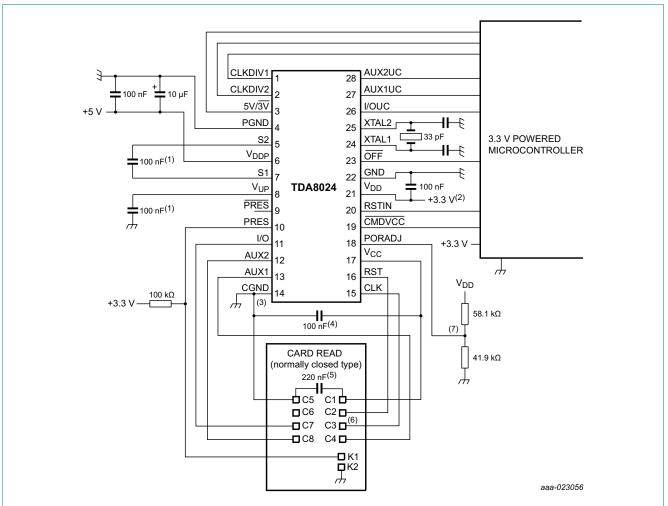

A DC-to-DC converter is incorporated to generate the 5 V or 3 V card supply voltage (V<sub>CC</sub>). The DC-to-DC converter should be supplied separately by V<sub>DDP</sub> and PGND. Due to the possibility of large transient currents, the two 100 nF capacitors of the DC-to-DC converter should be located as near as possible to the IC and have an ESR less than 100 m $\Omega$ .

The DC-to-DC converter functions as a voltage doubler or a voltage follower according to the respective values of  $V_{CC}$  and  $V_{DDP}$  (both have thresholds with a hysteresis of 100 mV).

The DC-to-DC converter function changes as follows.

- V<sub>CC</sub> = 5 V and V<sub>DDP</sub> > 5.8 V; voltage follower

- $V_{CC} = 5$  V and  $V_{DDP} < 5.7$  V; voltage doubler

- V<sub>CC</sub> = 3 V and V<sub>DDP</sub> > 4.1 V; voltage follower

- $V_{CC} = 3 \text{ V}$  and  $V_{DDP} < 4.0 \text{ V}$ ; voltage doubler.

Supply voltages  $V_{DD}$  and  $V_{DDP}$  may be applied to the IC in any sequence.

After powering the device, OFF remains LOW until CMDVCC is set HIGH.

During power off,  $\overline{OFF}$  falls LOW when V<sub>DD</sub> is below the falling threshold voltage.

### 8.2 Voltage supervisor

### 8.2.1 Without external divider on pin PORADJ (or with TDA8024AT)

The voltage supervisor surveys the  $V_{DD}$  supply. A defined reset pulse of approximately 8 ms ( $t_W$ ) is used internally to keep the IC inactive during power-on or power-off of the  $V_{DD}$  supply (see Figure 5).

As long as  $V_{DD}$  is less than  $V_{th2} + V_{hys2}$ , the IC remains inactive whatever the levels on the command lines. This state also lasts for the duration of  $t_W$  after  $V_{DD}$  has reached a level higher than  $V_{th2} + V_{hys2}$ .

When  $V_{DD}$  falls below  $V_{th2}$ , a deactivation sequence of the contacts is performed.

### 8.2.2 With an external divider on pin PORADJ (not for the TDA8024AT)

If an external resistor bridge is connected to pin PORADJ (R1 and R2 in Figure 1), then the following occurs:

• The internal threshold voltage V<sub>th2</sub> is overridden by the external voltage and by the hysteresis, therefore:

$$V_{th2(ext)(rise)} = \left(1 + \frac{RI}{R2}\right) \times \left(V_{bridge} + \frac{V_{hys(ext)}}{2}\right)$$

$$V_{th2(ext)(fall)} = \left(1 + \frac{RI}{R2}\right) \times \left(V_{bridge} - \frac{V_{hys(ext)}}{2}\right)$$

where  $V_{bridge} = 1.25 \text{ V typ.}$  and  $V_{hys(ext)} = 60 \text{ mV typ.}$

The reset pulse width t<sub>W</sub> is doubled to approximately 16 ms.

Input PORADJ is biased internally with a pull-down current source of 4  $\mu$ A which is removed when the voltage on pin PORADJ exceeds 1 V. This ensures that after detection of the external bridge by the IC during power-on, the input current on pin PORADJ does not cause inaccuracy of the bridge voltage.

The minimum threshold voltage should be higher than 2 V.

The maximum threshold voltage may be up to V<sub>DD</sub>.

#### 8.2.3 Applications examples

The voltage supervisor is used as Power-on reset and as supply dropout detection during a card session.

Supply dropout detection is to ensure that a proper deactivation sequence is followed before the voltage is too low.

For the internal voltage supervisor to function, the system microcontroller should operate down to 2.35 V to ensure a proper deactivation sequence. If this is not possible, external resistor values can be chosen to overcome the problem.

#### 8.2.3.1 Microcontroller requiring a 3.3 V $\pm$ 20 % supply

For a microcontroller supplied by 3.3 V with a  $\pm$ 5% regulator and with resistors R1, R2 having a  $\pm$ 1% tolerance, the minimum supply voltage is 3.135 V.

$V_{PORADJ} = k \times V_{DD}$ , where  $k = \frac{S1}{S1 + S2}$  with S1 and S2 the actual values of nominal resistors R1 and R2.

This can be shown as:

$0.99 \times R1 < S1 < 1.01 \times R1$  and  $0.99 \times R2 < S2 < 1.01 \times R2$

Transposed, this becomes

$$1 + \left(0.98 \times \frac{RI}{R2}\right) = 1 + \left(\frac{0.99}{1.01}\right) \times \frac{RI}{R2} < \frac{1}{k}$$

$$\frac{1}{k} < 1 + \left(\frac{1.01}{0.99}\right) \times \frac{R1}{R2} = 1 + \left(1.02 \times \frac{R1}{R2}\right)$$

If V1 =  $V_{th(ext)(rise)(max)}$  and V2 =  $V_{th(ext)(fall)(min)}$  activation will always be possible if  $V_{PORADJ}$  > V1 and deactivation will always be done for  $V_{PORADJ}$  < V2.

Activation is always possible for  $V_{DD} > \frac{VI}{k}$  and deactivation is always possible for  $V_{DD} < \frac{V2}{k}$

That is V1 = 1.31 V and V2 = 1.19 V and

$$\frac{R1}{R2} < \left(\frac{3.135}{1.31} - 1\right) \times 0.98 = 1.365$$

Suppose R1 + R2 = 100 k

$$\Omega$$

, then  $R2 = \frac{100 k\Omega}{2.365} = 42.3 k\Omega$  and R1 = 57.7 k $\Omega$ .

Deactivation will be effective at V2  $\times$  (1 + 1.02  $\times$  1.365) = 2.847 V in any case.

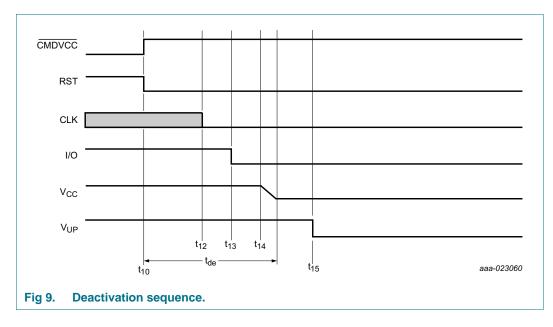

If the microcontroller continues to function down to 2.80 V, the slew rate on  $V_{DD}$  should be less than 2 V/ms to ensure that clock CLK is correctly delivered to the card until time  $t_{12}$  (see Figure 9).

#### 8.2.3.2 Microcontroller requiring a 3.3 V $\pm$ 10% supply

For a microcontroller supplied by a 3.3 V with a  $\pm$ 1% regulator and with resistors R1, R2 having a  $\pm$ 0.1% tolerance, the minimum supply voltage is 3.267 V.

The same calculations as in <u>Section 8.2.3.1</u> conclude:

TDA8024

© NXP Semiconductors N.V. 2016. All rights reserved.

# **TDA8024**

Standard smart card interface

$$\frac{R1}{R2} < \left(\frac{3.267}{1.310} - 1\right) \times 0.998 = 1.491$$

Therefor  $R2 = \frac{100 \, k\Omega}{2.49} = 40.14 \, k\Omega$  and R1 = 59.86 kΩ.

Deactivation will be effective at  $V2 \times (1 + 1.002 \times 1.491) = 2.967$  V in any case.

If the microcontroller continues to function down to 2.97 V, the slew rate on  $V_{DD}$  should be less than 0.20 V/ms to ensure that clock CLK is correctly delivered to the card until time  $t_{12}$  (see Figure 9).

# 8.3 Clock circuitry

The card clock signal (CLK) is derived from a clock signal input to pin XTAL1 or from a crystal operating at up to 26 MHz connected between pins XTAL1 and XTAL2.

The clock frequency can be  $f_{XTAL}$ ,  $\frac{1}{2} \times f_{XTAL}$ ,  $\frac{1}{4} \times f_{XTAL}$  or  $\frac{1}{8} \times f_{XTAL}$ . Frequency selection is made via inputs CLKDIV1 and CLKDIV2 (see <u>Table 4</u>).

| CLKDIV1 | CLKDIV2 | fclk                 |

|---------|---------|----------------------|

| 0       | 0       | $\frac{f_{XTAL}}{8}$ |

| 0       | 1       | $\frac{f_{XTAL}}{4}$ |

| 1       | 1       | $\frac{f_{XTAL}}{2}$ |

| 1       | 0       | f <sub>XTAL</sub>    |

Table 4.

Clock frequency selection<sup>[1]</sup>

[1] The status of pins CLKDIV1 and CLKDIV2 must not be changed simultaneously; a delay of 10 ns minimum between changes is needed; the minimum duration of any state of CLK is eight periods of XTAL1.

The frequency change is synchronous, which means that during transition no pulse is shorter than 45% of the smallest period, and that the first and last clock pulses about the instant of change have the correct width.

When changing the frequency dynamically, the change is effective for only eight periods of XTAL1 after the command.

The duty factor of f<sub>XTAL</sub> depends on the signal present at pin XTAL1.

In order to reach a 45% to 55% duty factor on pin CLK, the input signal on pin XTAL1 should have a duty factor of 48% to 52% and transition times of less than 5% of the input signal period.

If a crystal is used, the duty factor on pin CLK may be 45% to 55% depending on the circuit layout and on the crystal characteristics and frequency.

In other cases, the duty factor on pin CLK is guaranteed between 45% and 55% of the clock period.

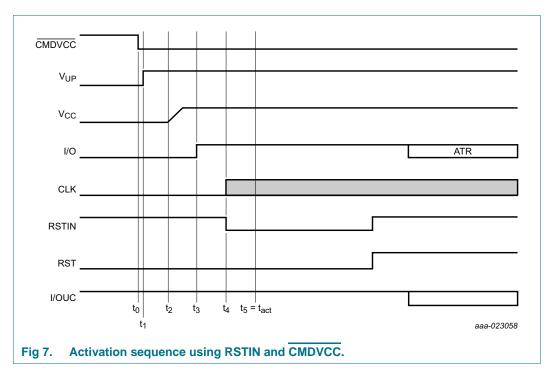

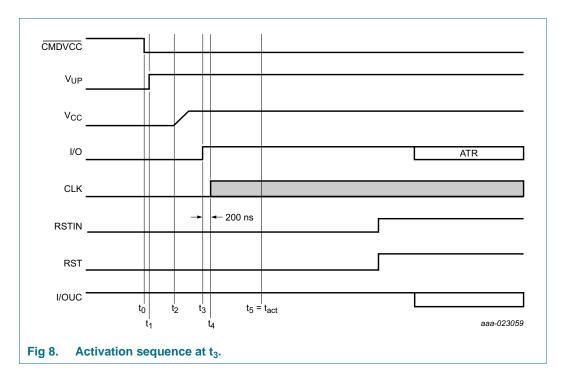

The crystal oscillator runs as soon as the IC is powered up. If the crystal oscillator is used, or if the clock pulse on pin XTAL1 is permanent, the clock pulse is applied to the card as shown in the activation sequences shown in Figure 7 and 8.

If the signal applied to XTAL1 is controlled by the system microcontroller, the clock pulse will be applied to the card when it is sent by the system microcontroller (after completion of the activation sequence).

### 8.4 I/O transceivers

The three data lines I/O, AUX1 and AUX2 are identical.

The Idle-state is realized by both I/O and I/OUC lines being pulled HIGH via a 11 k $\Omega$  resistor (I/O to V<sub>CC</sub> and I/OUC to V<sub>DD</sub>).

Pin I/O is referenced to  $V_{CC}$ , and pin I/OUC to  $V_{DD}$ , thus allowing operation when  $V_{CC}$  is not equal to  $V_{DD}$ .

The first side of the transceiver to receive a falling edge becomes the master. An anti-latch circuit disables the detection of falling edges on the line of the other side, which then becomes a slave.

After a time delay  $t_{d(edge)}$ , an N-transistor on the slave side is turned on, thus transmitting the logic 0 present on the master side.

When the master side returns to logic 1, a P-transistor on the slave side is turned on during the time delay  $t_{pu}$  and then both sides return to their idle states.

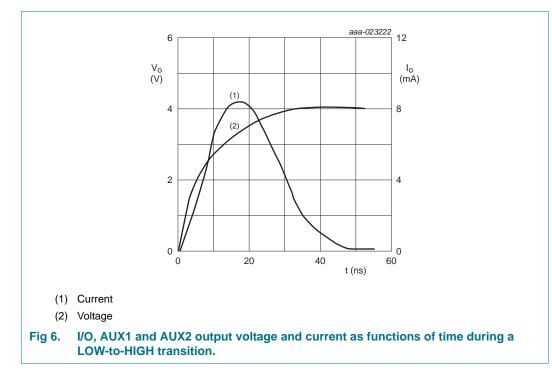

This active pull-up feature ensures fast LOW-to-HIGH transitions; as shown in Figure 6, it is able to deliver more than 1 mA at an output voltage of up to  $0.9V_{CC}$  into an 80 pF load. At the end of the active pull-up pulse, the output voltage depends only on the internal pull-up resistor and the load current.

The current to and from the card I/O lines is limited internally to 15 mA and the maximum frequency on these lines is 1 MHz.

TDA8024

11 of 33

# **TDA8024**

#### Standard smart card interface

### 8.5 Inactive mode

After a Power-on reset, the circuit enters the inactive mode. A minimum number of circuits are active while waiting for the microcontroller to start a session:

- All card contacts are inactive (approximately 200 Ω to GND)

- Pins I/OUC, AUX1UC and AUX2UC are in the high-impedance state (11 k $\Omega$  pull-up resistor to V\_DD)

- Voltage generators are stopped

- XTAL oscillator is running

- Voltage supervisor is active

- The internal oscillator is running at its low frequency

### 8.6 Activation sequence

After power-on and after the internal pulse width delay, the system microcontroller can check the presence of a card using the signals OFF and CMDVCC as shown in Table 5.

| Table 5. 0 | Card | presence | indication |

|------------|------|----------|------------|

|------------|------|----------|------------|

| OFF  | CMDVCC | Indication       |

|------|--------|------------------|

| HIGH | HIGH   | card present     |

| LOW  | HIGH   | card not present |

If the card is in the reader (this is the case if  $\overrightarrow{\mathsf{PRES}}$  or  $\overrightarrow{\mathsf{PRES}}$  is active), the system microcontroller can start a card session by pulling  $\overrightarrow{\mathsf{CMDVCC}}$  LOW. The following sequence then occurs (see Figure 6):

1.  $\overline{\text{CMDVCC}}$  is pulled LOW and the internal oscillator changes to its high frequency (t<sub>0</sub>).

# TDA8024

### Standard smart card interface

- 2. The voltage doubler is started (between  $t_0$  and  $t_1$ ).

- 3. V<sub>CC</sub> rises from 0 to 5 V (or 3 V) with a controlled slope ( $t_2 = t_1 + 1.5 \times T$ ) where T is 64 times the period of the internal oscillator (approximately 25  $\mu$ s).

- 4. I/O, AUX1 and AUX2 are enabled  $(t_3 = t_1 + 4T)$

(these were pulled LOW until this moment).

- 5. CLK is applied to the C3 contact of the card reader  $(t_4)$ .

- 6. RST is enabled ( $t_5 = t_1 + 7T$ ).

The clock may be applied to the card using the following sequence:

- 1. Set RSTIN HIGH.

- 2. Set CMDVCC LOW.

- 3. Reset RSTIN LOW between  $t_3$  and  $t_5;\,\mbox{CLK}$  will start at this moment.

- 4. RST remains LOW until  $t_5$ , when RST is enabled to be the copy of RSTIN.

- 5. After t<sub>5</sub>, RSTIN has no further affect on CLK; this allows a precise count of CLK pulses before toggling RST.

If the applied clock is not needed, then  $\overline{CMDVCC}$  may be set LOW with RSTIN LOW. In this case, CLK will start at  $t_3$  (minimum 200 ns after the transition on I/O), and after  $t_5$ , RSTIN may be set HIGH in order to obtain an Answer To Request (ATR) from the card.

Activation should not be performed with RSTIN held permanently HIGH.

# **TDA8024**

Standard smart card interface

# 8.7 Active mode

When the activation sequence is completed, the TDA8024 will be in its active mode. Data is exchanged between the card and the microcontroller via the I/O lines. The TDA8024 is designed for cards without  $V_{PP}$  (the voltage required to program or erase the internal non-volatile memory).

### 8.8 Deactive sequence

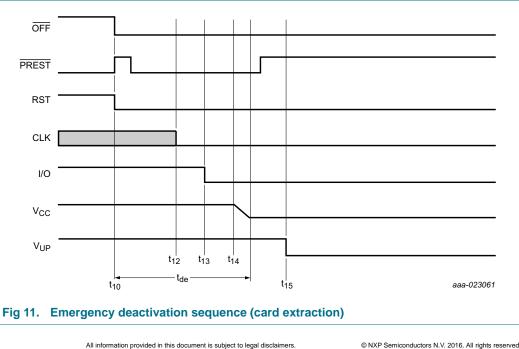

When a session is completed, the microcontroller sets the  $\overline{CMDVCC}$  line HIGH. The circuit then executes an automatic deactivation sequence by counting the sequencer back and finishing in the inactive mode (see Figure 9):

- 1. RST goes LOW  $(t_{10})$ .

- 2. CLK is held LOW ( $t_{12} = t_{10} + 0.5 \times T$ ) where T is 64 times the period of the internal oscillator (approximately 25 µs).

- 3. I/O, AUX1 and AUX2 are pulled LOW ( $t_{13} = t_{10} + T$ ).

- 4. V<sub>CC</sub> starts to fall towards zero ( $t_{14} = t_{10} + 1.5 \times T$ ).

- 5. The deactivation sequence is complete at  $t_{de}$ , when  $V_{CC}$  reaches its inactive state.

- 6.  $V_{UP}$  falls to zero ( $t_{15} = t_{10} + 5T$ ) and all card contacts become low-impedance to GND; I/OUC, AUX1UC and AUX2UC remain at  $V_{DD}$  (pulled-up via a 11 k $\Omega$  resistor).

- 7. The internal oscillator returns to its lower frequency.

# **TDA8024**

Standard smart card interface

### 8.9 V<sub>CC</sub> generator

The V<sub>CC</sub> generator has a capacity to supply up to 80 mA continuously at 5 V and 65 mA at 3 V.

An internal overload detector operates at approximately 120 mA. Current samples to the detector are internally filtered, allowing spurious current pulses up to 200 mA with a duration in the order of  $\mu$ s to be drawn by the card without causing deactivation. The average current must stay below the specified maximum current value.

For reasons of V<sub>CC</sub> voltage accuracy, a 100 nF capacitor with an ESR < 100 m $\Omega$  should be tied to CGND near to pin V<sub>CC</sub>, and a 100 nF or 220 nF capacitor (220 nF is the best choice) with the same ESR should be tied to CGND near card reader contact C1.

### 8.10 Fault detection

The following fault conditions are monitored:

- Short-circuit or high current on V<sub>CC</sub>

- Removal of a card during a transaction

- V<sub>DD</sub> dropping

- DC-to-DC converter operating out of the specified values (V<sub>DDP</sub> too low or current from V<sub>UP</sub> too high)

- Overheating

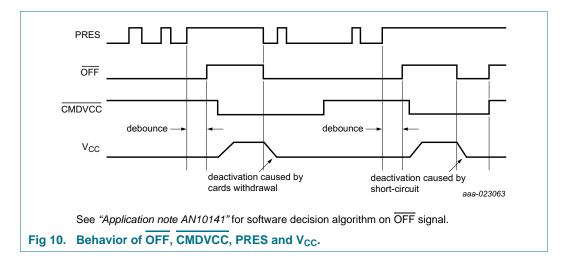

There are two different cases (see Figure 10):

CMDVCC HIGH outside a card session. Output OFF is LOW if a card is not in the card reader, and HIGH if a card is in the reader. A voltage drop on the V<sub>DD</sub> supply is detected by the supply supervisor, this generates an internal Power-on reset pulse but does not act upon OFF. No short-circuit or overheating is detected because the card is not powered-up.

TDA8024

15 of 33

• CMDVCC LOW within a card session. Output OFF goes LOW when a fault condition is detected. As soon as this occurs, an emergency deactivation is performed automatically (see Figure 11). When the system controller resets CMDVCC to HIGH it may sense the OFF level again after completing the deactivation sequence. This distinguishes between a hardware problem or a card extraction (OFF goes HIGH again if a card is present).

Depending on the type of card-present switch within the connector (normally-closed or normally-open) and on the mechanical characteristics of the switch, bouncing may occur on the PRES signals at card insertion or withdrawal.

There is a debounce feature in the device with an 8 ms typical duration (see Figure 10). When a card is inserted, output  $\overline{OFF}$  goes HIGH only at the end of the debounce time.

When the card is extracted, an automatic deactivation sequence of the card is performed on the first true/false transition on PRES or PRES and output OFF goes LOW.

# **TDA8024**

Standard smart card interface

# 9. Limiting values

#### Table 6. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                          | Parameter                         | Conditions                                                                                                     |        | Min  | Max  | Unit |

|---------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|--------|------|------|------|

| V <sub>DD</sub>                 | supply voltage                    |                                                                                                                |        | -0.3 | +6.5 | V    |

| V <sub>DDP</sub>                | DC-to-DC converter supply voltage |                                                                                                                |        | -0.3 | +6.5 | V    |

| V <sub>I</sub> , V <sub>O</sub> | voltage on input and output pins  | pins XTAL1, XTAL2, 5V/3V, RSTIN,<br>AUX1UC, <u>AUX2UC, I/OUC</u> , CLKDIV1,<br>CLKDIV2, CMDVCC, OFF and PORADJ |        | -0.3 | +6.5 | V    |

| V <sub>card</sub>               | voltage on card pins              | pins PRES, PRES, I/O, RST, AUX1, AUX2<br>and CLK                                                               |        | -0.3 | +6.5 | V    |

| V <sub>n</sub>                  | voltage on other pins             | pins V <sub>UP</sub> , S1 and S2                                                                               |        | -0.3 | +6.5 | V    |

| T <sub>j(max)</sub>             | maximum junction<br>temperature   |                                                                                                                |        | -    | 150  | °C   |

| T <sub>stg</sub>                | storage temperature               |                                                                                                                |        | -55  | +150 | °C   |

| V <sub>ESD</sub>                | electrostatic discharge           | card contacts in typical application;[1][2]                                                                    |        |      | I    |      |

|                                 | voltage                           | pins I/O, R <u>ST, V<sub>C</sub>C</u> , AUX1, AUX2, CLK, PRES and PRES                                         |        | -6   | +6   | kV   |

|                                 |                                   | all pins; <sup>[1]</sup>                                                                                       |        |      |      |      |

|                                 |                                   | Human Body Model (HBM)                                                                                         | [2][3] | -2   | +2   | kV   |

|                                 |                                   | Machine Model (MM)                                                                                             | [4]    | -200 | +200 | V    |

[1] All card contacts are protected against any short-circuit with any other card contact.

[2] Every pin withstands the ESD test according to MIL-STD-883C class 3 for card contacts, class 2 for the remaining. Method 3015 (HBM; 1500  $\Omega$  and 100 pF) 3 pulses positive and 3 pulses negative on each pin referenced to ground.

[3] In accordance with EIA/JESD22-A114-B, June 2000.

[4] In accordance with EIA/JESD22-A115-A, October 1997.

# **10. Thermal characteristics**

#### Table 7. Thermal characteristics

| Symbol               | Parameter                        | Conditions  | Тур    | Unit    |

|----------------------|----------------------------------|-------------|--------|---------|

| R <sub>th(j-a)</sub> | thermal resistance from junction | in free air |        |         |

|                      | to ambient                       |             | 70     | K/W     |

|                      | TDA8024T                         |             | 70     | K/W     |

|                      | TDA8024AT                        |             | 100[1] | K/W     |

|                      | TDA8024TT                        |             | 1000   | r\/ v v |

This figure was obtained using the following Printed-Circuit Board (PCB) technology: FR, 4 layers, 0.5 mm thickness, class 5, copper thickness 35 μm, Ni/Go plating, ground plane in internal layers.

17 of 33

# **TDA8024**

# **11. Characteristics**

#### Table 8. Characteristics

$V_{DD} = 3.3 \text{ V}; V_{DDP} = 5 \text{ V}; T_{amb} = 25 \text{ °C}; f_{XTAL} = 10 \text{ MHz}; all currents flowing into the IC are positive: see <u>Table note 1</u>; unless otherwise specified.$

| Symbol                     | Parameter                                                                 | Conditions                                                                    | Min        | Тур        | Max        | Unit   |

|----------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------|------------|------------|--------|

| Temperatur                 | e                                                                         |                                                                               |            |            |            |        |

| T <sub>amb</sub>           | ambient temperature                                                       |                                                                               | -25        | -          | +85        | °C     |

| Supplies                   | I                                                                         |                                                                               |            |            |            |        |

| V <sub>DD</sub>            | supply voltage                                                            |                                                                               | 2.7        | -          | 6.5        | V      |

| V <sub>DDP</sub>           | DC-to-DC converter                                                        | $V_{CC} = 5 \text{ V};  I_{CC}  < 80 \text{ mA}$                              | 4.0        | 5.0        | 6.5        | V      |

|                            | supply voltage                                                            | $V_{CC} = 5 \text{ V};  I_{CC}  < 20 \text{ mA}$                              | 3.0        | -          | 6.5        | V      |

| I <sub>DD</sub>            | supply current                                                            | card inactive                                                                 | -          | -          | 1.2        | mA     |

|                            |                                                                           | card active; $f_{CLK} = f_{XTAL}$ ;<br>C <sub>L</sub> = 30 pF                 | -          | -          | 1.5        | mA     |

| I <sub>DDP</sub>           | DC-to-DC converter supply                                                 | inactive mode                                                                 | -          | -          | 0.1        | mA     |

|                            | current                                                                   | active mode; $f_{CLK} = f_{XTAL}$ ;<br>$C_L = 30 \text{ pF}$ ; $ I_{CC}  = 0$ | -          | -          | 10         | mA     |

|                            |                                                                           | V <sub>CC</sub> = 5 V;  I <sub>CC</sub>   = 80 mA                             | -          | -          | 200        | mA     |

|                            |                                                                           | V <sub>CC</sub> = 3 V;  I <sub>CC</sub>   = 65 mA                             | -          | -          | 100        | mA     |

| V <sub>th2</sub>           | falling threshold voltage on $V_{\text{DD}}$                              | no external resistors at pin<br>PORADJ; V <sub>DD</sub> level falling         | 2.35       | 2.45       | 2.55       | V      |

| V <sub>hys2</sub>          | hysteresis of threshold voltage V <sub>th2</sub>                          | no external resistors at pin<br>PORADJ                                        | 50         | 100        | 150        | mV     |

| Pin PORAD                  | J <u>[2]</u>                                                              | 1                                                                             |            |            |            |        |

| V <sub>th(ext)(rise)</sub> | external rising threshold voltage on $V_{\text{DD}}$                      | external resistor bridge at pin<br>PORADJ; V <sub>DD</sub> level rising       | 1.240      | 1.28       | 1.310      | V      |

| V <sub>th(ext)(fall)</sub> | external falling threshold voltage on $V_{DD}$                            | external resistor bridge at pin<br>PORADJ; V <sub>DD</sub> level falling      | 1.190      | 1.22       | 1.26       | V      |

| V <sub>hys(ext)</sub>      | hysteresis of threshold voltage $Vt_{h(ext)}$                             | external resistor bridge at pin<br>PORADJ                                     | 30         | 60         | 90         | mV     |

| $\Delta V_{hys(ext)}$      | hysteresis of threshold voltage $V_{th(ext)}$ variation with temperature  | external resistor bridge at pin<br>PORADJ                                     | -          | -          | 0.25       | mV/k   |

| t <sub>w</sub>             | width of internal Power-on reset pulse                                    | no external resistors at pin<br>PORADJ                                        | 4          | 8          | 12         | ms     |

|                            |                                                                           | external resistor bridge at pin<br>PORADJ                                     | 8          | 16         | 24         | ms     |

| I <sub>L(PORADJ)</sub>     | leakage current on pin                                                    | VPORADJ < 0.5 V                                                               | -0.1       | 4          | 10         | μA     |

|                            | PORADJ                                                                    | VPORADJ > 1 V                                                                 | -1         | -          | +1         | μA     |

| P <sub>tot</sub>           | total power dissipation                                                   | continuous operation;<br>$T_{amb} = -25$ to +85 °C                            | -          | -          | 0.56       | W      |

| DC-to-DC c                 | onverter                                                                  |                                                                               |            |            | 1          |        |

| f <sub>CLK</sub>           | clock frequency                                                           | card active                                                                   | 2.2        | -          | 3.2        | MHz    |

| V <sub>th(vd-vf)</sub>     | threshold voltage for<br>voltage doubler to change<br>to voltage follower | 5 V card<br>3 V card                                                          | 5.2<br>3.8 | 5.8<br>4.1 | 6.2<br>4.4 | V<br>V |

# **TDA8024**

Standard smart card interface

#### Table 8. Characteristics ...continued

$V_{DD} = 3.3 \text{ V}; V_{DDP} = 5 \text{ V}; T_{amb} = 25 \text{ °C}; f_{XTAL} = 10 \text{ MHz}; all currents flowing into the IC are positive: see <u>Table note 1</u>; unless otherwise specified.$

| Symbol                                     | Parameter                                                 | Conditions                                                                              | Min          | Тур  | Max                 | Unit |  |

|--------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------|------|---------------------|------|--|

| V <sub>UP(av)</sub>                        | output voltage on pin V <sub>UP</sub>                     | $V_{CC} = 5 V$                                                                          | 5.2          | 5.7  | 6.2                 | V    |  |

|                                            | (average value)                                           | V <sub>CC</sub> = 3 V; V <sub>DDP</sub> = 3.3 V                                         | 3.5          | 3.9  | 4.3                 | V    |  |

| Card supply                                | voltage (pin V <sub>CC</sub> ) <u><sup>[3]</sup></u>      |                                                                                         | I            |      | I                   | -    |  |

| C <sub>VCC</sub>                           | external capacitance on pin $V_{CC}$                      | Ŀ                                                                                       | <u>4]</u> 80 | -    | 400                 | nF   |  |

| V <sub>CC</sub>                            | card supply voltage                                       | 5 V card                                                                                |              |      |                     | _    |  |

|                                            | (including ripple voltage)                                | card inactive;  I <sub>CC</sub>   = 0 mA                                                | -0.1         | 0    | +0.1                | V    |  |

|                                            |                                                           | card inactive; $ I_{CC}  = 1 \text{ mA}$                                                | -0.1         | 0    | +0.3                | V    |  |

|                                            |                                                           | card active;  I <sub>CC</sub>   < 80 mA                                                 | 4.75         | 5.0  | 5.25                | V    |  |

|                                            |                                                           | card active; single current<br>pulse, $I_p = -100 \text{ mA}$ ;<br>$t_p = 2 \text{ ms}$ | 4.65         | 5.0  | 5.25                | V    |  |

|                                            |                                                           | card active; current pulses,<br>$I_p = 40 \text{ nAs}$                                  | 4.65         | 5.0  | 5.25                | V    |  |

|                                            |                                                           | card active; current pulses,<br>$I_p = 40$ nAs with $ I_{CC}  < 200$ mA; $t_p < 400$ ns | 4.65         | 5.0  | 5.25                | V    |  |

|                                            |                                                           | 3 V card                                                                                |              |      |                     |      |  |

|                                            |                                                           | card inactive;  I <sub>CC</sub>   = 0 mA                                                | -0.1         | 0    | +0.1                | V    |  |

|                                            |                                                           | card inactive;  I <sub>CC</sub>   = 1 mA                                                | -0.1         | 0    | +0.3                | V    |  |

|                                            |                                                           | card active;  I <sub>CC</sub>   < 65 mA                                                 | 2.85         | 3.0  | 3.15                | V    |  |

|                                            |                                                           | card active; single current pulse, $I_p = -100 \text{ mA}$ ; $t_p = 2 \text{ ms}$       | 2.76         | 3.0  | 3.20                | V    |  |

|                                            |                                                           | card active; current pulses,<br>I <sub>p</sub> = 40 nAs                                 | 2.76         | 3.0  | 3.20                | V    |  |

|                                            |                                                           | card active; current pulses,<br>$I_p = 40$ nAs with $ I_{CC}  < 200$ mA; $t_p < 400$ ns | 2.76         | 3.0  | 3.20                | V    |  |

| V <sub>CC(ripple)(p-p)</sub>               | ripple voltage on V <sub>CC</sub><br>(peak to peak value) | f <sub>ripple</sub> = 20 kHz to 200 MHz                                                 | -            | -    | 350                 | mV   |  |

| I <sub>CC</sub>                            | card supply current                                       | $V_{CC} = 0$ to 5 V                                                                     | -            | -    | 80                  | mA   |  |

|                                            |                                                           | $V_{CC} = 0$ to 3 V                                                                     | -            | -    | 65                  | mA   |  |

|                                            |                                                           | V <sub>CC</sub> short-circuit to GND                                                    | 100          | 120  | 150                 | mA   |  |

| SR                                         | slew rate                                                 | slew up or down                                                                         | 0.08         | 0.15 | 0.22                | V/μs |  |

| Crystal oscil                              | lator (pins XTAL1 and XTAL                                | 2)                                                                                      |              |      |                     |      |  |

| C <sub>XTAL1</sub> ,<br>C <sub>XTAL2</sub> | external capacitance on pins XTAL1 and XTAL2              | depends on type of crystal or<br>resonator used                                         | -            | -    | 15                  | pF   |  |

| f <sub>XTAL</sub>                          | crystal frequency                                         |                                                                                         | 2            | -    | 26                  | MHz  |  |

| f <sub>XTAL1</sub>                         | frequency applied on pin<br>XTAL1                         |                                                                                         | 0            | -    | 26                  | MHz  |  |

| V <sub>IL</sub>                            | LOW-level input voltage on pin XTAL1                      |                                                                                         | -0.3         | -    | +0.3V <sub>DD</sub> | V    |  |

TDA8024 Product data sheet

# **TDA8024**

Standard smart card interface

#### Table 8. Characteristics ...continued

$V_{DD} = 3.3 \text{ V}; V_{DDP} = 5 \text{ V}; T_{amb} = 25 \text{ °C}; f_{XTAL} = 10 \text{ MHz}; all currents flowing into the IC are positive: see <u>Table note 1</u>; unless otherwise specified.$

| Symbol                                                   | Parameter                                     | Conditions                                                                                                                      | Min                 | Тур        | Max                   | Unit              |

|----------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|-----------------------|-------------------|

| V <sub>IH</sub>                                          | HIGH-level input voltage on pin XTAL1         |                                                                                                                                 | 0.7V <sub>DD</sub>  | -          | V <sub>DD</sub> + 0.3 | V                 |

| Data lines (                                             | oins I/O, I/OUC, AUX1, AUX2                   | , AUX1UC and AUX2UC)                                                                                                            |                     | _          |                       |                   |

| t <sub>d(I/O-I/OUC)</sub> ,<br>t <sub>d(I/OUC-I/O)</sub> | I/O to I/OUC, I/OUC to I/O falling edge delay |                                                                                                                                 | -                   | -          | 200                   | ns                |

| t <sub>pu</sub>                                          | active pull-up pulse width                    |                                                                                                                                 | -                   | -          | 100                   | ns                |

| f <sub>I/O(max)</sub>                                    | maximum frequency on data lines               |                                                                                                                                 | -                   | -          | 1                     | MHz               |

| Ci                                                       | input capacitance on data lines               |                                                                                                                                 | -                   | -          | 10                    | pF                |

| Data lines to                                            | o card reader (pins I/O, AUX                  | 1 and AUX2; with integrated 11                                                                                                  | kΩ pull-up res      | sistors to | V <sub>CC</sub> )     |                   |

| V <sub>o(inactive)</sub> output voltage                  |                                               | inactive mode                                                                                                                   |                     |            |                       |                   |

|                                                          |                                               | no load                                                                                                                         | 0                   | -          | 0.1                   | V                 |

|                                                          |                                               | I <sub>o(inactive)</sub> = 1 mA                                                                                                 | -                   | -          | 0.3                   | V                 |

| I <sub>o(inactive)</sub>                                 | output current                                | inactive mode; pin grounded                                                                                                     | -                   | -          | -1                    | mA                |

| V <sub>OL</sub>                                          | LOW-level output voltage                      | I <sub>OL</sub> = 1 mA                                                                                                          | 0                   | -          | 0.3                   | V                 |

|                                                          |                                               | $I_{OL} \ge 15 \text{ mA}$                                                                                                      | $V_{CC}-0.4$        | -          | V <sub>CC</sub>       | V                 |

| V <sub>OH</sub>                                          | HIGH-level output voltage                     | no DC load                                                                                                                      | 0.9V <sub>CC</sub>  | -          | V <sub>CC</sub> + 0.1 | V                 |

|                                                          |                                               | 5 V and 3 V cards;<br>I <sub>OH</sub> < -40 μA                                                                                  | 0.75V <sub>CC</sub> | -          | V <sub>CC</sub> + 0.1 | V                 |

|                                                          |                                               | $ I_{OH}  \ge 10 \text{ mA}$                                                                                                    | 0                   | -          | 0.4                   | V                 |

| V <sub>IL</sub>                                          | LOW-level input voltage                       |                                                                                                                                 | 0.3                 | -          | 0.8                   | V                 |

| V <sub>IH</sub>                                          | HIGH-level input voltage                      |                                                                                                                                 | 1.5                 | -          | V <sub>CC</sub> + 0.3 | V                 |

| I <sub>IL</sub>                                          | LOW-level input current                       | V <sub>IL</sub> = 0 V                                                                                                           | -                   | -          | 600                   | μA                |

| II <sub>LIH</sub>                                        | HIGH-level input leakage current              | V <sub>IH</sub> = V <sub>CC</sub>                                                                                               | -                   | -          | 10                    | μA                |

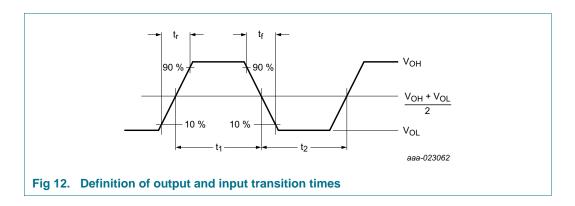

| t <sub>t(DI)</sub>                                       | data input transition time                    | V <sub>IL(max)</sub> to V <sub>IH(min)</sub>                                                                                    | -                   | -          | 1.2                   | μS                |

| t <sub>t(DO)</sub>                                       | data output transition time                   | $\label{eq:V_o} \begin{array}{l} V_{o} = 0 \mbox{ to } V_{CC};  C_{L} \leq 80 \mbox{ pF}; \\ 10\% \mbox{ to } 90\% \end{array}$ | -                   | -          | 0.1                   | μs                |

| R <sub>pu</sub>                                          | integrated pull-up resistor                   | pull-up resistor to V <sub>DD</sub>                                                                                             | 9                   | 11         | 13                    | kΩ                |

| I <sub>pu</sub>                                          | current when pull-up active                   | V <sub>OH</sub> = 0.9V <sub>CC</sub> ; C = 80 pF                                                                                | -1                  | -          | -                     | mA                |

| Data lines to                                            | o microcontroller (pins I/OU                  | C, AUX1UC and AUX2UC; with                                                                                                      | integrated 11       | kΩ pull-u  | p resistors to        | V <sub>DD</sub> ) |

| V <sub>OL</sub>                                          | LOW-level output voltage                      | I <sub>OL</sub> = 1 mA                                                                                                          | 0                   | -          | 0.3                   | V                 |

| V <sub>OH</sub>                                          | HIGH-level output voltage                     | no DC load                                                                                                                      | 0.9V <sub>DD</sub>  | -          | V <sub>DD</sub> + 0.1 | V                 |

|                                                          |                                               | 5 V and 3 V cards;<br>I <sub>OH</sub> < -40 μA                                                                                  | 0.75V <sub>DD</sub> | -          | V <sub>DD</sub> + 0.1 | V                 |

| V <sub>IL</sub>                                          | LOW-level input voltage                       |                                                                                                                                 | -0.3                | -          | +0.3V <sub>DD</sub>   | V                 |

| VIH                                                      | HIGH-level input voltage                      |                                                                                                                                 | 0.7V <sub>DD</sub>  | -          | V <sub>DD</sub> + 0.3 | V                 |

| I <sub>LIH</sub>                                         | HIGH-level input leakage current              | $V_{IH} = V_{DD}$                                                                                                               | -                   | -          | 10                    | μA                |

| I <sub>IL</sub>                                          | LOW-level input current                       | V <sub>IL</sub> = 0 V                                                                                                           | -                   | -          | 600                   | μA                |

|                                                          | data input transition time                    | V <sub>IL(max)</sub> to V <sub>IH(min)</sub>                                                                                    |                     | _          |                       | +                 |

TDA8024 Product data sheet © NXP Semiconductors N.V. 2016. All rights reserved.

# **TDA8024**

Standard smart card interface

#### Table 8. Characteristics ...continued

$V_{DD} = 3.3 \text{ V}; V_{DDP} = 5 \text{ V}; T_{amb} = 25 \text{ °C}; f_{XTAL} = 10 \text{ MHz}; all currents flowing into the IC are positive: see <u>Table note 1</u>; unless otherwise specified.$

| Symbol                                      | Parameter                            | Conditions                                                                    | Min                | Тур | Мах                   | Unit |  |

|---------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------|--------------------|-----|-----------------------|------|--|

| t <sub>t(DO)</sub>                          | data output transition time          | V <sub>o</sub> = 0 to V <sub>DD</sub> ; C <sub>L</sub> < 30 pF;<br>10% to 90% | -                  | -   | 0.1                   | μS   |  |

| R <sub>pu</sub>                             | integrated pull-up resistor          | pull-up resistor to V <sub>DD</sub>                                           | 9                  | 11  | 13                    | kΩ   |  |

| I <sub>pu</sub>                             | current when pull-up active          | V <sub>OH</sub> = 0.9V <sub>DD</sub> ; C = 30 pF                              | -1                 | -   | -                     | mA   |  |

| Internal osci                               | llator                               |                                                                               |                    |     |                       |      |  |

| f <sub>OSC(int)</sub> frequency of internal |                                      | inactive mode                                                                 | 55                 | 140 | 200                   | kHz  |  |

|                                             | oscillator                           | active mode                                                                   | 2.2                | 2.7 | 3.2                   | MHz  |  |

| Reset output                                | t to card reader (pin RST)           |                                                                               |                    |     | i                     |      |  |

| V <sub>o(inactive)</sub>                    | output voltage                       | inactive mode                                                                 |                    |     |                       |      |  |

|                                             |                                      | no load                                                                       | 0                  | -   | 0.1                   | V    |  |

|                                             |                                      | I <sub>o(inactive)</sub> = 1 mA                                               | 0                  | -   | 0.3                   | V    |  |

| I <sub>o(inactive)</sub>                    | output current                       | inactive mode; pin grounded                                                   | -                  | -   | -1                    | mA   |  |

| t <sub>d(RSTIN-RST)</sub>                   | RSTIN to RST delay                   | RST enabled                                                                   | -                  | -   | 2                     | μs   |  |

| V <sub>OL</sub>                             | LOW-level output voltage             | I <sub>OL</sub> = 200 μA                                                      | 0                  | -   | 0.2                   | V    |  |

|                                             |                                      | I <sub>OL</sub> = 20 mA (current limit)                                       | $V_{CC}-0.4$       | -   | V <sub>CC</sub>       | V    |  |

| V <sub>OH</sub>                             | HIGH-level output voltage            | I <sub>OH</sub> = -200 μA                                                     | 0.9V <sub>CC</sub> | -   | V <sub>CC</sub>       | V    |  |

|                                             |                                      | I <sub>OH</sub> = -20 mA (current limit)                                      | 0                  | -   | 0.4                   | V    |  |

| t <sub>r</sub>                              | rise time                            | $C_L = 100 \text{ pF}; V_{CC} = 5 \text{ V or } 3 \text{ V}$                  | -                  | -   | 0.1                   | μS   |  |

| t <sub>f</sub>                              | fall time                            | $C_L$ = 100 pF; $V_{CC}$ = 5 V or 3 V                                         | -                  | -   | 0.1                   | μs   |  |

| Clock output                                | t to card reader (pin CLK)           |                                                                               |                    |     | Ċ                     |      |  |

| V <sub>o(inactive)</sub> output voltage     |                                      | inactive mode                                                                 |                    |     |                       |      |  |

|                                             |                                      | no load                                                                       | 0                  | -   | 0.1                   | V    |  |

|                                             |                                      | I <sub>o(inactive)</sub> = 1 mA                                               | 0                  | -   | 0.3                   | V    |  |

| I <sub>o(inactive)</sub>                    | output current                       | CLK inactive; pin grounded                                                    | 0                  | -   | -1                    | mA   |  |

| V <sub>OL</sub>                             | LOW-level output voltage             | I <sub>OL</sub> = 200 μA                                                      | 0                  | -   | 0.3                   | V    |  |

|                                             |                                      | I <sub>OL</sub> = 70 mA (current limit)                                       | $V_{CC}-0.4$       | -   | V <sub>CC</sub>       | V    |  |

| V <sub>OH</sub>                             | HIGH-level output voltage            | I <sub>OH</sub> = -200 μA                                                     | 0.9V <sub>CC</sub> | -   | V <sub>CC</sub>       | V    |  |

|                                             |                                      | I <sub>OH</sub> = -70 mA (current limit)                                      | 0                  | -   | 0.4                   | V    |  |

| t <sub>r</sub>                              | rise time                            | C <sub>L</sub> = 30 pF [5]                                                    | -                  | -   | 16                    | ns   |  |

| t <sub>f</sub>                              | fall time                            | C <sub>L</sub> = 30 pF [5]                                                    | -                  | -   | 16                    | ns   |  |

| δ                                           | duty factor (except for $f_{XTAL}$ ) | C <sub>L</sub> = 30 pF [5]                                                    | 45                 | -   | 55                    | %    |  |

| SR                                          | slew rate                            | slew up or down; $C_L = 30 \text{ pF}$                                        | 0.2                | -   | -                     | V/ns |  |

| Control inpu                                | ts (pins CLKDIV1, CLKDIV2            | , CMDVCC, RSTIN and 5V/3V)[6]                                                 |                    | ·   |                       |      |  |

| VIL                                         | LOW-level input voltage              |                                                                               | -0.3               | -   | +0.3V <sub>DD</sub>   | V    |  |

| Viн                                         | HIGH-level input voltage             |                                                                               | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 | V    |  |

| I <sub>LIL</sub>                            | LOW-level input leakage current      | $0 < V_{IL} < V_{DD}$                                                         | -                  | -   | 1                     | μA   |  |

| ILIH                                        | HIGH-level input leakage current     | $0 < V_{IH} < V_{DD}$                                                         | -                  | -   | 1                     | μA   |  |

# **TDA8024**

Standard smart card interface

#### Table 8. Characteristics ...continued

$V_{DD}$  = 3.3 V;  $V_{DDP}$  = 5 V;  $T_{amb}$  = 25 °C;  $f_{XTAL}$  = 10 MHz; all currents flowing into the IC are positive: see <u>Table note 1</u>; unless otherwise specified.

| Symbol                | Parameter                                           | Conditions                               | Min                         | Тур | Max                   | Unit |

|-----------------------|-----------------------------------------------------|------------------------------------------|-----------------------------|-----|-----------------------|------|

| Card prese            | ence inputs (pins PRES and P                        | RES)[7]                                  | I                           |     |                       |      |

| Vil                   | LOW-level input voltage                             |                                          | -0.3                        | -   | +0.3V <sub>DD</sub>   | V    |

| Vih                   | HIGH-level input voltage                            |                                          | 0.7V <sub>DD</sub>          | -   | V <sub>DD</sub> + 0.3 | V    |

| ILIL                  | LOW-level input leakage current                     | $0 < V_{IL} < V_{DD}$                    | -                           | -   | 5                     | μA   |

| IILIH                 | HIGH-level input leakage current                    | $0 < V_{IH} < V_{DD}$                    | -                           | -   | 5                     | μA   |

| Interrupt o           | utput (pin OFF; NMOS drain v                        | with integrated 20 k $\Omega$ pull-up re | sistor to V <sub>DD</sub> ) | )   |                       |      |

| V <sub>OL</sub>       | LOW-level output voltage                            | $I_{OL} = 2 \text{ mA}$                  | 0                           | -   | 0.3                   | V    |

| V <sub>OH</sub>       | HIGH-level output voltage                           | I <sub>OH</sub> = -15 μA                 | 0.75V <sub>DD</sub>         | -   | -                     | V    |

| R <sub>pu</sub>       | integrated pull-up resistor                         | 20 k $\Omega$ pull-up resistor to V_{DD} | 16                          | 20  | 24                    | kΩ   |

| Protection            | and limitation                                      |                                          | I                           |     |                       |      |