# **MCP2518FDT-E/SL Datasheet**

www.digi-electronics.com

Μ

| DiGi Electronics Part Number | MCP2518FDT-E/SL-DG                           |

|------------------------------|----------------------------------------------|

| Manufacturer                 | Microchip Technology                         |

| Manufacturer Product Number  | MCP2518FDT-E/SL                              |

| Description                  | IC CAN CONTROLLER SPI 14SOIC                 |

| Detailed Description         | CAN Controller CAN 2.0 SPI Interface 14-SOIC |

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

### Purchase and inquiry

| Manufacturer Product Number:   | Manufacturer:            |

|--------------------------------|--------------------------|

| MCP2518FDT-E/SL                | Microchip Technology     |

| Series:                        | Product Status:          |

| Functional Safety (FuSa)       | Active                   |

| DiGi-Electronics Programmable: | Protocol:                |

| Not Verified                   | CAN                      |

| Function:                      | Interface:               |

| Controller                     | SPI                      |

| Standards:                     | Voltage - Supply:        |

| CAN 2.0                        | 2.7V ~ 5.5V              |

| Current - Supply:              | Operating Temperature:   |

| 20mA                           | -40°C ~ 125°C            |

| Package / Case:                | Supplier Device Package: |

| 14-SOIC (0.154", 3.90mm Width) | 14-SOIC                  |

| Base Product Number:           |                          |

| MCP2518                        |                          |

|                                |                          |

### **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 3 (168 Hours)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

# <u>MCP2518FD</u>

### **External CAN FD Controller with SPI Interface**

#### Features

#### <u>General</u>

- External CAN FD Controller with Serial Peripheral Interface (SPI)

- Arbitration Bit Rate up to 1 Mbps

- Data Bit Rate up to 8 Mbps

- CAN FD Controller modes

- Mixed CAN 2.0B and CAN FD Mode

- CAN 2.0B Mode

- Conforms to ISO 11898-1:2015

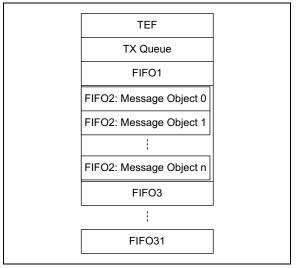

#### Message FIFOs

- 31 FIFOs, configurable as Transmit or Receive FIFOs

- One Transmit Queue (TXQ)

- · Transmit Event FIFO (TEF) with 32 bit time stamp

#### Message Transmission

- Message transmission prioritization:

- Based on priority bit field

- Message with lowest ID gets transmitted first using the Transmit Queue (TXQ)

- Programmable automatic retransmission attempts: unlimited, 3 attempts or disabled

#### Message Reception

- · 32 Flexible Filter and Mask Objects

- Each object can be configured to filter either:

- Standard ID + first 18 data bits, or

- Extended ID

- · 32-bit Time Stamp

#### **Special Features**

- VDD: 2.7 to 5.5V

- Active Current: maximum 20 mA at 5.5 V, 40 MHz CAN clock

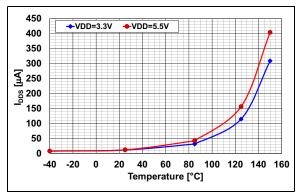

- Sleep Current: 15 μA, typical

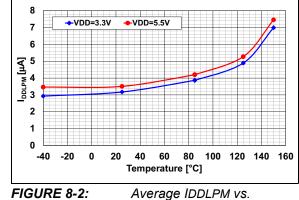

- Low Power Mode current: maximum 10  $\mu A$  from -40°C to +150°C

- · Message Objects are located in RAM: 2 KB

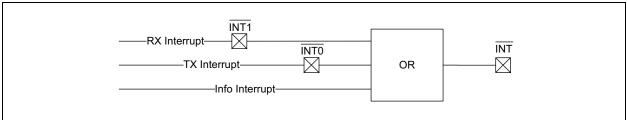

- Up to 3 Configurable Interrupt Pins

- Bus Health Diagnostics and Error Counters

- Transceiver Standby Control

- Start of frame pin for indicating the beginning of messages on the bus

- AEC-Q100 Qualified

- Temperature Ranges:

- Extended (E): -40°C to +125°C

- High (H): -40°C to +150°C

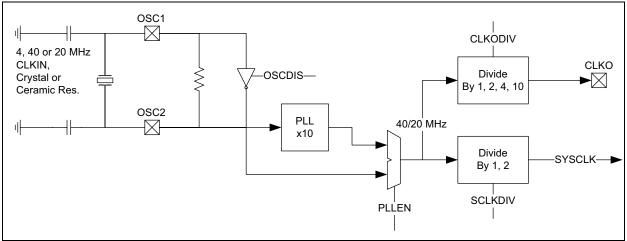

#### Oscillator Options

- 40, 20 or 4 MHz Crystal or Ceramic Resonator; External Clock Input

- · Clock Output with Prescaler

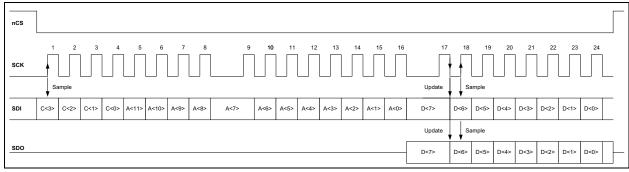

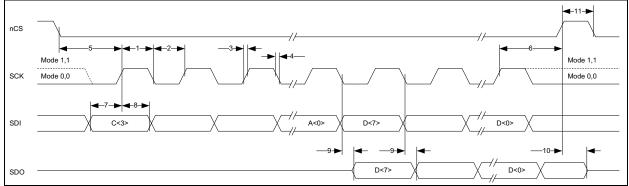

#### SPI Interface

- Up to 20 MHz SPI clock speed

- Supports SPI Modes 0, 0 and 1, 1

- Registers and bit fields are arranged in a way to enable efficient access through SPI

#### Safety Critical Systems

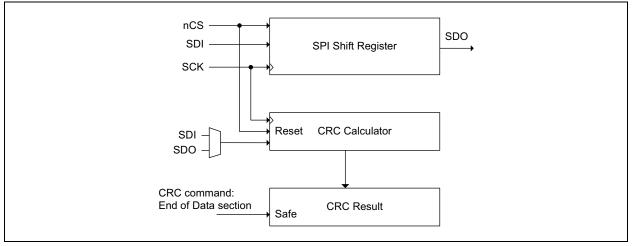

- SPI commands with CRC to detect noise on SPI interface

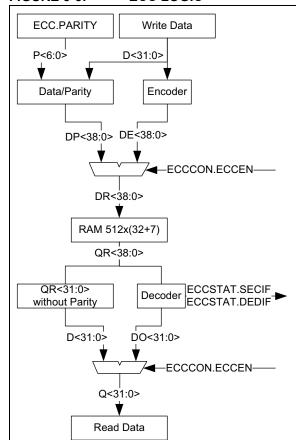

- Error Correction Code (ECC) protected RAM

#### **Additional Features**

- GPIO pins: INT0 and INT1 can be configured as general purpose I/O

- Open drain outputs: TXCAN, INT, INTO, and INT1 pins can be configured as push/pull or open drain outputs

- ISO 26262 Functional Safety ready

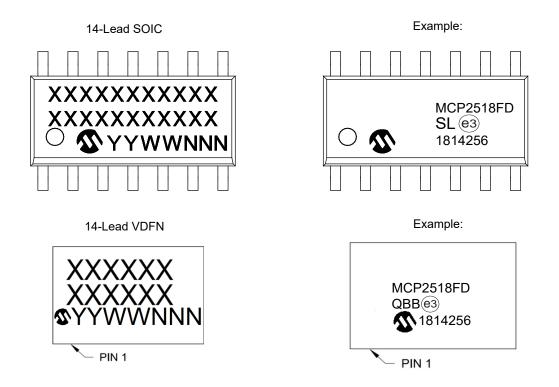

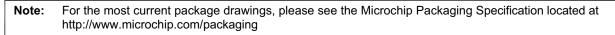

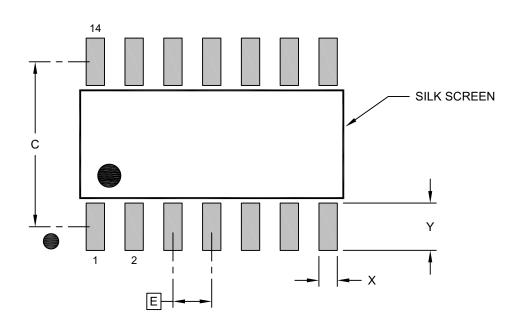

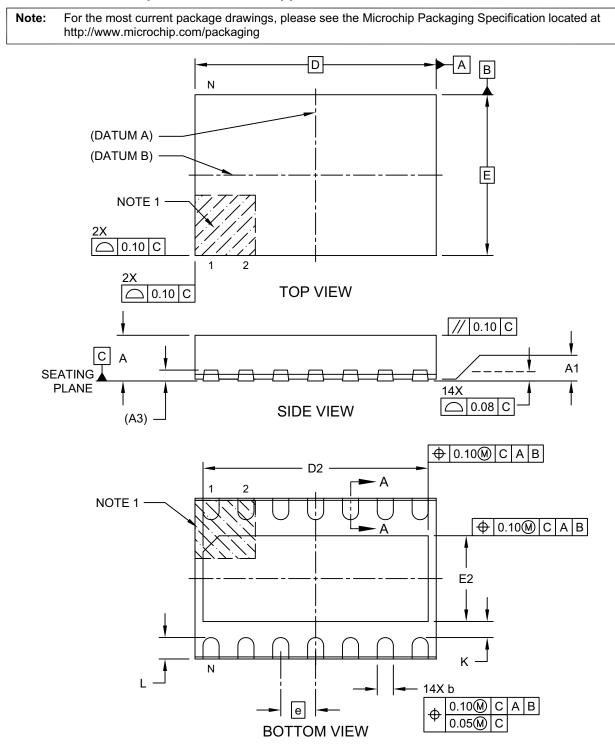

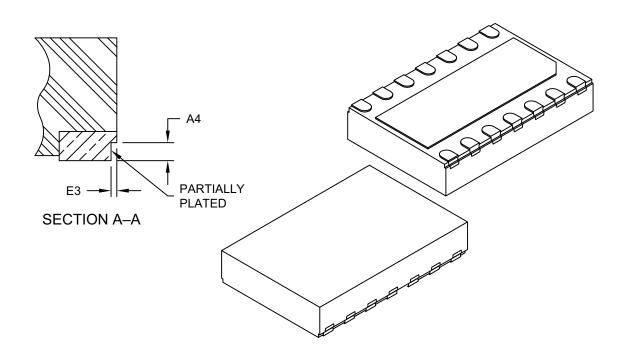

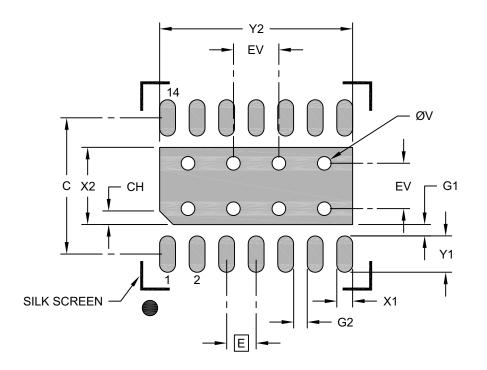

### Package Types

|                          | N    | ICP251                    | FD                           |           |

|--------------------------|------|---------------------------|------------------------------|-----------|

|                          |      | SOIC1                     | 4                            |           |

| TXCAI                    | N [] | $\bigcirc$                | 14 VDD                       |           |

| RXCA                     | N 2  |                           | 13 nCS                       |           |

| CLKO/SO                  | F 3  |                           | 12 SDO                       |           |

| IN                       | т (4 |                           | 11 SDI                       |           |

| OSC                      | 2 5  |                           | 10 scк                       |           |

| OSC                      | 1 6  |                           | 9 INT0/GPIO0/                | XSTBY     |

| VS                       | s 7  |                           | 8 INT1/GPIO1                 |           |

| VDF                      |      | <b>/ICP251</b><br>with we | 3 <b>FD</b><br>table flanks* |           |

| TXCAN                    | 1]   | /                         | 14 VDD                       |           |

| RXCAN                    | 2    |                           | 13 nCS                       |           |

| CLKO/SOF                 | 3    |                           | 12 SDO                       |           |

| INT                      | 4    | EP*                       | 11 SDI                       |           |

| OSC2                     | 5    |                           | 10 SCK                       |           |

| OSC1                     | 6    |                           | 9 INT0/GPIO0/2               | XSTBY     |

| VSS                      | 7    |                           | 8 INT1/GPIO1                 |           |

| VDFN14 incl<br>Table 1-1 | udes | an Expo                   | ed Thermal Pad               | (EP); see |

### 1.0 DEVICE OVERVIEW

The MCP2518FD device is a cost-effective and small-footprint CAN FD controller that can be easily added to a microcontroller with an available SPI interface. A CAN FD channel can be easily added to a microcontroller that is either lacking a CAN FD peripheral or does not have enough CAN FD channels.

MCP2518FD supports both CAN frames in the Classical format (CAN2.0B) and CAN Flexible Data Rate (CAN FD) format, as specified in ISO 11898-1:2015.

The MCP2518FD device was improved as follows:

- Added Low Power Mode (LPM), in order to reduce leakage current to 10  $\mu A$  over the full temperature range.

- Extended SEQ field in Transmit Message Object and Transmit Event FIFO Object from 7 to 23 bits.

- Added DEVID register to distinguish between future members of the device family.

- Switched to saw cut DFN package with wettable flanks.

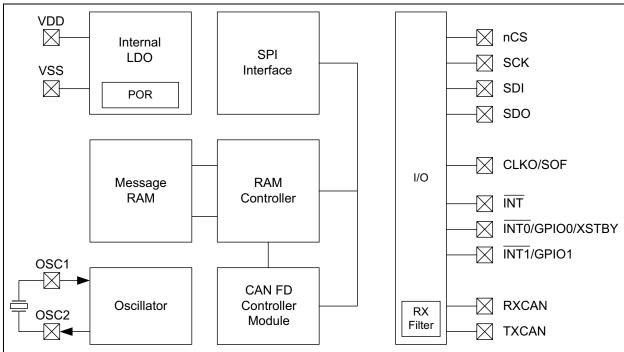

### 1.1 Block Diagram

Figure 1.1 shows the block diagram of the MCP2518FD device. MCP2518FD contains the following main blocks:

- The CAN FD Controller module implements the CAN FD protocol, and contains the FIFOs and Filters.

- The SPI interface is used to control the device by accessing Special Function Registers (SFR) and RAM.

- The RAM controller arbitrates the RAM accesses between the SPI and CAN FD Controller module.

- The Message RAM is used to store the data of the Message Objects.

- The oscillator generates the CAN clock.

- The Internal LDO and POR circuit.

- The I/O control.

Note 1: This data sheet summarizes the features of the MCP2518FD device. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP25xxFD Family Reference Manual".

### FIGURE 1-1: MCP2518FD BLOCK DIAGRAM

### 1.2 Pinout Description

Table 1-1 describes the functions of the pins.

#### TABLE 1-1: MCP2518FD STANDARD PINOUT VERSION

| Pin Name             | SOIC | VDFN | Pin Type | Description                                                          |

|----------------------|------|------|----------|----------------------------------------------------------------------|

| TXCAN                | 1    | 1    | 0        | Transmit output to CAN FD transceiver                                |

| RXCAN                | 2    | 2    | I        | Receive input from CAN FD transceiver                                |

| CLKO/SOF             | 3    | 3    | 0        | Clock output/Start of Frame output                                   |

| INT                  | 4    | 4    | 0        | Interrupt output (active low)                                        |

| OSC2                 | 5    | 5    | 0        | External oscillator output                                           |

| OSC1                 | 6    | 6    | I        | External oscillator input                                            |

| Vss                  | 7    | 7    | Р        | Ground                                                               |

| INT1/GPIO1           | 8    | 8    | I/O      | RX Interrupt output (active low)/GPIO                                |

| INT0/GPIO0/<br>XSTBY | 9    | 9    | I/O      | TX Interrupt output (active low)/GPIO/<br>Transceiver Standby output |

| SCK                  | 10   | 10   | I        | SPI clock input                                                      |

| SDI                  | 11   | 11   | I        | SPI data input                                                       |

| SDO                  | 12   | 12   | 0        | SPI data output                                                      |

| nCS                  | 13   | 13   | I        | SPI chip select input                                                |

| Vdd                  | 14   | 14   | Р        | Positive Supply                                                      |

| EP                   | -    | 15   | Р        | Exposed Pad; connect to Vss                                          |

Legend: P = Power, I = Input, O = Output

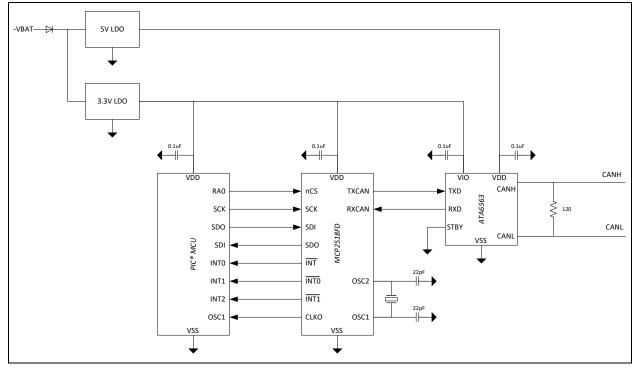

### **1.3** Typical Application

Figure 1-2 shows an example of a typical application of the MCP2518FD device. In this example, the microcontroller operates at 3.3V.

The MCP2518FD device interfaces directly with microcontrollers operating at 2.7V to 5.5V. In addition, the MCP2518FD device connects directly to high-speed CAN FD transceivers. There are no external level shifters required when connecting VDD of the MCP2518FD and the microcontroller to VIO of the transceiver.

The VDD of the CAN FD transceiver is connected to 5V.

The SPI interface is used to configure and control the CAN FD controller.

The MCP2518FD device signals interrupts to the microcontroller by using INT, INT0 and INT1. Interrupts need to be cleared by the microcontroller through SPI.

The CLKO pin provides the clock to the microcontroller.

#### FIGURE 1-2: MCP2518FD INTERFACING WITH A 3.3V MICROCONTROLLER

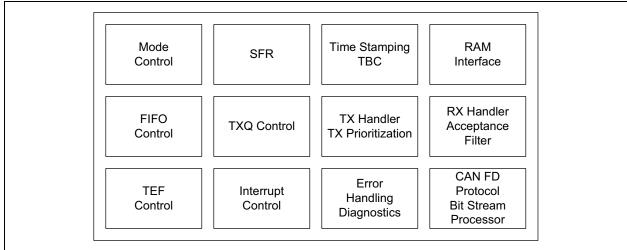

### 2.0 CAN FD CONTROLLER MODULE

Figure 2-1 shows the main blocks of the CAN FD Controller module:

- The CAN FD Controller module has multiple modes:

- Configuration

- Normal CAN FD

- Normal CAN 2.0

- Sleep (normal Sleep mode and Low Power Mode)

- Listen Only

- Restricted Operation

- Internal and External Loop back modes

- The CAN FD Bit Stream Processor (BSP) implements the Medium Access Control of the CAN FD protocol described in ISO 11898-1:2015. It serializes and de-serializes the bit stream, encodes and decodes the CAN FD frames, manages the medium access, acknowledges frames and detects and signals errors.

- The TX Handler prioritizes the messages that are requested for transmission by the Transmit FIFOs. It uses the RAM Interface to fetch the transmit data from RAM and provides it to the BSP for transmission.

- The BSP provides received messages to the RX Handler. The RX Handler uses the Acceptance Filter to filter out messages that shall be stored into Receive FIFOs. It uses the RAM Interface to store received data into RAM.

- Each FIFO can be configured either as a Transmit or Receive FIFO. The FIFO Control keeps track of the FIFO Head and Tail, and calculates the User Address. For a TX FIFO, the User Address points to the address in RAM where the data for the next transmit message shall be stored. For a RX FIFO, the User Address points to the address in RAM where the data of the next receive message shall be read. The User notifies the FIFO that a message was written to or read from RAM by incrementing the Head/Tail of the FIFO.

- The Transmit Queue (TXQ) is a special transmit FIFO that transmits the messages based on the ID of the messages stored in the queue.

- The Transmit Event FIFO (TEF) stores the message IDs of the transmitted messages.

- A free-running Time Base Counter is used to time stamp received messages. Messages in the TEF can also be time stamped.

- The CAN FD Controller module generates interrupts when new messages are received or when messages were transmitted successfully.

- The SFR are used to control and to read the status of the CAN FD Controller module.

Note 1: This data sheet summarizes the features of the CAN FD Controller module. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP25xxFD Family Reference Manual".

### FIGURE 2-1: CAN FD CONTROLLER MODULE BLOCK DIAGRAM

FIGURE 3-1:

### MCP2518FD

MEMORY MAP

### 3.0 MEMORY ORGANIZATION

Figure 3-1 illustrates the main sections of the memory and its address ranges:

- MCP2518FD Special Function Registers

- CAN FD Controller module SFR

- Message Memory (RAM)

The SFR are 32-bit wide. The LSB is located at the lower address, for example, the LSB of C1CON is located at address  $0 \times 000$ , while its MSB is located at address  $0 \times 003$ .

Table 3-1 lists the MCP2518FD specific registers. The first column contains the address of the SFR.

Table 3-2 lists the registers of the CAN FD Controller module. The first column contains the address of the SFR.

#### MSB LSB Address Address -32 bit-0x003 0x000 MSB LSB CAN FD Controller Module SFR (752 BYTE) 0x2EF 0x2EC 0x2F3 0x2F0 Unimplemented (272 BYTE) 0x3FF 0x3FC 0x403 0X400 RAM (2KBYTE) **OxBFF** 0xBFC 0xC03 0xC00 Unimplemented (512 BYTE) 0xDFF 0xDFC 0xE00 0xE03 MCP2518FD SFR (24 BYTE) 0xE17 0xE14 0xE1B 0xE18 Reserved (488 BYTE) **OxFFF 0xFFC**

### © 2019-2020 Microchip Technology Inc.

| IABLE              | J-1. N       |       |                   | GISTER S          | UNINAN            |                   |                   |                   |                  |                  |

|--------------------|--------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Address            | Name         | )     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| E03                | OSC          | 31:24 | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| E02                |              | 23:16 |                   |                   | -                 | -                 | -                 |                   |                  | _                |

| E01                |              | 15:8  | —                 | —                 | —                 | SCLKRDY           | —                 | OSCRDY            | —                | PLLRDY           |

| E00 <sup>(1)</sup> |              | 7:0   |                   | CLKOE             | DIV[1:0]          | SCLKDIV           | LPMEN             | OSCDIS            |                  | PLLEN            |

|                    | IOCON        | 31:24 | _                 | INTOD             | SOF               | TXCANOD           | —                 | _                 | PM1              | PM0              |

|                    |              | 23:16 | -                 | _                 | —                 | —                 | —                 | _                 | GPIO1            | GPIO0            |

|                    |              | 15:8  | _                 | _                 | —                 | —                 | —                 | _                 | LAT1             | LAT0             |

| E04                |              | 7:0   | -                 | XSTBYEN           | —                 | —                 | —                 | _                 | TRIS1            | TRIS0            |

|                    | CRC          | 31:24 | _                 | _                 | —                 | —                 | —                 | _                 | FERRIE           | CRCERRIE         |

|                    |              | 23:16 | -                 | _                 | —                 | —                 | —                 | _                 | FERRIF           | CRCERRIF         |

|                    |              | 15:8  |                   |                   |                   | CRC               | [15:8]            |                   |                  |                  |

| E08                |              | 7:0   |                   |                   |                   | CRC               | [7:0]             |                   |                  |                  |

|                    | ECCCON       | 31:24 | -                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

|                    |              | 23:16 | _                 | _                 | —                 | —                 | —                 | _                 | —                | —                |

|                    |              | 15:8  | —                 |                   |                   |                   | PARITY[6:0]       |                   |                  |                  |

| E0C                |              | 7:0   | -                 | _                 | —                 | —                 | —                 | DEDIE             | SECIE            | ECCEN            |

|                    | ECCSTAT      | 31:24 | _                 | _                 | —                 | —                 |                   | ERRADI            | DR[11:8]         |                  |

|                    |              | 23:16 |                   |                   |                   | ERRAD             | DR[7:0]           |                   |                  |                  |

|                    |              | 15:8  | _                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

| E10                |              | 7:0   |                   |                   | —                 | —                 | —                 | DEDIF             | SECIF            | —                |

|                    | DEVID        | 31:24 | _                 | _                 | _                 | —                 | —                 | _                 | —                | _                |

|                    |              | 23:16 | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                    |              | 15:8  | -                 | _                 | —                 | —                 | —                 | _                 | _                | —                |

| E14                |              | 7:0   |                   | ID[;              | 3:0]              |                   |                   | REV               | [3:0]            |                  |

|                    | <b>-</b> , , | -     |                   |                   | -                 |                   |                   |                   | [0.0]            |                  |

### TABLE 3-1: MCP2518FD REGISTER SUMMARY

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

2: The bit fields in the IOCON register must be written using single data byte SFR WRITE instructions.

| Addr.             | Name     |              | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-------------------|----------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 03                | C1CON    | 31:24        |                   |                   | /S[3:0]           |                   | ABAT              |                   | REQOP[2:0]       |                  |  |  |

| 02                |          | 23:16        |                   | OPMOD[2:0]        |                   | TXQEN             | STEF              | SERR2LOM          | ESIGM            | RTXAT            |  |  |

| 01                |          | 15:8         | -                 | _                 | -                 | BRSDIS            | BUSY              | WF                | F[1:0]           | WAKFIL           |  |  |

| 00 <sup>[1]</sup> |          | 7:0          | —                 | PXEDIS            | ISOCRCEN          |                   | •                 | DNCNT[4:0]        |                  |                  |  |  |

| C1NBTCFG          | 31:24    |              |                   |                   | BRF               | P[7:0]            |                   |                   |                  |                  |  |  |

|                   | 23:16    |              |                   |                   | TSEG              | 61[7:0]           |                   |                   |                  |                  |  |  |

|                   |          | 15:8         | -                 |                   |                   |                   | TSEG2[6:0]        |                   |                  |                  |  |  |

| 04                |          | 7:0          | —                 |                   |                   |                   | SJW[6:0]          |                   |                  |                  |  |  |

| C1DBTCFG          |          | 31:24        |                   |                   |                   | BRF               | P[7:0]            |                   |                  |                  |  |  |

|                   | 23:16    | —            | —                 | — — TSEG1[4:0]    |                   |                   |                   |                   |                  |                  |  |  |

|                   |          | 15:8         | -                 | _                 | -                 | -                 |                   | TSEG              | 62[3:0]          |                  |  |  |

| 08                |          | 7:0          | —                 | —                 | -                 | -                 |                   | SJW               | /[3:0]           |                  |  |  |

|                   | C1TDC    | 31:24        |                   | —                 | _                 | _                 | —                 | _                 | EDGFLTEN         | SID11EN          |  |  |

|                   |          | 23:16        | -                 | —                 | -                 | -                 | —                 | -                 | TDCMC            | DD[1:0]          |  |  |

|                   |          | 15:8         | -                 |                   |                   |                   | TDCO[6:0]         |                   |                  |                  |  |  |

| 0C                |          | 7:0          |                   | _                 |                   |                   | TDC               | V[5:0]            |                  |                  |  |  |

| C1TBC             | 31:24    |              |                   |                   | TBC[              | 31:24]            |                   |                   |                  |                  |  |  |

|                   |          | 23:16        |                   | TBC[23:16]        |                   |                   |                   |                   |                  |                  |  |  |

|                   |          | 15:8         |                   | TBC[15:8]         |                   |                   |                   |                   |                  |                  |  |  |

| 10                |          | 7:0          |                   |                   |                   | TBC               | C[7:0]            |                   |                  |                  |  |  |

| C1TSCON           | C1TSCON  | 31:24        | _                 | —                 |                   | _                 | —                 | _                 |                  | —                |  |  |

|                   |          | 23:16        | -                 | —                 | -                 | -                 | —                 | TSRES             | TSEOF            | TBCEN            |  |  |

|                   |          | 15:8         | _                 | —                 | _                 | _                 | —                 | _                 | TBCPF            | RE[9:8]          |  |  |

| 14                |          | 7:0          | TBCPRE[7:0]       |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   | C1VEC    | 31:24        | - RXCODE[6:0]     |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   |          | 23:16        | —                 |                   |                   |                   | TXCODE[6:0]       |                   |                  |                  |  |  |

|                   |          | 15:8         | -                 |                   |                   |                   |                   |                   |                  |                  |  |  |

| 18                |          | 7:0          | - ICODE[6:0]      |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   | C1INT    | 31:24        | IVMIE             | WAKIE             | CERRIE            | SERRIE            | RXOVIE            | TXATIE            | SPICRCIE         | ECCIE            |  |  |

|                   |          | 23:16        | —                 | —                 | _                 | TEFIE             | MODIE             | TBCIE             | RXIE             | TXIE             |  |  |

|                   |          | 15:8         | IVMIF             | WAKIF             | CERRIF            | SERRIF            | RXOVIF            | TXATIF            | SPICRCIF         | ECCIF            |  |  |

| 1C                |          | 7:0          | —                 | —                 |                   | TEFIF             | MODIF             | TBCIF             | RXIF             | TXIF             |  |  |

| C1RXIF            | 31:24    |              | RFIF[31:24]       |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   |          | 23:16        |                   | RFIF[23:16]       |                   |                   |                   |                   |                  |                  |  |  |

|                   |          | 15:8         |                   |                   |                   |                   | [15:8]            |                   |                  |                  |  |  |

| 20<br>C1TXIF      | 7:0      |              | RFIF[7:1] —       |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   | C1TXIF   | 31:24        |                   |                   |                   |                   | 31:24]            |                   |                  |                  |  |  |

|                   |          | 23:16        | TFIF[23:16]       |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   |          | 15:8         |                   |                   |                   | TFIF              | [15:8]            |                   |                  |                  |  |  |

| 24                |          | 7:0          | TFIF[7:0]         |                   |                   |                   |                   |                   |                  |                  |  |  |

|                   | C1RXOVIF | 31:24        |                   |                   |                   |                   | F[31:24]          |                   |                  |                  |  |  |

|                   |          | 23:16        |                   |                   |                   | RFOVI             | F[23:16]          |                   |                  |                  |  |  |

|                   |          | 15:8         |                   |                   |                   |                   | IF[15:8]          |                   |                  |                  |  |  |

|                   |          |              |                   |                   |                   |                   |                   |                   |                  | _                |  |  |

| 28                |          | 7:0          |                   | RFOVIF[7:1] —     |                   |                   |                   |                   |                  |                  |  |  |

| 28                | C1TXATIF | 7:0<br>31:24 |                   |                   |                   |                   | [31:24]           |                   |                  |                  |  |  |

| 28                | C1TXATIF |              |                   |                   |                   | TFATIF<br>TFATIF  | [23:16]           |                   |                  |                  |  |  |

| 28                | C1TXATIF | 31:24        |                   |                   |                   | TFATIF<br>TFATIF  |                   |                   |                  |                  |  |  |

|  | TABLE 3-2: | CAN FD CONTROLLER MODULE REGISTER SUMMARY |

|--|------------|-------------------------------------------|

|--|------------|-------------------------------------------|

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| Addr.    | Name                    |             | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|----------|-------------------------|-------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

|          | C1TXREQ                 | 31:24       |                   |                   |                   | TXREC             | 2[31:24]          |                   | •                |                  |  |  |  |

|          |                         | 23:16       |                   |                   |                   | TXREC             | Q[23:16]          |                   |                  |                  |  |  |  |

|          |                         | 15:8        |                   |                   |                   | TXRE              | Q[15:8]           |                   |                  |                  |  |  |  |

| 30       |                         | 7:0         |                   |                   |                   | TXRE              | Q[7:0]            |                   |                  |                  |  |  |  |

|          | C1TREC                  | 31:24       | —                 | _                 | —                 | _                 | —                 | —                 | —                |                  |  |  |  |

|          |                         | 23:16       | —                 |                   | TXBO              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |  |  |  |

|          |                         | 15:8        |                   |                   |                   | TEC               | [7:0]             |                   |                  |                  |  |  |  |

| 34       |                         | 7:0         |                   |                   |                   |                   | [7:0]             |                   |                  |                  |  |  |  |

| C1BDIAG0 | C1BDIAG0                | 31:24       |                   | DTERRCNT[7:0]     |                   |                   |                   |                   |                  |                  |  |  |  |

|          |                         | 23:16       |                   |                   |                   |                   | CNT[7:0]          |                   |                  |                  |  |  |  |

|          |                         | 15:8        |                   |                   |                   |                   | CNT[7:0]          |                   |                  |                  |  |  |  |

| 38       |                         | 7:0         |                   |                   |                   | NRERR             | CNT[7:0]          |                   |                  |                  |  |  |  |

|          | C1BDIAG1                | 31:24       | DLCMM             | ESI               | DCRCERR           |                   | DFORMERR          | _                 | DBIT1ERR         | DBIT0ERR         |  |  |  |

|          |                         | 23:16       | TXBOERR           | _                 | NCRCERR           | NSTUFERR          |                   | NACKERR           | NBIT1ERR         | NBIT0ERR         |  |  |  |

|          |                         | 15:8<br>7:0 |                   |                   |                   |                   | CNT[15:8]         |                   |                  |                  |  |  |  |

| 3C       | 3C                      |             |                   | EFMSGCNT[7:0]     |                   |                   |                   |                   |                  |                  |  |  |  |

|          | C1TEFCON                | 31:24       | —                 | _                 | —                 |                   |                   | FSIZE[4:0]        |                  |                  |  |  |  |

|          |                         | 23:16       | —                 |                   | -                 | _                 | —                 | _                 | —                | —                |  |  |  |

|          |                         | 15:8        | —                 | _                 | —                 | _                 | —                 | FRESET            | —                | UINC             |  |  |  |

| 40       |                         | 7:0         | —                 | —                 | TEFTSEN           | _                 | TEFOVIE           | TEFFIE            | TEFHIE           | TEFNEIE          |  |  |  |

|          | C1TEFSTA                | 31:24       | —                 | _                 | —                 | _                 | —                 | _                 | —                | _                |  |  |  |

|          |                         | 23:16       | —                 | _                 | —                 | _                 | _                 | _                 | _                | _                |  |  |  |

|          |                         | 15:8        | —                 | _                 | —                 | _                 | _                 | _                 | —                | _                |  |  |  |

| 44       |                         | 7:0         | —                 | _                 | —                 | —                 | TEFOVIF           | TEFFIF            | TEFHIF           | TEFNEIF          |  |  |  |

|          | C1TEFUA                 | 31:24       | TEFUA[31:24]      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|          |                         | 23:16       |                   |                   |                   |                   | [23:16]           |                   |                  |                  |  |  |  |

|          |                         | 15:8        |                   |                   |                   |                   | A[15:8]           |                   |                  |                  |  |  |  |

| 48       |                         | 7:0         |                   |                   |                   |                   | IA[7:0]           |                   |                  |                  |  |  |  |

|          | Reserved <sup>(2)</sup> | 31:24       |                   |                   |                   |                   | ed[31:24]         |                   |                  |                  |  |  |  |

|          |                         | 23:16       |                   |                   |                   |                   | ed[23:16]         |                   |                  |                  |  |  |  |

|          |                         | 15:8        |                   |                   |                   |                   | ed[15:8]          |                   |                  |                  |  |  |  |

| 4C       |                         | 7:0         | Reserved[7:0]     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|          | C1TXQCON                | 31:24       |                   | PLSIZE[2:0]       |                   |                   |                   | FSIZE[4:0]        |                  |                  |  |  |  |

|          |                         | 23:16       | _                 | TXAT              | [1:0]             |                   |                   | TXPRI[4:0]        | 1                | 1                |  |  |  |

|          |                         | 15:8        | —                 | _                 | -                 | _                 | —                 | FRESET            | TXREQ            | UINC             |  |  |  |

| 50       |                         | 7:0         | TXEN              | _                 | —                 | TXATIE            | —                 | TXQEIE            | _                | TXQNIE           |  |  |  |

|          | C1TXQSTA                | 31:24       | —                 | —                 | —                 |                   | —                 | _                 | —                |                  |  |  |  |

|          |                         | 23:16       | —                 | _                 | -                 | —                 | —                 | _                 | —                | —                |  |  |  |

|          |                         | 15:8        | _                 | _                 | —                 |                   |                   | TXQCI[4:0]        |                  | 1                |  |  |  |

| 54       |                         | 7:0         | TXABT             | TXLARB            | TXERR             | TXATIF            |                   | TXQEIF            |                  | TXQNIF           |  |  |  |

|          | C1TXQUA                 | 31:24       |                   |                   |                   |                   | \[31:24]          |                   |                  |                  |  |  |  |

|          |                         | 23:16       |                   |                   |                   |                   | A[23:16]          |                   |                  |                  |  |  |  |

|          |                         | 15:8        |                   |                   |                   |                   | A[15:8]           |                   |                  |                  |  |  |  |

| 58       |                         | 7:0         |                   |                   |                   | TXQL              | JA[7:0]           |                   |                  |                  |  |  |  |

### TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| 5C<br>60<br>64<br>68<br>62<br>70<br>74<br>78<br>72<br>80                                      | C1FIFOCON1<br>C1FIFOSTA1<br>C1FIFOUA1<br>C1FIFOCON2<br>C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOCON3<br>C1FIFOCON3<br>C1FIFOSTA3 | 31:24           23:16           15:8           7:0           31:24           23:16           15:8           7:0           31:24           23:16           15:8           7:0           31:24           23:16           15:8           7:0           31:24           23:16           15:8           7:0           31:0           31:0           31:0 | <br>TXEN<br><br><br>TXABT                      | PLSIZE[2:0]<br>TXAT<br>—<br>RTREN<br>—<br>—<br>—<br>TXLARB | [1:0]<br>—<br>RXTSEN<br>—<br>—<br>—<br>TXERR | TXATIE<br>—<br>TXATIF<br>FIFOU | RXOVIE                 | FSIZE[4:0]<br>TXPRI[4:0]<br>FRESET<br>TFERFFIE<br>—<br>FIFOCI[4:0] | TXREQ<br>TFHRFHIE<br>— | UINC<br>TFNRFNIE<br>—<br>— |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------|----------------------------------------------|--------------------------------|------------------------|--------------------------------------------------------------------|------------------------|----------------------------|

| 60<br>64<br>68<br>6C<br>70<br>74<br>78<br>7C<br>80                                            | C1FIFOUA1<br>C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                          | 15:8<br>7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:0<br>31:0<br>31:0                                                                                                                                                                                                                                               |                                                | RTREN                                                      | RXTSEN                                       | —<br>—<br>TXATIF               |                        | FRESET<br>TFERFFIE<br>—<br>FIFOCI[4:0]                             | TFHRFHIE<br>—<br>—     |                            |

| 60<br>64<br>68<br>6C<br>70<br>74<br>78<br>72<br>80                                            | C1FIFOUA1<br>C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                          | 7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                               | TXEN                                           | RTREN<br>—<br>—<br>—                                       |                                              | —<br>—<br>TXATIF               |                        | TFERFFIE<br>—<br>—<br>FIFOCI[4:0]                                  | TFHRFHIE<br>—<br>—     |                            |

| 60<br>64<br>68<br>6C<br>70<br>74<br>78<br>7C<br>80                                            | C1FIFOUA1<br>C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                          | 31:24<br>23:16<br>15:8<br>7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                      |                                                |                                                            |                                              | —<br>—<br>TXATIF               |                        | —<br>—<br>FIFOCI[4:0]                                              |                        | TFNRFNIE<br>—<br>—         |

| 60<br>64<br>68<br>6C<br>70<br>74<br>78<br>72<br>80                                            | C1FIFOUA1<br>C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                          | 23:16<br>15:8<br>7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                               | —<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>— | —<br>—<br>TXLARB                                           | —<br>—<br>TXERR                              |                                | <br><br>RXOVIF         |                                                                    | _                      | _                          |

| 64           68           6C           70           74           78           7C           80 | C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                       | 15:8         7:0         31:24         23:16         15:8         7:0         31:0         31:0                                                                                                                                                                                                                                                     | —<br>TXABT                                     | —<br>—<br>TXLARB                                           | —<br>—<br>TXERR                              |                                | —<br>RXOVIF            |                                                                    | —                      | —                          |

| 64           68           6C           70           74           78           7C           80 | C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                       | 7:0<br>31:24<br>23:16<br>15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                                                | TXABT                                          | —<br>TXLARB                                                | —<br>TXERR                                   |                                | RXOVIF                 |                                                                    | Γ                      |                            |

| 64<br>68<br>6C<br>70<br>74<br>78<br>7C<br>80                                                  | C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                       | 31:24<br>23:16<br>15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                                                       | TXABT                                          | TXLARB                                                     | TXERR                                        |                                | RXOVIF                 | TEEDEELE                                                           |                        |                            |

| 68       6C       70       74       78       7C       80                                      | C1FIFOCON2<br>C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                       | 23:16<br>15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | FIFOU                          |                        | TFERFFIF                                                           | TFHRFHIF               | TFNRFNIF                   |

| 68       6C       70       74       78       7C       80                                      | C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                                     | 15:8<br>7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                                                                         |                                                |                                                            |                                              |                                | A[31:24]               |                                                                    |                        |                            |

| 68       6C       70       74       78       7C       80                                      | C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                                     | 7:0<br>31:0<br>31:0                                                                                                                                                                                                                                                                                                                                 |                                                |                                                            |                                              | FIFOU                          | A[23:16]               |                                                                    |                        |                            |

| 68       6C       70       74       78       7C       80                                      | C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                                     | 31:0<br>31:0                                                                                                                                                                                                                                                                                                                                        |                                                |                                                            |                                              | FIFOU                          | A[15:8]                |                                                                    |                        |                            |

| 6C<br>70<br>74<br>78<br>7C<br>80                                                              | C1FIFOSTA2<br>C1FIFOUA2<br>C1FIFOCON3                                                                                     | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | FIFOL                          | JA[7:0]                |                                                                    |                        |                            |

| 70       74       78       7C       80                                                        | C1FIFOUA2<br>C1FIFOCON3                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     |                                                |                                                            |                                              | same as C                      | IFIFOCON1              |                                                                    |                        |                            |

| 74<br>78<br>7C<br>80                                                                          | C1FIFOCON3                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | same as C                      | 1FIFOSTA1              |                                                                    |                        |                            |

| 78<br>7C<br>80                                                                                |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                     |                                                |                                                            |                                              | same as C                      | 1FIFOUA1               |                                                                    |                        |                            |

| 7C<br>80                                                                                      | C1FIFOSTA3                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | same as C                      | IFIFOCON1              |                                                                    |                        |                            |

| 80                                                                                            |                                                                                                                           | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | same as C                      | 1FIFOSTA1              |                                                                    |                        |                            |

|                                                                                               | C1FIFOUA3                                                                                                                 | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | same as C                      | 1FIFOUA1               |                                                                    |                        |                            |

| 84                                                                                            | C1FIFOCON4                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOCON1                                         |                                              |                                |                        |                                                                    |                        |                            |

| ÷ .                                                                                           | C1FIFOSTA4                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOSTA1                                         |                                              |                                |                        |                                                                    |                        |                            |

| 88                                                                                            | C1FIFOUA4                                                                                                                 | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOUA1                                          |                                              |                                |                        |                                                                    |                        |                            |

| 8C                                                                                            | C1FIFOCON5                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOCON1                                         |                                              |                                |                        |                                                                    |                        |                            |

| 90                                                                                            | C1FIFOSTA5                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOSTA1                                         |                                              |                                |                        |                                                                    |                        |                            |

| 94                                                                                            | C1FIFOUA5                                                                                                                 | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOUA1                                          |                                              |                                |                        |                                                                    |                        |                            |

| 98                                                                                            | C1FIFOCON6                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOCON1                                         |                                              |                                |                        |                                                                    |                        |                            |

|                                                                                               | C1FIFOSTA6                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                | same as C1FIFOSTA1                             |                                                            |                                              |                                |                        |                                                                    |                        |                            |

| A0                                                                                            | C1FIFOUA6                                                                                                                 | 31:0                                                                                                                                                                                                                                                                                                                                                | same as C1FIFOUA1                              |                                                            |                                              |                                |                        |                                                                    |                        |                            |

|                                                                                               | C1FIFOCON7                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                | same as C1FIFOCON1                             |                                                            |                                              |                                |                        |                                                                    |                        |                            |

|                                                                                               | C1FIFOSTA7                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              |                                | 1FIFOSTA1              |                                                                    |                        |                            |

| AC                                                                                            | C1FIFOUA7                                                                                                                 | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              |                                | 1FIFOUA1               |                                                                    |                        |                            |

|                                                                                               | C1FIFOCON8                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              |                                | IFIFOCON1              |                                                                    |                        |                            |

|                                                                                               | C1FIFOSTA8                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              |                                | 1FIFOSTA1              |                                                                    |                        |                            |

| B8                                                                                            | C1FIFOUA8                                                                                                                 | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              |                                | IFIFOUA1               |                                                                    |                        |                            |

|                                                                                               | C1FIFOCON9                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                | same as C1FIFOCON1<br>same as C1FIFOSTA1                   |                                              |                                |                        |                                                                    |                        |                            |

|                                                                                               | C1FIFOSTA9                                                                                                                | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              | -                              | -                      |                                                                    |                        |                            |

| C4                                                                                            | C1FIFOUA9<br>C1FIFOCON10                                                                                                  | 31:0                                                                                                                                                                                                                                                                                                                                                |                                                |                                                            |                                              |                                |                        |                                                                    |                        |                            |

|                                                                                               |                                                                                                                           | 31:0<br>31:0                                                                                                                                                                                                                                                                                                                                        |                                                | same as C1FIFOCON1<br>same as C1FIFOSTA1                   |                                              |                                |                        |                                                                    |                        |                            |