# PL602-21SI-R Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number PL602-21SI-R-DG

Manufacturer Microchip Technology

Manufacturer Product Number PL602-21SI-R

Description IC CLK BUFFER 100MHZ 8SOIC

Detailed Description IC 100MHz 1 8-SOIC (0.154", 3.90mm Width)

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# **Purchase and inquiry**

| Manufacturer Product Number:   | Manufacturer:            |

|--------------------------------|--------------------------|

| PL602-21SI-R                   | Microchip Technology     |

| Series:                        | Product Status:          |

|                                | Active                   |

| DiGi-Electronics Programmable: | PLL:                     |

| Not Verified                   | Yes                      |

| Input:                         | Output:                  |

| Crystal                        | LVCMOS                   |

| Number of Circuits:            | Ratio - Input:Output:    |

| 1                              | -1:1                     |

| Differential - Input:Output:   | Frequency - Max:         |

| No/Yes                         | 100MHz                   |

| Divider/Multiplier:            | Voltage - Supply:        |

| No/No                          | 2.25V ~ 3.63V            |

| Operating Temperature:         | Mounting Type:           |

| -40°C ~ 85°C                   | Surface Mount            |

| Package / Case:                | Supplier Device Package: |

| 8-SOIC (0.154", 3.90mm Width)  | 8-SOP                    |

| Base Product Number:           |                          |

| PL602                          |                          |

# **Environmental & Export classification**

8542.39.0001

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 3 (168 Hours)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

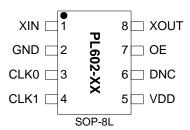

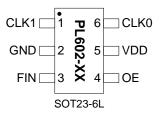

# HCSL Compatible Clock Generator for PCI Express PIN CONFIGURATION

### FEATURES

- Input Frequency:

- Fundamental Crystal or Reference Input: 25MHz

- Output Frequency:

- o PL602-21: 100MHz differential outputs.

- o PL602-22: 125MHz differential outputs.

- o PL602-23: 200MHz differential outputs.

- PL602-26: 25MHz differential outputs.

- o PL602-27: 250MHz differential outputs.

- o PL602-15: 156.25 MHz differential outputs.

- Very low Jitter: 28ps Pk-Pk typ.

- Very low Phase Noise:

- o -130 dBc at 10kHz offset at 100MHz

- No external loop filter is required

- Power supply range: 2.25V to 3.63V

- Operating temperature range from -40°C to 85°C

- Available in 6-pin SOT or 8-pin SOP Green/RoHS compliant package.

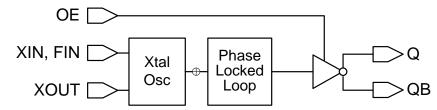

#### **DESCRIPTION**

The PL602-XX is the smallest, high performance, lowest power differential output clock IC available for HCSL timing applications. PL602-XX offers -130dBc at 10kHz offset at 100MHz, with a very low jitter (2 ps TIE RMS), making it ideal for HCSL applications requiring small size and low power.

#### **BLOCK DIAGRAM**

#### PIN DESCRIPTION

| Nome     | Pi  | n #   | Turna | Description                                                              |  |

|----------|-----|-------|-------|--------------------------------------------------------------------------|--|

| Name     | SOP | SOT23 | Type  |                                                                          |  |

| XIN      | 1   | -     | I     | Crystal input (SOP package only)                                         |  |

| FIN      | -   | 3     | I     | Reference clock input (SOT23 package only)                               |  |

| GND      | 2   | 2     | Р     | GND connection                                                           |  |

| CLK[0:1] | 3,4 | 1,6   | 0     | Differential clock outputs [note:CLK0=~CLK1]                             |  |

| VDD      | 5   | 5     | Р     | VDD connection                                                           |  |

| DNC      | 6   | -     | -     | Do not connect                                                           |  |

| OE       | 7   | 4     | I     | Output enable (OE) input. Internal $60 \text{K}\Omega$ pull up resistor. |  |

| XOUT     | 8   | -     | 0     | Crystal output pin.                                                      |  |

### **HCSL Compatible Clock Generator for PCI Express**

### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETERS                     | SYMBOL   | MIN. | MAX.                 | UNITS |

|--------------------------------|----------|------|----------------------|-------|

| Supply Voltage Range           | $V_{DD}$ | -0.5 | 4.6                  | V     |

| Input Voltage Range            | Vı       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage Range           | Vo       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Soldering Temperature          |          |      | 260                  | °C    |

| Storage Temperature            | Ts       | -65  | 150                  | °C    |

| Ambient Operating Temperature* |          | -40  | +85                  | °C    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied. \*Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

#### **AC SPECIFICATIONS**

| PARAMETERS                                | CONDITIONS                                                                                 | MIN. | TYP. | MAX.     | UNITS |

|-------------------------------------------|--------------------------------------------------------------------------------------------|------|------|----------|-------|

| Crystal Input Frequency                   | Fundamental Crystal                                                                        |      | 25   |          | MHz   |

| Input (F <sub>IN</sub> ) Frequency        |                                                                                            |      | 25   |          | MHz   |

| Input (F <sub>IN</sub> ) Signal Amplitude | Internally AC coupled                                                                      | 0.9  |      | $V_{DD}$ | Vpp   |

| Output Frequency                          |                                                                                            | 25   |      | 200      | MHz   |

| Output Enable Time                        | OE Function; Ta=25° C, Add one clock period to this measurement for a usable clock output. |      |      | 10       | ns    |

| Output Disable Time                       | OE Function; Ta=25° C                                                                      |      |      | 10       | ns    |

| Settling Time                             | At power-up $(V_{DD} \ge 2.25V)$                                                           |      |      | 10       | ms    |

| VDD Sensitivity                           | Frequency vs. V <sub>DD</sub> , ±10%                                                       | -2   |      | 2        | ppm   |

| Output Rise Time                          | 10/90%V <sub>он</sub>                                                                      |      | 0.3  | 0.5      | ns    |

| Output Fall Time                          | 90/10%V <sub>он</sub>                                                                      |      | 0.3  | 0.5      | ns    |

| Skew Between Outputs                      | Measured at 50% V <sub>OH</sub>                                                            |      |      | 250      | ps    |

| Duty Cycle                                | At V <sub>DD</sub> /2                                                                      | 45   | 50   | 55       | %     |

| Period Jitter, peak-to-peak               | With canacitive descupling between V                                                       |      | 28   |          | ps    |

| Cycle-to-Cycle, RMS                       | - With capacitive decoupling between V <sub>DD</sub> and GND                               |      | 9    |          | ps    |

| Cycle-to-Cycle, peak                      | - At 100MHz                                                                                |      | 25   |          | ps    |

| TIE, RMS                                  | - 20,000 samples measured                                                                  |      | 2    |          | ps    |

# **HCSL Compatible Clock Generator for PCI Express**

### **DC SPECIFICATIONS**

| PARAMETERS              | SYMBOL           | CONDITIONS                               | MIN. | TYP. | MAX. | UNITS |

|-------------------------|------------------|------------------------------------------|------|------|------|-------|

| Supply Current, Dynamic | I <sub>DD</sub>  | At 100MHz, No Load                       |      | 25   |      | mA    |

| Operating Voltage       | $V_{DD}$         |                                          | 2.25 |      | 3.63 | V     |

| Output Low Voltage      | V <sub>OL</sub>  | HCSL termination,                        |      |      | 0.05 | V     |

| Output High Voltage     | V <sub>OH</sub>  | $(RS = 150\Omega, RT = 49.9\Omega) 3.3V$ | 0.65 | 0.75 | 0.85 | V     |

| Output Current          | I <sub>OSD</sub> | $(RS = 100\Omega, RT = 49.9\Omega) 2.5V$ | 13   | 15   | 17   | mA    |

### **CRYSTAL SPECIFICATIONS**

| PARAMETERS                               | SYMBOL                | MIN. | TYP. | MAX. | UNITS |

|------------------------------------------|-----------------------|------|------|------|-------|

| Fundamental Crystal Resonator Frequency  | F <sub>XIN</sub>      |      | 25   |      | MHz   |

| Crystal Loading Rating                   | C <sub>L (xtal)</sub> |      | 18   |      | pF    |

| Maximum Sustainable Drive Level          |                       |      |      | 500  | μW    |

| Operating Drive Level                    |                       |      | 100  |      | μW    |

| Crystal Shunt Capacitance                | C0                    |      |      | 6    | pF    |

| Effective Series Resistance, Fundamental | ESR                   |      |      | 45   | Ω     |

### **HCSL Compatible Clock Generator for PCI Express**

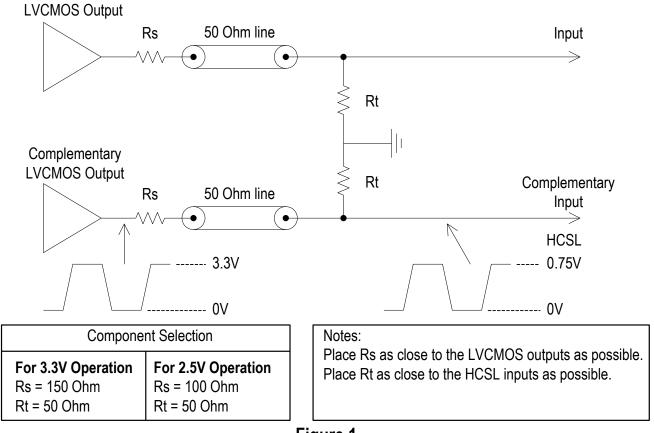

#### PCI EXPRESS/HCSL COMPATIBLE LAYOUT GUIDELINES

Figure 1 below describes how to terminate the complementary LVCMOS outputs of PL602-XX for use with HCSL inputs.

Figure 1

#### PCB LAYOUT CONSIDERATIONS FOR PERFORMANCE OPTIMIZATION

The following guidelines are to assist you with a performance optimized PCB design:

- Keep all the PCB traces to PL602-XX as short as possible, as well as keeping all other traces as far away from it as possible.

- Place the crystal as close as possible to both crystal pins of the device. This will reduce the cross-talk between the crystal and the other signals.

- Separate crystal pin traces from the other signals on the PCB, but allow ample distance between the two crystal pin traces.

- Place a 0.01µF~0.1µF decoupling capacitor between VDD and GND, on the component side of the PCB, close to the VDD pin. It is not recommended to place this component on the backside of the PCB.

- It is highly recommended to keep the VDD and GND traces as short as possible.

- When connecting long traces (> 1 inch) to a CMOS output, it is important to design the traces as a transmission line or 'stripline', to avoid reflections or ringing. In this case, the CMOS output needs to be matched to the trace impedance. Usually 'striplines' are designed for  $50\Omega$  impedance and CMOS outputs usually have lower than  $50\Omega$  impedance so matching can be achieved by adding a resistor in series with the CMOS output pin to the 'stripline' trace.

# **HCSL Compatible Clock Generator for PCI Express**

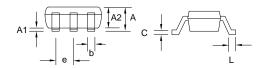

### PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

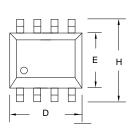

#### SOP-8L

| Symbol   | Dimension in MM |      |  |

|----------|-----------------|------|--|

| Syllibol | Min.            | Max. |  |

| Α        | 1.35            | 1.75 |  |

| A1       | 0.10            | 0.25 |  |

| A2       | 1.25            | 1.50 |  |

| В        | 0.33            | 0.53 |  |

| С        | 0.19            | 0.27 |  |

| D        | 4.80            | 5.00 |  |

| Е        | 3.80            | 4.00 |  |

| Н        | 5.80            | 6.20 |  |

| L        | 0.40            | 0.89 |  |

| е        | 1.27 BSC        |      |  |

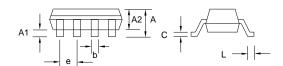

#### SOT23-6L

| Cymphol | Dimensi  | on in MM |  |

|---------|----------|----------|--|

| Symbol  | Min.     | Max.     |  |

| Α       | 1.05     | 1.35     |  |

| A1      | 0.05     | 0.15     |  |

| A2      | 1.00     | 1.20     |  |

| В       | 0.30     | 0.50     |  |

| С       | 0.08     | 0.20     |  |

| D       | 2.80     | 3.00     |  |

| E       | 1.50     | 1.70     |  |

| Н       | 2.60     | 3.0      |  |

| L       | 0.35     | 0.55     |  |

| е       | 0.95 BSC |          |  |

### **HCSL Compatible Clock Generator for PCI Express**

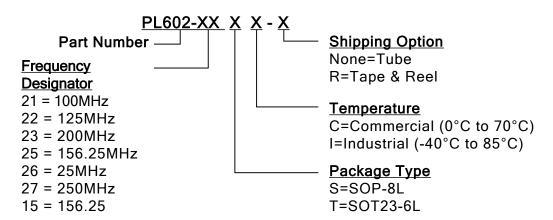

### ORDERING INFORMATION (GREEN PACKAGE COMPLIANT)

### For part ordering, please contact our Sales Department:

2180 Fortune Drive, San Jose, CA 95131, USA Tel: (408) 944-0800 Fax: (408) 474-1000

#### PART NUMBER

The order number for this device is a combination of the following: Part number, Package type and Operating temperature range

| Part / Order Number | Marking     | Package Option               |

|---------------------|-------------|------------------------------|

| PL602-2XSC          | P602-2X     | 8-Pin SOP (Tube)             |

| PL602-2XSC-R        | SC<br>LLLLL | 8-Pin SOP (Tape and Reel)    |

| PL602-1XTC-R        | F1X<br>LLL  | 6-Pin SOT-23 (Tape and Reel) |

| PL602-2XTC-R        | F2X<br>LLL  | 6-Pin SOT-23 (Tape and Reel) |

Note: LLL / LLLLL designate Production Lot.

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.

### **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com