# SY75576LKY Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number SY75576LKY-DG

Manufacturer Microchip Technology

Manufacturer Product Number SY75576LKY

Description IC CLK BUFFER 2:4 267MHZ 20TSSOP

Detailed Description Clock Fanout Buffer (Distribution), Multiplexer IC 2:

4 267 MHz 20-TSSOP (0.173", 4.40mm Width)

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# **Purchase and inquiry**

| Manufacturer Product Number:              | Manufacturer:                |

|-------------------------------------------|------------------------------|

| SY75576LKY                                | Microchip Technology         |

| Series:                                   | Product Status:              |

| Precision Edge®                           | Active                       |

| Type:                                     | Number of Circuits:          |

| Fanout Buffer (Distribution), Multiplexer | 1                            |

| Ratio - Input:Output:                     | Differential - Input:Output: |

| 2:4                                       | Yes/Yes                      |

| Input:                                    | Output:                      |

| HCSL, LVDS                                | HCSL, LVDS                   |

| Frequency - Max:                          | Voltage - Supply:            |

| 267 MHz                                   | 3.135V ~ 3.465V              |

| Operating Temperature:                    | Mounting Type:               |

| -40°C ~ 85°C                              | Surface Mount                |

| Package / Case:                           | Supplier Device Package:     |

| 20-TSSOP (0.173", 4.40mm Width)           | 20-TSSOP                     |

| Base Product Number:                      |                              |

| SY75576                                   |                              |

# **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |  |

|------------------|-----------------------------------|--|

| ROHS3 Compliant  | 1 (Unlimited)                     |  |

| REACH Status:    | ECCN:                             |  |

| REACH Unaffected | EAR99                             |  |

| HTSUS:           |                                   |  |

| 8542.39.0001     |                                   |  |

#### SY75576L

#### 267MHz 1:4 3.3V HCSL/LVDS Fanout Buffer

#### PrecisionEdge™

#### **General Description**

The SY75576L is a high-speed, fully differential 1:4 clock fanout buffer optimized to provide four identical output copies with 137fs phase jitter and maximum 50ps output-to-output skew. Designed to be used with PCI-Express applications, SY75576L accepts and outputs HCSL or LVDS logic levels.

The SY75576L operates from a 3.3V  $\pm 5\%$  power supply and is guaranteed over the full industrial temperature range (-40°C to +85°C). It is available in a 20-pin TSSOP lead-free package.

The SY75576L is part of Micrel's high-speed, ultra-low jitter, PrecisionEdge™ product line.

Datasheets and support documentation are available on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

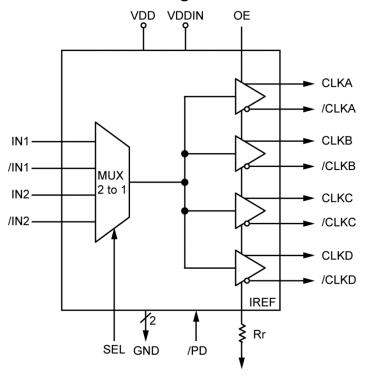

#### **Functional Block Diagram**

#### **Features**

- · Four differential pairs of LVDS or HCSL outputs

- Two pairs of differential inputs accept LVDS or HCSL logic levels

- 267MHz max HCSL frequency

- 100MHz max LVDS frequency

- Ultra low phase jitter:

- 137fs<sub>rms</sub>, 200MHz (12kHz–20MHz)

- 153fs<sub>rms</sub>, 156.25MHz (12kHz-20MHz)

- 212fs<sub>rms</sub>, 100MHz (12kHz-20MHz)

- <2ps Total\_Jitter<sub>pk-pk</sub>, 200MHz (BER = 10<sup>-12</sup>)

- 50ps output-to-output skew

- 3.3V ±5% power supply operation

- -40°C to +85°C operating temperature

- Available in 20-pin TSSOP lead-free package

#### **Applications**

- · Clock distribution

- PCI-Express

- Servers

- Switches

- Routers

Precision Edge is a registered trademark of Micrel, Inc.

# Ordering Information<sup>(1)</sup>

| Part Number                  | Package Type | Operating Range | Package Marking                           | Lead Finish |

|------------------------------|--------------|-----------------|-------------------------------------------|-------------|

| SY75576LKY                   | TSSOP-20     | Industrial      | 75576L<br>with Pb-Free bar-line indicator | Matte-Sn    |

| SY75576LKY TR <sup>(2)</sup> | TSSOP-20     | Industrial      | 75576L<br>with Pb-Free bar-line indicator | Matte-Sn    |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A$  = 25°C, DC Electricals only.

- 2. Tape and Reel.

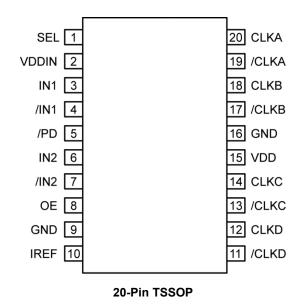

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                  |  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | SEL      | SEL = 0 propagates IN2, /IN2 to outputs. SEL = 1 propagates IN1, /IN1 to outputs. Internal put up resistor, IN1, /IN1 is selected by default. |  |

| 2          | VDDIN    | 3.3V power supply                                                                                                                             |  |

| 3          | IN1      | HCSL/LVDS input 1                                                                                                                             |  |

| 4          | /IN1     | HCSL/LVDS inverted input 1                                                                                                                    |  |

| 5          | /PD      | PD = 0 powers down the chip and tri-states outputs. The pin is attached to an internal pull-up resistor.                                      |  |

| 6          | IN2      | HCSL/LVDS input 2                                                                                                                             |  |

| 7          | /IN2     | HCSL/LVDS inverted input 2                                                                                                                    |  |

| 8          | OE       | Tri-state outputs. High = enable outputs. Low = disable outputs. Internal pull-up resistor, out are enabled by default.                       |  |

| 9          | GND      | Ground                                                                                                                                        |  |

| 10         | IREF     | External resistor Rref between pin IREF and GND controls reference current                                                                    |  |

| 11         | /CLKD    | Inverted output D                                                                                                                             |  |

| 12         | CLKD     | Non-inverted output D                                                                                                                         |  |

| 13         | /CLKC    | Inverted output C                                                                                                                             |  |

| 14         | CLKC     | Non-inverted output C                                                                                                                         |  |

| 15         | VDD      | 3.3V power supply                                                                                                                             |  |

| 16         | GND      | Ground                                                                                                                                        |  |

| 17         | /CLKB    | Inverted output B                                                                                                                             |  |

| 18         | CLKB     | Non-inverted output B                                                                                                                         |  |

| 19         | /CLKA    | Inverted output A                                                                                                                             |  |

| 20         | CLKA     | Non-inverted output A                                                                                                                         |  |

# **Clock Input Function Table**

| SEL | Input Pair |

|-----|------------|

| 0   | IN2/IN2    |

| 1   | IN1/IN1    |

# Absolute Maximum Ratings<sup>(3)</sup>

| Supply Voltage (V <sub>DD</sub> , V <sub>DDIN</sub> ) | 5.5V                         |

|-------------------------------------------------------|------------------------------|

| Input Voltage (V <sub>IN</sub> )                      | $-0.5V$ to $V_{DDIN} + 0.5V$ |

| Lead Temperature (soldering, 20s)                     | 260°C                        |

| Maximum Junction Temperature                          | 125°C                        |

| Storage Temperature (T <sub>s</sub> )                 | 65°C to +150°C               |

| ESD Protection (input)                                | 2000V min.                   |

# Operating Ratings<sup>(4)</sup>

| Supply Voltage (V <sub>DD</sub> , V <sub>DDIN</sub> ) | 3.135V to 3.465V |

|-------------------------------------------------------|------------------|

| Ambient Op Temperature (T <sub>A</sub> )              | 40°C to +85°C    |

| Package Thermal Resistance <sup>(5)</sup>             |                  |

| TSSOP                                                 |                  |

| Still-air (θ <sub>JA</sub> )                          | 93°C/W           |

| Junction-to-Case (θ <sub>IC</sub> )                   | 20°C/W           |

# DC Electrical Characteristics<sup>(6)</sup>

$V_{DD}$  =  $V_{DDIN}$  = 3.135V to 3.465V,  $T_A$  = -40°C to +85°C, unless otherwise stated. Rref = 475 $\Omega$

| Symbol                                | Parameter                            | Condition                | Min.  | Тур. | Max.                    | Units |

|---------------------------------------|--------------------------------------|--------------------------|-------|------|-------------------------|-------|

| $V_{DD}$ , $V_{DDIN}$                 | Power Supply Voltage Range           |                          | 3.135 | 3.3  | 3.465                   | ٧     |

| C <sub>IN</sub>                       | Input Capacitance                    |                          |       |      | 7                       | pF    |

| C <sub>out</sub>                      | Output Capacitance                   |                          |       |      | 6                       | pF    |

| L <sub>Pin</sub>                      | Pin Inductance                       |                          |       |      | 5                       | nΗ    |

| Rout                                  | Output Resistance                    |                          | 3     |      |                         | kΩ    |

| R <sub>pull up</sub>                  | Pull up Resistance                   | SEL, /PD, OE             |       | 110  |                         | kΩ    |

| V <sub>IH</sub>                       | Input High Voltage                   | SEL, /PD, OE             | 2     |      | V <sub>DDIN</sub> + 0.3 | V     |

| V <sub>IL</sub>                       | Input Low Voltage                    | SEL, /PD, OE             | -0.3  |      | 0.8                     | ٧     |

| V <sub>IH</sub>                       | Input High Voltage                   | HCSL, IN, /IN            | 660   | 750  | 850                     | ٧     |

| V <sub>IL</sub>                       | Input Low Voltage                    | HCSL, IN, /IN            | -150  | 0    |                         | ٧     |

| V <sub>IN</sub>                       | Differential Input Voltage Range     | LVDS, IN, /IN            | 250   | 350  | 550                     | mV    |

| V <sub>input offset</sub>             | Input Common Mode Voltage            | LVDS, IN, /IN,           | 1.125 | 1.25 | 1.375                   | V     |

| V <sub>OH</sub>                       | Output High Voltage                  | HSCL                     | 660   | 750  | 850                     | mV    |

| V <sub>OL</sub>                       | Output Low Voltage                   | HSCL                     | -150  | 0    | 27                      | mV    |

| Vcross <sup>(7, 8)</sup>              | Crossing Point Voltage               | Absolute                 | 250   | 350  | 550                     | mV    |

| Vcross_variation <sup>(7, 8, 9)</sup> | Variation of Crossing Point Voltage  | Variation over all edges |       |      | 140                     | mV    |

|                                       |                                      | 50Ω, 2pF                 |       | 75   | 90                      | mA    |

| I <sub>DD</sub>                       | Power Supply Current For VDD + VDDIN | No load, /PD = Low       |       |      | 0.4                     | mA    |

|                                       | אוטט י טט א                          | OE = Logic Low           |       |      | 20                      | mA    |

| I <sub>IL</sub> <sup>(10)</sup>       | Input Leakage Current                | $0 < V_{IN} < V_{DDIN}$  | -5    |      | 5                       | μΑ    |

#### Notes:

- Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this datasheet. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

- The datasheet limits are not guaranteed if the device is operated beyond the operating ratings.

- Package thermal resistance assumes that the exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB. WJB and  $\theta_{JA}$  values are determined for a 4-layer board in still-air unless otherwise stated. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

- 6. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

- Test setup is  $R_L = 50\Omega$  with 2pF,  $Rr = 475\Omega \pm 1\%$ .

- Measurement taken from Q and /Q.

- Measured at the crossing point where instantaneous voltages of CLK and /CLK are equal.

- 10. Inputs with pull-up/pull-down resistances are not included.

#### AC Electrical Characteristics<sup>(6)</sup>

$V_{DD} = V_{DDIN} = 3.135V$  to 3.465V,  $T_A = -40$ °C to +85°C, unless otherwise stated.

| Symbol                          | Parameter                                                     | Condition                                   | Min. | Тур. | Max. | Units             |

|---------------------------------|---------------------------------------------------------------|---------------------------------------------|------|------|------|-------------------|

| £                               | Maximum Francisco                                             | HCSL Termination                            |      |      | 267  | MHz               |

| f <sub>MAX</sub>                | Maximum Frequency                                             | LVDS Termination                            |      |      | 100  | MHz               |

| t <sub>PD</sub>                 | Propagation Delay                                             | Note 11                                     |      | 2    |      | ns                |

| t <sub>Skew</sub>               | Output-to-Output skew                                         | Notes 12, 13                                |      |      | 50   | ps                |

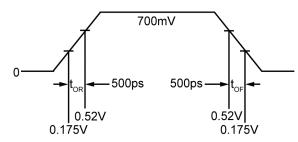

| t <sub>R</sub> , t <sub>F</sub> | Output Rise/Fall Times<br>0.175V to 0.525V / 0.525V to 0.175V | At full output swing. 50Ω, 2pF              | 175  | 338  | 700  | ps                |

| t <sub>R/F_var</sub>            | Rise/Fall Time Variation                                      | At full output swing. 50Ω, 2pF              |      |      | 125  | ps                |

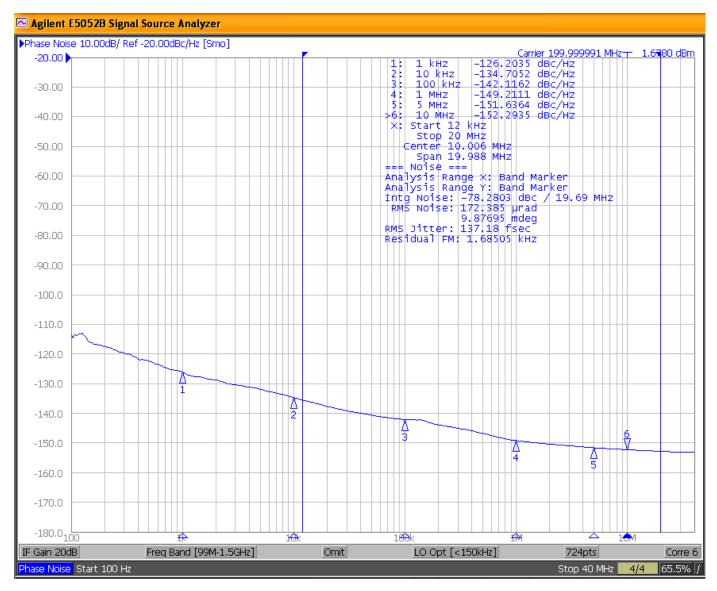

|                                 |                                                               | At 200MHz                                   |      | 137  |      | fs <sub>rms</sub> |

| T <sub>RJ_Jitter</sub>          | Phase Jitter                                                  | At 156.25MHz                                |      | 153  |      | fs <sub>rms</sub> |

|                                 |                                                               | At 100MHz                                   |      | 212  |      | fs <sub>rms</sub> |

| T <sub>TJ_Jitter</sub>          | Total Jitter                                                  | BER = $10^{-12}$ , $T_{DJ} = 0$ , at 200MHz |      | 2    |      | ps                |

| T <sub>OE_enable</sub>          | Output Enable Time                                            | All Outputs                                 |      | 2    |      | μs                |

| T <sub>OE_disable</sub>         | Output Disable Time                                           | All Outputs                                 |      | 10   |      | ns                |

| T <sub>DCY</sub>                | Duty Cycle                                                    |                                             | 45   | 50   | 55   | %                 |

#### Notes:

- 11. Measured from the differential input crossing point to the differential output crossing point.

- 12. Output-to-Output skew is the difference in time between outputs, receiving data from the same input, for the same temperature, voltage, and transition.

- 13. This parameter is defined in accordance with JEDEC Standard 65.

### **Jitter Analysis**

Jitter is defined as the deviation of a signal from its ideal position. Phase noise is the presence of signal energy at frequencies other than the carrier. Random jitter has a Gaussian distribution and is specified as an rms unit, which is one standard deviation of the distribution. Since Gaussian distribution is unbounded in an infinite sample, no communication system can be completely error free. Instead, communication links are rated with a maximum bit error rate (BER), which is typically around  $10^{-12}$  for high-speed communication equipment. Achieving a desired BER requires accounting for a number of standard deviations of random noise by using the appropriate value for N (see Table 1) in the formula in Equation 1.

$$T_i = N \times R_i + D_i$$

Eq. 1

Where Tj is total jitter, Rj is random jitter, and Dj is deterministic jitter. If routing clock signals, the deterministic jitter is usually negligible and the Tj is dominated by the random jitter. Calculating Tj from Rj using Equation 1 gives the values in Table 1.

**Table 1. Standard Deviations of Random Noise**

| BER               | N      | R <sub>j</sub> at 200MHz | T <sub>j</sub> at 200MHz |

|-------------------|--------|--------------------------|--------------------------|

| 10 <sup>-10</sup> | 12.723 | 137fs_rms                | 1.743ps                  |

| 10 <sup>-11</sup> | 13.412 | 137fs_rms                | 1.837ps                  |

| 10 <sup>-12</sup> | 14.069 | 137fs_rms                | 1.927ps                  |

| 10 <sup>-13</sup> | 14.698 | 137fs_rms                | 2.013ps                  |

SY75576L Micrel, Inc.

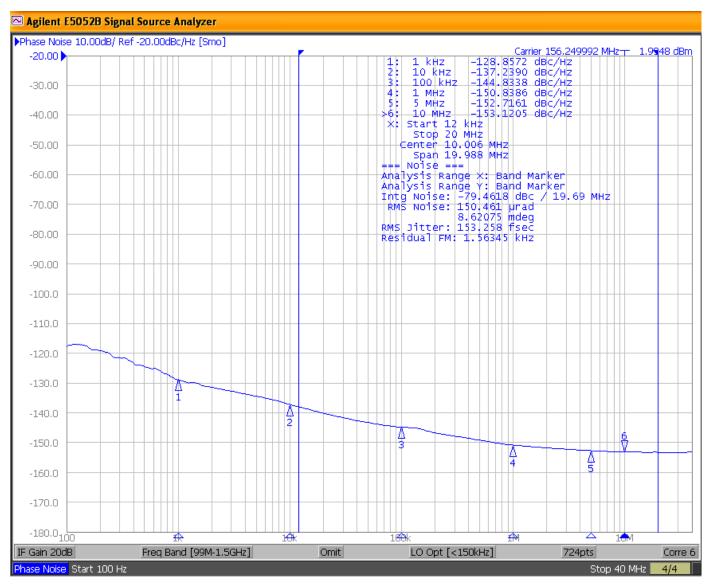

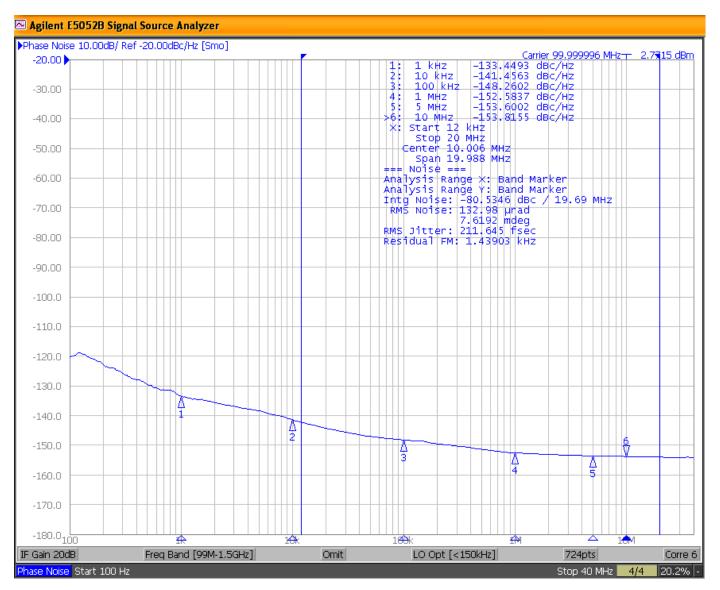

#### **Phase Noise Plots**

Phase jitter = 137fs<sub>rms</sub>, 200MHz carrier frequency; integration range: 12kHz-20MHz

Phase jitter = 153fs<sub>rms</sub>, 156.25MHz carrier frequency; integration range: 12kHz-20MHz

Phase jitter = 212fs<sub>rms</sub>, 100MHz carrier frequency; integration range: 12kHz-20MHz

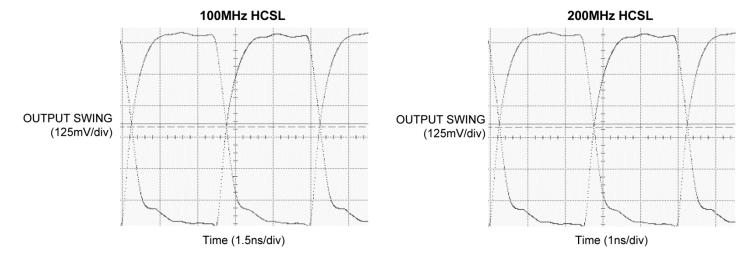

#### **Functional Characteristics**

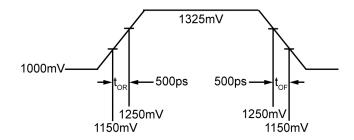

# **HCSL Waveform Diagram**

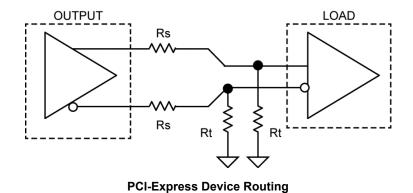

# **HCSL Interface Application**

$Rs = 33\Omega$

$Rt = 50\Omega$

# **LVDS Waveform Diagram**

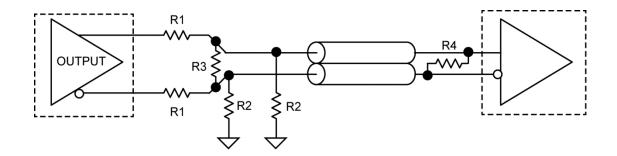

# **LVDS Interface Application**

$R1 = 33\Omega$

$R2 = 175\Omega$

$R3 = 140\Omega$

$R4 = 100\Omega$

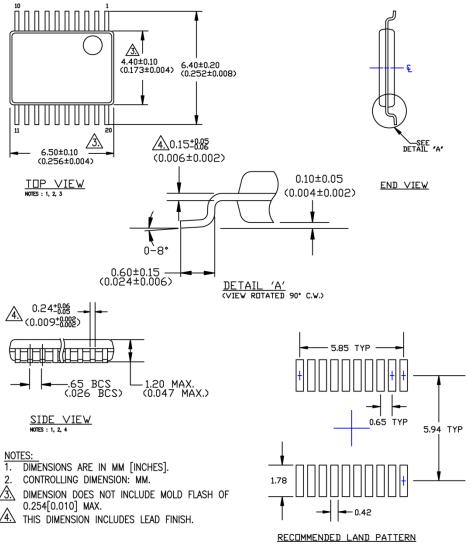

### Package Information<sup>(14)</sup>

20-Pin TSSOP

#### Note:

14. Package information is correct as of the publication date. For updates and most current information, go to <a href="https://www.micrel.com">www.micrel.com</a>.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2013 Micrel, Incorporated.

#### **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com