# FS6370-01G-XTD Datasheet

www.digi-electronics.com

| DiGi Electronics Part Number | FS6370-01G-XTD-DG                                                |

|------------------------------|------------------------------------------------------------------|

| Manufacturer                 | onsemi                                                           |

| Manufacturer Product Number  | FS6370-01G-XTD                                                   |

| Description                  | IC PLL CLOCK GENERATOR 16SOIC                                    |

| Detailed Description         | PLL Clock Generator IC 230MHz 1 16-SOIC (0.154",<br>.90mm Width) |

|                              |                                                                  |

3

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

### Purchase and inquiry

| Manufacturer Product Number:   | Manufacturer:                  |

|--------------------------------|--------------------------------|

| FS6370-01G-XTD                 | onsemi                         |

| Series:                        | Product Status:                |

|                                | Obsolete                       |

| DiGi-Electronics Programmable: | Туре:                          |

| Verified                       | PLL Clock Generator            |

| PLL:                           | Input:                         |

| Yes                            | Crystal                        |

| Output:                        | Number of Circuits:            |

| CMOS                           | 1                              |

| Ratio - Input:Output:          | Differential - Input:Output:   |

| 1:4                            | No/No                          |

| Frequency - Max:               | Divider/Multiplier:            |

| 230MHz                         | Yes/No                         |

| Voltage - Supply:              | Operating Temperature:         |

| 3V ~ 5.5V                      | 0°C ~ 70°C                     |

| Mounting Type:                 | Package / Case:                |

| Surface Mount                  | 16-SOIC (0.154", 3.90mm Width) |

| Supplier Device Package:       | Base Product Number:           |

| 16-SOIC                        | FS6370                         |

|                                |                                |

### **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 2 (1 Year)                        |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

## FS6370 EEPROM Programmable 3-PLL Clock Generator IC

### **1.0 Features**

- Just-in-time customization of clock frequencies via internal non-volatile 128-bit serial EEPROM

- I<sup>2</sup>C<sup>™</sup>-bus serial interface

- Three on-chip PLLs with programmable reference and feedback dividers

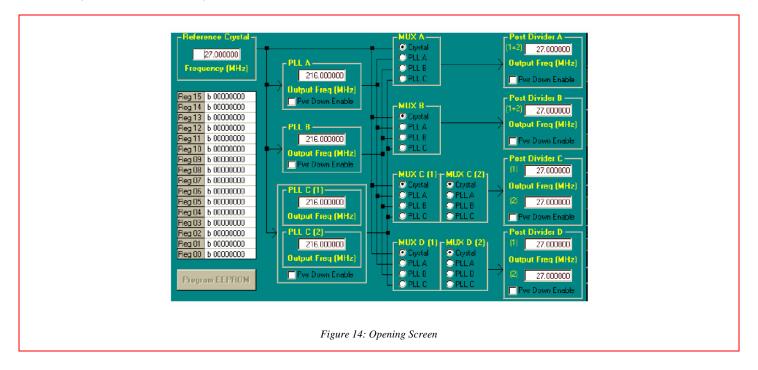

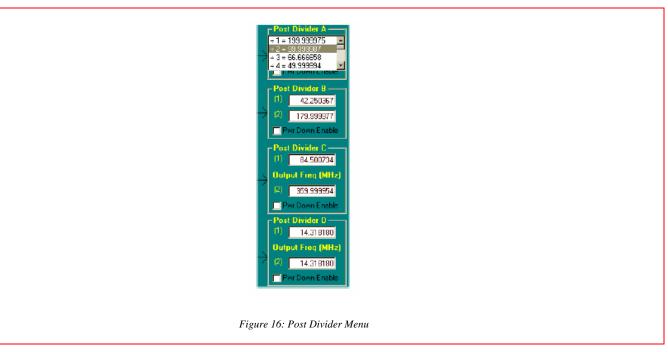

- Four independently programmable muxes and post dividers

- Programmable power-down of all PLLs and output clock drivers

- Tristate outputs for board testing

- One PLL and two mux/post-divider combinations can be modified via SEL\_CD input

- 5 V to 3.3 V operation

- · Accepts 5 MHz to 27 MHz crystal resonators

### 2.0 Description

The FS6370 is a CMOS clock generator IC designed to minimize cost and component count in a variety of electronic systems. Three EEPROM-programmable phase-locked loops (PLLs) driving four programmable muxes and post dividers provide a high degree of flexibility.

An internal EEPROM permits just-in-time factory programming of devices for end user requirements.

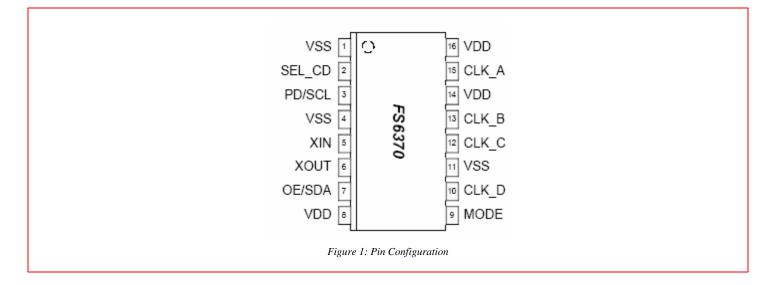

### Table 1: Pin Descriptions

| Pin | Туре              | Name   | Description                                                                         |

|-----|-------------------|--------|-------------------------------------------------------------------------------------|

| 1   | Р                 | VSS    | Ground                                                                              |

| 2   | DI                | SEL_CD | Selects one of two programmed PLL C, Mux C/D and post divider C/D combinations      |

| 3   | DI                | PD/SCL | Power-down input (run-mode) or serial interface clock input (program mode)          |

| 4   | Р                 | VSS    | Ground                                                                              |

| 5   | AI                | XIN    | Crystal oscillator feedback                                                         |

| 6   | AO                | XOUT   | Crystal oscillator drive                                                            |

| 7   | DI <sup>U</sup> O | OE/SDA | Output enable input (run mode) or serial interface data input/output (program mode) |

| 8   | Р                 | VDD    | Power supply (5 V to 3.3 V)                                                         |

| 9   | DI                | MODE   | Selects either program mode (low) or run mode (high)                                |

| 10  | DO                | CLK_D  | D clock output                                                                      |

| 11  | P                 | VSS    | Ground                                                                              |

| 12  | DO                | CLK_C  | C clock output                                                                      |

| 13  | DO                | CLK_B  | B clock output                                                                      |

| 14  | Р                 | VDD    | Power supply (5 V to 3.3 V)                                                         |

| 15  | DO                | CLK_A  | A clock output                                                                      |

| 16  | Р                 | VDD    | Power supply (5 V to 3.3 V)                                                         |

Key: AI = Analog Input; AO = Analog Output; DI = Digital Input; DI<sup>U</sup> = Input with Internal Pull-Up; DI<sub>D</sub> = Input with Internal Pull-Down; DIO = Digital Input/Output; DI-3 = Three-Level Digital Input, DO = Digital Output; P = Power/Ground; # = Active Low pin

### **3.0 Functional Block Description**

### 3.1 Phase Locked Loops (PLLs)

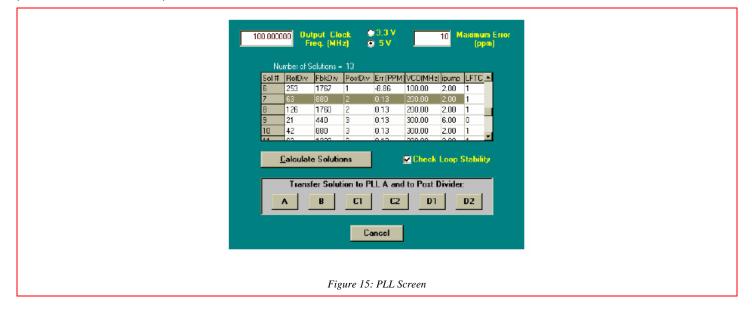

Each of the three on-chip PLLs is a standard phase- and frequency-locked loop architecture that multiplies a reference frequency to a desired frequency by a ratio of integers. This frequency multiplication is exact.

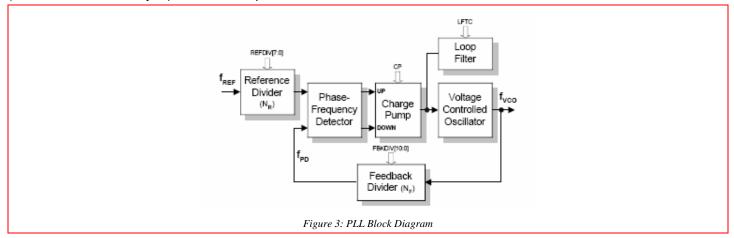

As shown in Figure 3, each PLL consists of a reference divider, a phase-frequency detector (PFD), a charge pump, an internal loop filter, a voltage-controlled oscillator (VCO), and a feedback divider.

During operation, the reference frequency ( $f_{REF}$ ), generated by the on-board crystal oscillator, is first reduced by the reference divider. The divider value is often referred to as the modulus, and is denoted as  $N_R$  for the reference divider. The divided reference is fed into the PFD.

The PFD controls the frequency of the VCO ( $f_{VCO}$ ) through the charge pump and loop filter. The VCO provides a high-speed, low noise, continuously variable frequency clock source for the PLL. The output of the VCO is fed back to the PFD through the feedback divider (the modulus is denoted by N<sub>F</sub>) to close the loop.

The PFD will drive the VCO up or down in frequency until the divided reference frequency and the divided VCO frequency appearing at the inputs of the PFD are equal. The input/output relationship between the reference frequency and the VCO frequency is:

$$f_{VCO} = f_{REF} \left( \frac{N_F}{N_R} \right)$$

### 3.1.1. Reference Divider

The reference divider is designed for low phase jitter. The divider accepts the output of the reference oscillator and provides a divideddown frequency to the PFD. The reference divider is an 8-bit divider, and can be programmed for any modulus from 1 to 255 by programming the equivalent binary value. A divide-by-256 can also be achieved by programming the eight bits to 00h.

### 3.1.2. Feedback Divider

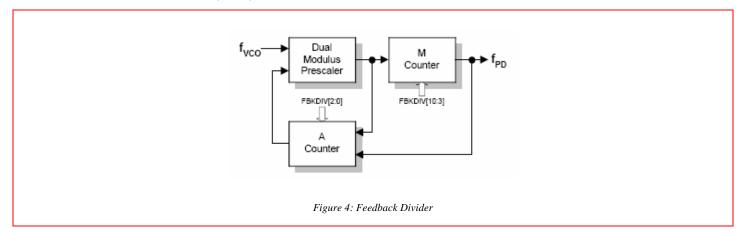

The feedback divider is based on a dual-modulus pre-scaler technique. The technique allows the same granularity as a fully programmable feedback divider, while still allowing the programmable portion to operate at low speed. A high-speed pre-divider (also called a pre-scaler) is placed between the VCO and the programmable feedback divider because of the high speeds at which the VCO can operate. The dual-modulus technique insures reliable operation at any speed that the VCO can achieve and reduces the overall power consumption of the divider.

For example, a fixed divide-by-eight pre-scaler could have been used in the feedback divider. Unfortunately, a divide-by-eight would limit the effective modulus of the entire feedback divider to multiples of eight. This limitation would restrict the ability of the PLL to

achieve a desired input-frequency-to-output-frequency ratio without making both the reference and feedback divider values comparatively large. Generally, very large values are undesirable as they degrade the bandwidth of the PLL, increasing phase jitter and acquisition time.

To understand the operation of the feedback divider, refer to Figure 4. The M-counter (with a modulus always equal to M) is cascaded with the dual-modulus pre-scaler. The A-counter controls the modulus of the pres-caler. If the value programmed into the A-counter is A, the pre-scaler will be set to divide by N+1 for A pre-scaler outputs. Thereafter, the prescaler divides by N until the M-counter output resets the A-counter, and the cycle begins again. Note that N=8, and A and M are binary numbers.

Suppose that the A-counter is programmed to zero. The modulus of the pre-scaler will always be fixed at N; and the entire modulus of the feedback divider becomes MxN.

Next, suppose that the A-counter is programmed to a one. This causes the pre-scaler to switch to a divide-by-N+1 for its first divide cycle and then revert to a divide-by-N. In effect, the A-counter absorbs (or "swallows") one extra clock during the entire cycle of the feedback divider. The overall modulus is now seen to be equal to MxN+1.

This example can be extended to show that the feedback divider modulus is equal to MxN+A, where A<M.

### 3.1.3. Feedback Divider Programming

For proper operation of the feedback divider, the A-counter must be programmed only for values that are less than or equal to the M-counter. Therefore, not all divider moduli below 56 are available for use. This is shown in Table 2.

Above a modulus of 56, the feedback divider can be programmed to any value up to 2047.

| M-Counter:   | A-Counter: FBKDIV[2:0] |     |     |              |               |     |     |     |

|--------------|------------------------|-----|-----|--------------|---------------|-----|-----|-----|

| FBKDIV[10:3] | 000                    | 001 | 010 | 011          | 100           | 101 | 110 | 111 |

| 0000001      | 8                      | 9   | -   | -            | -             | -   | -   | -   |

| 0000010      | 16                     | 17  | 18  | -            | -             | -   | -   | -   |

| 0000011      | 24                     | 25  | 26  | 27           | -             | -   | -   | -   |

| 00000100     | 32                     | 33  | 34  | 35           | 36            | -   | -   | -   |

| 00000101     | 40                     | 41  | 42  | 43           | 44            | 45  | -   | -   |

| 00000110     | 48                     | 49  | 50  | 51           | 52            | 53  | 54  | -   |

| 00000111     | 56                     | 57  | 58  | 59           | 60            | 61  | 62  | 63  |

|              |                        |     |     | Feedback Div | vider Modulus |     |     |     |

Table 2: Feedback Divider Modulus Under 56

### 3.2 Post Divider Muxes

As shown in Figure 2, a mux in front of each post divider stage can select from any one of the three PLL frequencies or the reference frequency. The mux selection is controlled by bits in the EEPROM or the control registers.

The input frequency on two of the four multiplexers (muxes C and D in Figure 2) can be altered without reprogramming by a logic-level input on the SEL\_CD pin.

### **3.3 Post Dividers**

A post divider performs several useful functions. First, it allows the VCO to be operated in a narrower range of speeds compared to the variety of output clock speeds that the device is required to generate. Second, it changes the basic PLL equation to:

$$f_{CLK} = f_{REF} \left( \frac{N_F}{N_R} \right) \left( \frac{1}{N_P} \right)$$

where NP is the post divider modulus. The extra integer in the denominator permits more flexibility in the programming of the loop for many applications where frequencies must be achieved exactly.

The modulus on two of the four post dividers (post dividers C and D in Figure 2) can be altered without reprogramming by a logic level on the SEL\_CD pin.

### **4.0 Device Operation**

The FS6370 has two modes of operation:

- Program mode: during which either the EEPROM or the FS6370 control registers can be programmed directly with the desired PLL settings

- Run mode: where the PLL settings stored the EEPROM are transferred to the FS6370 control registers on power-up, and the device then operates based on those settings

Note that the EEPROM locations are not physically the same registers used to control the FS6370.

Direct access to either the EEPROM or the FS6370 control registers is achieved in program mode. The EEPROM register contents are automatically transferred to the FS6370 control registers in normal device operation (run mode).

### 4.1 MODE Pin

The MODE pin controls the mode of operation. A logic-low places the FS6370 in program mode. A logic-high puts the device in run mode. A pull-up on this pin defaults the device into run mode.

Reprogramming of either the control registers or the EEPROM is permitted at any time if the MODE pin is a logic-low.

Note, however, that a logic-high state on the MODE pin is latched so that only one transfer of EEPROM data to the FS6370 control registers can occur. If a second transfer of EEPROM data into the FS6370 is desired, power (VDD) must be removed and reapplied to the device.

The MODE pin also controls the function of the PD/SCL and OE/SDA pins. In run mode, these two pins function as power-down (PD) and output enable (OE) controls. In program mode, the pins function as the I<sub>2</sub>C interface for clock (SCL) and data (SDA).

### 4.2 SEL\_CD Pin

The SEL\_CD pin provides a way to alter the operation of PLL C, muxes C and D, and post dividers C and D without having to reprogram the device. A logic-low on the SEL\_CD pin selects the control bits with a "C1" or "D1" notation, per Table 3. A logic-high on the SEL\_CD pin selects the control bits with "C2" or "D2" notation, per Table 3.

Note that changing between two running frequencies using the SEL\_CD pin may produce glitches in the output, especially if the postdivider(s) is/are altered.

#### 4.3 Oscillator Overdrive

For applications where an external reference clock is provided (and the crystal oscillator is not required), the reference clock should be connected to XOUT and XIN must be left unconnected (float).

For best results, make sure the reference clock signal is as jitter-free as possible, can drive a 40 pF load with fast rise and fall times, and can swing rail-to-rail.

If the reference clock is not a rail-to-rail signal, the reference must be AC coupled to XOUT through a 0.01 µF or 0.1 µF capacitor. A minimum 1 V peak-to-peak signal is required to drive the internal differential oscillator buffer.

### 5.0 Run Mode

If the MODE pin is set to a logic-high, the device enters the run mode. The high state is latched (see MODE pin). The FS6370 then copies the stored EEPROM data into its control registers and begins normal operation based on that data when the self-load is complete.

The self-load process takes about 89,000 clocks of the crystal oscillator. During the self-load time, all clock outputs are held low. At a reference frequency of 27 MHz, the self-load takes about 3.3ms to complete.

If the EEPROM is empty (all zeros), the crystal reference frequency provides the clock for all four outputs.

No external programming access to the FS6370 is possible in run mode. The dual-function PD/SCL and OE/SDA pins become a power-down (PD) and output enable (OE) control, respectively.

### 5.1 Power-Down and Output Enable

A logic-high on the PD/SCL pin powers down only those portions of the FS6370 which have their respective power-down control bits enabled. Note that the PD/SCL pin has an internal pull-up.

When a post divider is powered down, the associated output driver is forced low. When all PLLs and post dividers are powered down the crystal oscillator is also powered down. The XIN pin is forced low, and the XOUT pin is pulled high.

A logic-low on the OE/SDA pin tristates all output clocks. Note that this pin has an internal pull-up.

### 6.0 Program Mode

If the MODE pin is logic-low, the device enters the program mode. All internal registers are cleared to zero, delivering the crystal frequency to all outputs. The device allows programming of either the internal 128-bit EEPROM or the on-chip control registers via I<sub>2</sub>C control over the PD/SCL and OE/SDA pins. The EEPROM and the FS6370 act as two separate parallel devices on the same on-chip I<sub>2</sub>C-bus. Choosing either the EEPROM or the device control registers is done via the I<sub>2</sub>C device address.

The dual-function PD/SCL and OE/SDA pins become the serial data I/O (SDA) and serial clock input (SCL) for normal I<sub>2</sub>C communications. Note that power-down and output enable control via the PD/SCL and OE/SDA pins is not available.

### 6.1 EEPROM Programming

Data must be loaded into the EEPROM in a most-significant-bit (MSB) to least-significant-bit (LSB) order. The register map of the EEPROM is noted in Table 3.

#### The device address of the EEPROM is:

| A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 0  | Х  | Х  | X  |

### 6.1.1. Write Operation

The EEPROM can only be written to with the random register write procedure (see Section 8.2.2). The procedure consists of the device address, the register address, a R/W bit, and one byte of data.

Following the STOP condition, the EEPROM initiates its internally timed 4ms write cycle, and commits the data byte to memory. No acknowledge signals are generated during the EEPROM internal write cycle.

If a stop bit is transmitted before the entire write command sequence is complete, then the command is aborted and no data is written to memory. If more than eight bits are transmitted before the stop bit is sent, then the EEPROM will clear the previously loaded data byte and will begin loading the data buffer again.

### 6.1.2. Acknowledge Polling

The EEPROM does not acknowledge while it internally commits data to memory. This feature can be used to increase data throughput by determining when the internal write cycle is complete.

The process is to initiate the random register write procedure with a START condition, the EEPROM device address, and the write command bit (R/W=0).

If the EEPROM has completed its internal 4 ms write cycle, the EEPROM will acknowledge on the next clock, and the write command can continue.

If the EEPROM has not completed the internal 4 ms write cycle, the random register write procedure must be restarted by sending the START condition, device address and R/W bit. This sequence must be repeated until the EEPROM acknowledges.

### 6.1.3. Read Operation

The EEPROM supports both the random register read procedure and the sequential register read procedure (both are outlined in Section 6).

For sequential read operations, the EEPROM has an internal address pointer that increments by one at the end of each read operation. The pointer directs the EEPROM to transmit the next sequentially addressed data byte, allowing the entire memory contents to be read in one operation.

### 6.2 Direct Register Programming

The FS6370 control registers may be directly accessed by simply using the FS6370 device address in the read or write operations. The operation of the device will follow the register values. The register map of the FS6370 is identical to that of the EEPROM shown in Table 3.

The FS6370 supports the random read and write procedures, as well as the sequential read and write procedures described in Section 8.

#### The device address for the FS6370 is:

| A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 1  | 1  | 0  | 0  |

### 7.0 Cost Reduction Migration Path

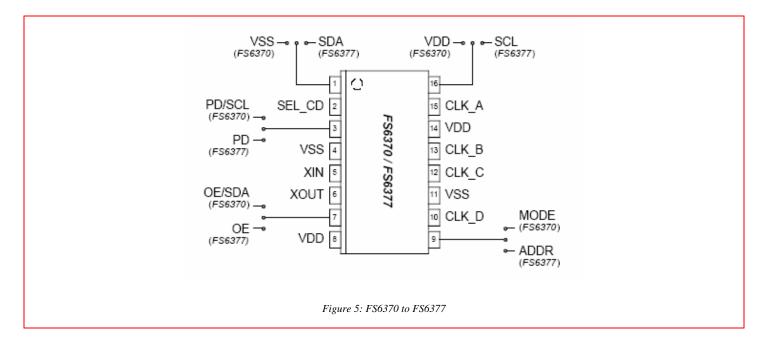

The FS6370 is compatible with the programmable register-based FS6377 or a fixed-frequency ROM-based clock generator. Attention should be paid to the board layout if a migration path to either of these devices is desired.

### 7.1 Programming Migration Path

If the design can support I<sub>2</sub>C programming overhead, a cost reduction from the EEPROM-based FS6370 to the register-based FS6377 is possible.

Figure 5 shows the five pins that may not be compatible between the various devices if programming of the FS6370 or the FS6377 is desired.

### 7.2 Non-Programming Migration Path

If the design has solidified on a particular EEPROM programming pattern, the EEPROM pattern can be hard-coded into a ROM-based device. For high-volume requirements, a ROM-based device offers significant cost savings over the FS6370. Contact an ON Semiconductor sales representative for more detail.

### **8.0 I<sub>2</sub>C-bus Control Interface**

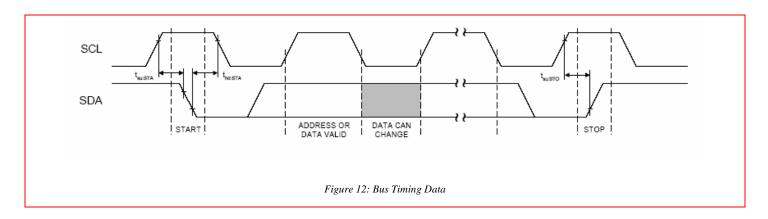

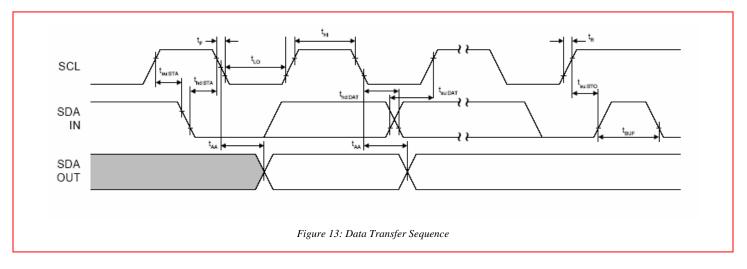

This device is a read/write slave device meeting all Philips I<sub>2</sub>C-bus specifications except a "general call." The bus has to be controlled by a master device that generates the serial clock SCL, controls bus access and generates the START and STOP conditions while the device works as a slave. Both master and slave can operate as a transmitter or receiver, but the master device determines which mode is activated. A device that sends data onto the bus is defined as the transmitter, and a device receiving data as the receiver.

I<sub>2</sub>C-bus logic levels noted herein are based on a percentage of the power supply ( $V_{DD}$ ). A logic-one corresponds to a nominal voltage of  $V_{DD}$ , while a logic-low corresponds to ground ( $V_{SS}$ ).

### 8.1 Bus Conditions

Data transfer on the bus can only be initiated when the bus is not busy. During the data transfer, the data line (SDA) must remain stable whenever the clock line (SCL) is high. Changes in the data line while the clock line is high will be interpreted by the device as a START or STOP condition. The following bus conditions are defined by the l<sub>2</sub>C-bus protocol.

#### 8.1.1. Not Busy

Both the data (SDA) and clock (SCL) lines remain high to indicate the bus is not busy.

### 8.1.2. START Data Transfer

A high to low transition of the SDA line while the SCL input is high indicates a START condition. All commands to the device must be preceded by a START condition.

### 8.1.3. STOP Data Transfer

A low to high transition of the SDA line while SCL is held high indicates a STOP condition. All commands to the device must be followed by a STOP condition.

### 8.1.4. Data Valid

The state of the SDA line represents valid data if the SDA line is stable for the duration of the high period of the SCL line after a START condition occurs. The data on the SDA line must be changed only during the low period of the SCL signal. There is one clock pulse per data bit.

Each data transfer is initiated by a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is determined by the master device, and can continue indefinitely. However, data that is overwritten to the device after the first 16 bytes will overflow into the first register, then the second, and so on, in a first-in, first-overwritten fashion.

### 8.1.5. Acknowledge

When addressed, the receiving device is required to generate an acknowledge after each byte is received. The master device must generate an extra clock pulse to coincide with the acknowledge bit. The acknowledging device must pull the SDA line low during the high period of the master acknowledge clock pulse. Setup and hold times must be taken into account.

The master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been read (clocked) out of the slave. In this case, the slave must leave the SDA line high to enable the master to generate a STOP condition.

### 8.2 I<sub>2</sub>C-bus Operation

All programmable registers can be accessed randomly or sequentially via this bi-directional two wire digital interface. The device accepts the following I<sub>2</sub>C-bus commands.

### 8.2.1. Device Address

After generating a START condition, the bus master broadcasts a seven-bit device address followed by a R/W bit.

The device address of the FS6370 is:

| A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 1  | 1  | 0  | 0  |

| Any one of eight possible addresses are available for the EEPROM. | The least aignificant three hits are den't ears's |

|-------------------------------------------------------------------|---------------------------------------------------|

| Any one of eight possible addresses are available for the EEFRON. |                                                   |

| A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 0  | Х  | Х  | Х  |

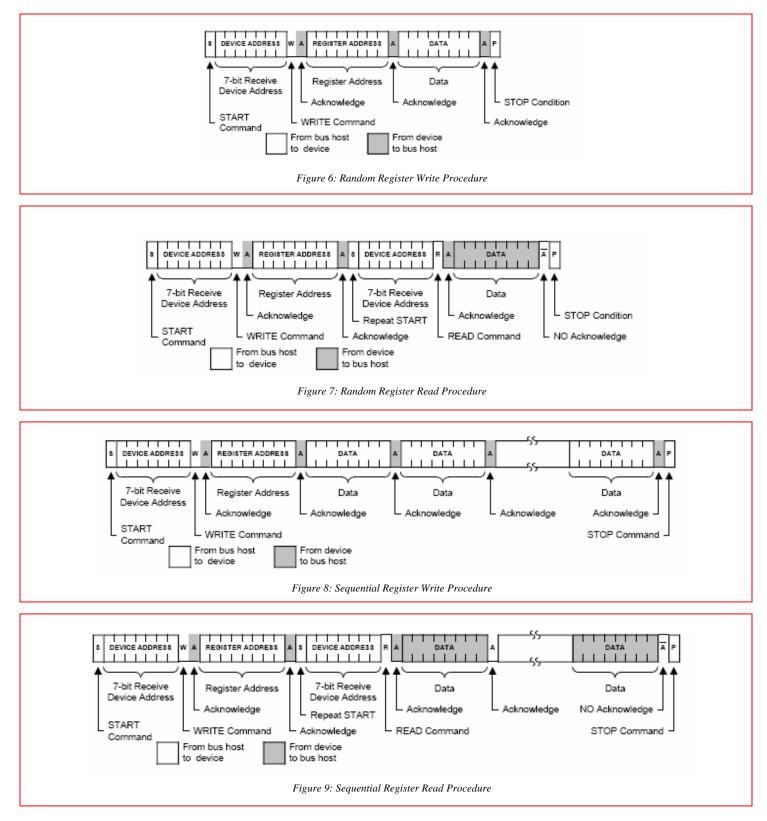

#### 8.2.2. Random Register Write Procedure

Random write operations allow the master to directly write to any register. To initiate a write procedure, the R/W bit that is transmitted after the seven-bit device address is a logic-low. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is written into the slave's address pointer. Following an acknowledge by the slave, the master is allowed to write eight bits of data into the addressed register. A final acknowledge is returned by the device, and the master generates a STOP condition.

If either a STOP or a repeated START condition occurs during a register write, the data that has been transferred is ignored.

### 8.2.3. Random Register Read Procedure

Random read operations allow the master to directly read from any register. To perform a read procedure, the R/W bit that is transmitted after the seven-bit address is a logic-low, as in the register write procedure. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is then written into the slave's address pointer.

Following an acknowledge by the slave, the master generates a repeated START condition. The repeated START terminates the write procedure, but not until after the slave's address pointer is set. The slave address is then resent, with the R/W bit set this time to a logic-high, indicating to the slave that data will be read. The slave will acknowledge the device address, and then transmits the eight-bit word. The master does not acknowledge the transfer but does generate a STOP condition.

### 8.2.4. Sequential Register Write Procedure

Sequential write operations allow the master to write to each register in order. The register pointer is automatically incremented after each write. This procedure is more efficient than the random register write if several registers must be written.

To initiate a write procedure, the R/W bit that is transmitted after the seven-bit device address is a logic-low. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is written into the slave's address pointer. Following an acknowledge by the slave, the master is allowed to write up to 16 bytes of data into the addressed register before the register address pointer overflows back to the beginning address. An acknowledge by the device between each byte of data must occur before the next data byte is sent.

Registers are updated every time the device sends an acknowledge to the host. The register update does not wait for the STOP condition to occur. Registers are therefore updated at different times during a sequential register write.

### 8.2.5. Sequential Register Read Procedure

Sequential read operations allow the master to read from each register in order. The register pointer is automatically incremented by one after each read. This procedure is more efficient than the random register read if several registers must be read.

To perform a read procedure, the R/W bit that is transmitted after the seven-bit address is a logic-low, as in the register write procedure. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is then written into the slave's address pointer.

Following an acknowledge by the slave, the master generates a repeated START condition. The repeated START terminates the write procedure, but not until after the slave's address pointer is set. The slave address is then resent, with the R/W bit set this time to a logic-high, indicating to the slave that data will be read. The slave will acknowledge the device address, and then transmits all 16 bytes of data starting with the initial addressed register. The register address pointer will overflow if the initial register address is larger than zero. After the last byte of data, the master does not acknowledge the transfer but does generate a STOP condition.

#### FS6370-01G-XTD onsemi IC PLL CLOCK GENERATOR 16SOIC

## FS6370

### 9.0 Programming Information

| Address | Bit 7 Bit 6                           | Bit 5           | Bit 4          | Bit 3           | Bit 2            | Bit 1            | Bit 0    |

|---------|---------------------------------------|-----------------|----------------|-----------------|------------------|------------------|----------|

| Byte 15 | MUX_D2[1:0]                           | MUX_            | C2[1:0]        | PDPOST_D        | PDPOST_C         | PDPOST_B         | PDPOST_A |

|         | (selected via SEL_CD = 1)             | (selected via   | $SEL_CD = 1$ ) |                 |                  |                  |          |

| Byte 14 | POST                                  | D2[3:0]         |                |                 | POST_C           | 2[3:0]           |          |

|         | (selected via                         | $SEL_CD = 1$ )  |                |                 | (selected via SI | EL_CD = 1)       |          |

| Byte 13 | POST                                  | _D1[3:0]        |                |                 | POST_C           | 1[3:0]           |          |

|         | · · · · · · · · · · · · · · · · · · · | $SEL_CD = 0$ )  |                |                 | (selected via SI | EL_CD = 0)       |          |

| Byte 12 | POST                                  | _B[3:0]         |                |                 | POST_A           | [3:0]            |          |

| Byte 11 | MUX_D1[1:0]                           | Reserved (0)    | LFTC_C2        | CP_C2           | FBKDIV           | /_C2[10:8] M-Cou | unter    |

|         | (selected via SEL_CD = 0)             |                 | (SEL_CD=1)     | (SEL_CD=1)      | (selected        | d via SEL_CD pir | า = 1)   |

| Byte 10 |                                       | DIV_C2[7:3] M-C |                |                 |                  | V_C2[2:0] A-Cou  |          |

|         | (selec                                | ted via SEL_CD  | pin = 1)       |                 | (selected        | d via SEL_CD pir | 1 = 1)   |

| Byte 9  |                                       |                 |                | IV_C2[7:0]      |                  |                  |          |

|         |                                       |                 | · · ·          | SEL_CD pin = 1) |                  |                  |          |

| Byte 8  | MUX_C1[1:0]                           | PDPLL_C         | LFTC_C1        | CP_C1           |                  | /_C1[10:8] M-Cou |          |

|         | (selected via SEL_CD = 0)             |                 | (SEL_CD=0)     | (SEL_CD=0)      |                  | ted via SEL_CD = | /        |

| Byte 7  |                                       | DIV_C1[7:3] M-C |                |                 |                  | V_C1[2:0] A-Cou  |          |

|         | (se                                   | ected via SEL_C |                |                 | (select          | ted via SEL_CD = | = 1)     |

| Byte 6  |                                       |                 |                | IV_C1[7:0]      |                  |                  |          |

|         |                                       | <u> </u>        | · · ·          | a SEL_CD = 0)   |                  |                  |          |

| Byte 5  | MUX_B[1:0]                            | PDPLL_B         | LFTC_B         | CP_B            |                  | V_B[10:8] M-Cou  |          |

| Byte 4  | FBł                                   | ounter          |                | FBKD            | IV_B[2:0] A-Cour | nter             |          |

| Byte 3  |                                       |                 |                | 0IV_B[7:0]      |                  |                  |          |

| Byte 2  | MUX_A[1:0]                            | PDPLL_A         | LFTC_A         | CP_A            | FBKDI            | V_A[10:8] M-Cou  | nter     |

| Byte 1  | FBP                                   | DIV_A[7:3] M-Co | ounter         |                 | FBKD             | IV_A[2:0] A-Cour | nter     |

| Byte 0  |                                       |                 | REFD           | 0IV_A[7:0]      |                  |                  |          |

#### Table 3: Register Map (Note: All register bits are cleared to zero on power-up)

### 9.1 Control Bit Assignments

If any PLL control bit is altered during device operation, including those bits controlling the reference and feedback dividers, the output frequency will slew smoothly (in a glitch-free manner) to the new frequency. The slew rate is related to the programmed loop filter time constant.

However, any programming changes to any mux or post divider control bits will cause a glitch on an operating clock output.

### 9.1.1. Power-Down

All power-down functions are controlled by enable bits. That is, the bits select which portions of the FS6370 to power-down when the PD input is asserted. If the power-down bit contains a one, the related circuit will shut down if the PD pin is high (run mode only). When the PD pin is low, power is enabled to all circuits.

If the power-down bit contains a zero, the related circuit will continue to function regardless of the PD pin state.

### Table 4: Power-Down Bits

| Name                     | Description               |           |

|--------------------------|---------------------------|-----------|

|                          | Power-Down PLL A          |           |

| PDPLL_A                  | Bit = 0                   | Power on  |

| (Bit 21)                 | Bit = 1                   | Power off |

|                          | Power-Down PLL B          |           |

| PDPLL_B                  | Bit = 0                   | Power on  |

| (Bit 45)                 | Bit = 1                   | Power off |

|                          | Power-Doan PLL C          |           |

| PDPLL_C                  | Bit = 0                   | Power on  |

| (Bit 69)                 | Bit = 1                   | Power off |

| Reserved (0)<br>(Bit 69) |                           |           |

|                          | Power-Down POST Divider A |           |

| PDPOST_A                 | Bit = 0                   | Power on  |

| (Bit 120)                | Bit = 1                   | Power off |

|                          | Power-Down POST Divider B |           |

| PDPOST_B                 | Bit = 0                   | Power on  |

| (Bit 121)                | Bit = 1                   | Power off |

|                          | Power-Down POST Divider C |           |

| PDPOSTC                  | Bit = 0                   | Power on  |

| (Bit 122)                | Bit = 1                   | Power off |

|                          | Power-Down POST Divider D |           |

| PDPOSTD                  | Bit = 0                   | Power on  |

| (Bit 123)                | Bit = 1                   | Power off |

### Table 5: Divider Control Bits

| Name            | Description                            |                 |

|-----------------|----------------------------------------|-----------------|

| REFDIV_A[7:0]   | Reference Divider A (N <sub>R</sub> )  |                 |

| (Bits 7-0)      |                                        |                 |

| REFDIV_B[7:0]   | Reference Divider B (N <sub>R</sub> )  |                 |

| (Bits 31-24)    |                                        |                 |

| REFDIV_C1[7:0]  | Reference Divider C1 (N <sub>R</sub> ) |                 |

| (Bits 55-48)    | selected when the SEL-CD pin = 0       |                 |

| REFDIV_C2[7:0]  | Reference Divider C2 (N <sub>R</sub> ) |                 |

| (Bits 79-72)    | selected when the SEL-CD pin = 1       |                 |

|                 | Feedback Divider A (N <sub>F</sub> )   |                 |

| FBKDIV_A[10:0]  | FBKDIV_A[2:0]                          | A-Counter value |

| (Bits 18-8)     | FBKDIV_A[10:3]                         | M-Counter value |

|                 | Feedback Divider B (N <sub>F</sub> )   |                 |

| FBKDIV_B[10:0]  | FBKDIV_B[2:0]                          | A-Counter value |

| (Bits 42-32)    | FBKDIV_B[10:3]                         | M-Counter value |

|                 | Feedback Divider C1 (N <sub>F</sub> )  |                 |

|                 | selected when the SEL-CD pin = 0       |                 |

| FBKDIV_C1[10:0] | FBKDIV_C1[2:0]                         | A-Counter value |

| (Bits 66-56)    | FBKDIV_C1[10:3]                        | M-Counter value |

|                 | Feedback Divider C2 (N <sub>F</sub> )  |                 |

|                 | selected when the SEL-CD pin = 1       |                 |

| FBKDIV_C2[10:0] | FBKDIV_C2[2:0]                         | A-Counter value |

| (Bits 90-80)    | FBKDIV_C2[10:3]                        | M-Counter value |

### Table 6: Post Divider Control Bits

| Name                          | Description                      |

|-------------------------------|----------------------------------|

| POST_A[3:0]<br>(Bits 99-96)   | POST divider A (see Table 7)     |

| POST_B[3:0]<br>(Bits 103-100) | POST divider B (see Table 7)     |

| POST_C1[3:0]                  | POST divider C1 (see Table 7)    |

| (Bits 107-104)                | selected when the SEL_CD pin = 0 |

| POST_C2[3:0]                  | POST divider C2 (see Table 7)    |

| (Bits 115-112)                | selected when the SEL_CD pin = 1 |

| POST_D1[3:0]                  | POST divider D1 (see Table 7)    |

| (Bits 111-108)                | selected when the SEL_CD pin = 0 |

| POST_D2[3:0]                  | POST divider D2 (see Table 7)    |

| (Bits 119-116)                | selected when the SEL_CD pin = 1 |

### Table 7: Post Divider Modulus

| Bit [3] | Bit [2] | Bit [1] | Bit [0] | Divide By |

|---------|---------|---------|---------|-----------|

| 0       | 0       | 0       | 0       | 1         |

| 0       | 0       | 0       | 1       | 2         |

| 0       | 0       | 1       | 0       | 3         |

| 0       | 0       | 1       | 1       | 4         |

| 0       | 1       | 0       | 0       | 5         |

| 0       | 1       | 0       | 1       | 6         |

| 0       | 1       | 1       | 0       | 8         |

| 0       | 1       | 1       | 1       | 9         |

| 1       | 0       | 0       | 0       | 10        |

| 1       | 0       | 0       | 1       | 12        |

| 1       | 0       | 1       | 0       | 15        |

| 1       | 0       | 1       | 1       | 16        |

| 1       | 1       | 0       | 0       | 18        |

| 1       | 1       | 0       | 1       | 20        |

| 1       | 1       | 1       | 0       | 25        |

| 1       | 1       | 1       | 1       | 50        |

### Table 8: PLL Tuning Bits

| Name     | Description                                       |                           |  |  |  |  |

|----------|---------------------------------------------------|---------------------------|--|--|--|--|

|          | Loop Filter Time Constant A                       |                           |  |  |  |  |

| LFTC_A   | Bit = 0                                           | Short time constant: 7 µs |  |  |  |  |

| (Bit 20) | Bit = 1                                           | Long time constant: 20 µs |  |  |  |  |

|          | Loop Filter Time Constant B                       |                           |  |  |  |  |

| LFTC_B   | Bit = 0                                           | Short time constant: 7 µs |  |  |  |  |

| (Bit 44) | Bit = 1                                           | Long time constant: 20 µs |  |  |  |  |

|          | Loop Filter Time Constant C1 - Selected when t    | he SEL_CD pin = 0         |  |  |  |  |

| LFTC_C1  | Bit = 0                                           | Short time constant: 7 µs |  |  |  |  |

| (Bit 68) | Bit = 1                                           | Long time constant: 20 µs |  |  |  |  |

|          | Loop Filter Time Constant C2 - Selected when t    | he SEL_CD pin = 1         |  |  |  |  |

| LFTC_C2  | Bit = 0                                           | Short time constant: 7 µs |  |  |  |  |

| (Bit 92) | Bit = 1                                           | Long time constant: 20 µs |  |  |  |  |

|          | Charge Pump A                                     |                           |  |  |  |  |

| CP_A     | Bit = 0                                           | Current = 2 µA            |  |  |  |  |

| (Bit 19) | Bit = 1                                           | Current = 10 µA           |  |  |  |  |

|          | Charge Pump B                                     |                           |  |  |  |  |

| CP_B     | Bit = 0                                           | Current = 2 µA            |  |  |  |  |

| (Bit 43) | Bit = 1                                           | Current = 10 µA           |  |  |  |  |

|          | Charge Pump C1 - Selected when the SEL_CD         | pin = 0                   |  |  |  |  |

| CP_C1    | Bit = 0                                           | Current = 2 µA            |  |  |  |  |

| (Bit 67) | Bit = 1                                           | Current = 10 µA           |  |  |  |  |

|          | Charge Pump C2 - Selected when the SEL_CD pin = 1 |                           |  |  |  |  |

| CP_C2    | Bit = 0                                           | Current = 2 µA            |  |  |  |  |

| (Bit 91) | Bit = 1                                           | Current = 10 µA           |  |  |  |  |

### Table 9: MUX Select Bits

| Name           | Description        | Description                          |                     |  |  |  |  |  |  |  |  |

|----------------|--------------------|--------------------------------------|---------------------|--|--|--|--|--|--|--|--|

|                | MUX A Frequency Se | MUX A Frequency Select               |                     |  |  |  |  |  |  |  |  |

|                | Bit 23             | Bit 22                               |                     |  |  |  |  |  |  |  |  |

| MUX_A[1:0]     | 0                  | 0                                    | Reference frequency |  |  |  |  |  |  |  |  |

| (Bits 23-22)   | 0                  | 1                                    | PLL A frequency     |  |  |  |  |  |  |  |  |

| (Dits 23-22)   | 1                  | 0                                    | PLL B frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 1                                    | PLL C frequency     |  |  |  |  |  |  |  |  |

|                | MUX B Frequency Se | lect                                 |                     |  |  |  |  |  |  |  |  |

|                | Bit 47             | Bit 46                               |                     |  |  |  |  |  |  |  |  |

| MUX_B[1:0]     | 0                  | 0                                    | Reference frequency |  |  |  |  |  |  |  |  |

| (Bits 47-46)   | 0                  | 1                                    | PLL A frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 0                                    | PLL B frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 1                                    | PLL C frequency     |  |  |  |  |  |  |  |  |

|                |                    | elect – Selected when the SEL_CD pir |                     |  |  |  |  |  |  |  |  |

|                | Bit 71             | Bit 70                               | Reference frequency |  |  |  |  |  |  |  |  |

| MUX_C1[1:0]    | 0                  | 0                                    | PLL A frequency     |  |  |  |  |  |  |  |  |

| (Bits 71-70)   | 0                  | 1                                    | PLL B frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 0                                    | PLL C frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 1                                    |                     |  |  |  |  |  |  |  |  |

|                |                    | elect – Selected when the SEL_CD pir | 1 = 1               |  |  |  |  |  |  |  |  |

|                | Bit 125            | Bit 124                              |                     |  |  |  |  |  |  |  |  |

| MUX_C2[1:0]    | 0                  | 0                                    | Reference frequency |  |  |  |  |  |  |  |  |

| (Bits 125-124) | 0                  | 1                                    | PLL A frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 0                                    | PLL B frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 1                                    | PLL C frequency     |  |  |  |  |  |  |  |  |

|                |                    | elect – Selected when the SEL_CD pir | n = 0               |  |  |  |  |  |  |  |  |

|                | Bit 95             | Bit 94                               |                     |  |  |  |  |  |  |  |  |

| MUX_D1[1:0]    | 0                  | 0                                    | Reference frequency |  |  |  |  |  |  |  |  |

| (Bits 95-94)   | 0                  | 1                                    | PLL A frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 0                                    | PLL B frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 1                                    | PLL C frequency     |  |  |  |  |  |  |  |  |

|                |                    | elect – Selected when the SEL_CD pir | 1 = 1               |  |  |  |  |  |  |  |  |

|                | Bit 127            | Bit 126                              |                     |  |  |  |  |  |  |  |  |

| MUX_D2[1:0]    | 0                  | 0                                    | Reference frequency |  |  |  |  |  |  |  |  |

| (Bits 127-126) | 0                  | 1                                    | PLL A frequency     |  |  |  |  |  |  |  |  |

| (              | 1                  | 0                                    | PLL B frequency     |  |  |  |  |  |  |  |  |

|                | 1                  | 1                                    | PLL C frequency     |  |  |  |  |  |  |  |  |

### **10.0 Electrical Specifications**

### Table 10: Absolute Maximum Ratings

| Parameter                                                                         | Symbol          | Min.                 | Max.                 | Units |

|-----------------------------------------------------------------------------------|-----------------|----------------------|----------------------|-------|

| Supply Voltage, dc (V <sub>SS</sub> = ground)                                     | V <sub>DD</sub> | V <sub>SS</sub> -0.5 | 7                    | V     |

| Input Voltage, dc                                                                 | Vi              | V <sub>ss</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                                                                | Vo              | V <sub>ss</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Input Clamp Current, dc (V <sub>1</sub> < 0 or V <sub>1</sub> > V <sub>DD</sub> ) | I <sub>IK</sub> | -50                  | 50                   | mA    |

| Output Clamp Current, dc ( $V_1 < 0$ or $V_1 > V_{DD}$ )                          | I <sub>ок</sub> | -50                  | 50                   | mA    |

| Storage Temperature Range (non-condensing)                                        | Ts              | -65                  | 150                  | °C    |

| Ambient Temperature Range, Under Bias                                             | T <sub>A</sub>  | -55                  | 125                  | °C    |

| Junction Temperature                                                              | TJ              |                      | 150                  | °C    |

| Re-Flow Solder Profile                                                            |                 |                      | 260                  | °C    |

| Input Static Discharge Voltage Protection (MIL-STD 883E, Method 3015.7)           |                 |                      | 2                    | kV    |

Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These conditions represent a stress rating only, and functional operation of the device at these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance, functionality and reliability.

### **CAUTION: ELECTROSTATIC SENSITIVE DEVICE**

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high-energy electrostatic discharge.

#### Table 11: Operating Conditions

| Parameter                           | Symbol           | Conditions/Descriptions   | Min. | Тур. | Max. | Units |

|-------------------------------------|------------------|---------------------------|------|------|------|-------|

| Supply Voltage                      | V                | 5 V ± 10%                 | 4.5  | 5    | 5.5  | V     |

| Supply Voltage                      | V <sub>DD</sub>  | 3.3 V ± 10%               | 3    | 3.3  | 3.6  |       |

| Ambient Operating Temperature Range | T <sub>A</sub>   |                           | 0    |      | 70   | °C    |

| Crystal Resonator Frequency         | f <sub>XIN</sub> |                           | 5    |      | 27   | MHz   |

| Crystal Resonator Load Capacitance  | C <sub>XL</sub>  | Parallel resonant, AT cut |      | 18   |      | pF    |

| Serial Data Transfer Rate           |                  | Standard mode             | 10   |      | 100  | kb/s  |

| Output Driver Load Capacitance      | CL               |                           |      |      | 15   | pF    |

### Table 12: DC Electrical Specifications

| Parameter                            | Symbol                 | Conditions/Description                                                        |                        | Min.                 | Тур.  | Max.                 | Units |

|--------------------------------------|------------------------|-------------------------------------------------------------------------------|------------------------|----------------------|-------|----------------------|-------|

| Overall                              |                        |                                                                               |                        |                      |       |                      |       |

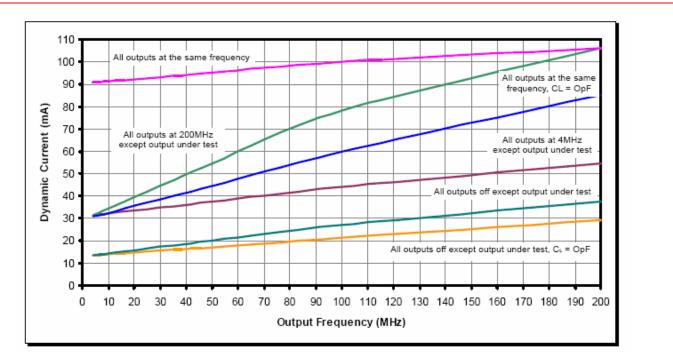

| Supply Current, Dynamic              | I <sub>DD</sub>        | $V_{DD}$ = 5.5V, $f_{CLK}$ = 50MHz ; $C_{I}$<br>See Figure 11 for more inform |                        |                      | 43    |                      | mA    |

| Supply Current, Write                | I <sub>DD(write)</sub> | Additional operating current of EEPROM program mode, V <sub>D</sub>           |                        |                      | 2     |                      | mA    |

| Supply Current, Read                 | I <sub>DD(read)</sub>  | Additional operating current of EEPROM program mode, V <sub>D</sub>           |                        |                      | 1     |                      | mA    |

| Supply Current, Static               | I <sub>DDL</sub>       | $V_{DD}$ = 5.5V, powered down vi                                              | a PD pin               |                      | 0.3   |                      | mA    |

| Dual Function I/O (P                 |                        |                                                                               |                        |                      |       |                      |       |

|                                      |                        |                                                                               | $V_{DD} = 5.5V$        | 3.85                 |       | V <sub>DD</sub> +0.3 |       |

|                                      |                        | Run mode (PD, OE)                                                             | $V_{DD} = 3.6V$        | 2.52                 |       | V <sub>DD</sub> +0.3 |       |

|                                      |                        | Register program mode                                                         | $V_{DD} = 5.5V$        | 3.85                 |       | V <sub>DD</sub> +0.3 |       |

| High-Level Input Voltage             | V <sub>IH</sub>        | (SDA, SCL)                                                                    | $V_{DD} = 3.6V$        | 2.52                 |       | V <sub>DD</sub> +0.3 | V     |

|                                      |                        | EEPROM prodgram mode                                                          | $V_{DD} = 5.5V$        | 3.85                 |       | V <sub>DD</sub> +0.3 |       |

|                                      |                        | (SDA, SCL)                                                                    | $V_{DD} = 3.6V$        | 2.52                 |       | V <sub>DD</sub> +0.3 |       |

|                                      |                        | Run mode (PD, OE)                                                             | $V_{DD} = 5.5V$        | V <sub>ss</sub> -0.3 |       | 1.65                 |       |

|                                      |                        |                                                                               | $V_{DD} = 3.6V$        | V <sub>ss</sub> -0.3 |       | 1.08                 | V     |

|                                      |                        | Register program mode (SDA, SCL)                                              | $V_{DD} = 5.5V$        | V <sub>ss</sub> -0.3 |       | 1.65                 |       |

| Low-Level Input Voltage              | VIL                    |                                                                               | $V_{DD} = 3.6V$        | V <sub>SS</sub> -0.3 |       | 1.08                 |       |

|                                      |                        | EEPROM prodgram mode<br>(SDA, SCL)                                            | V <sub>DD</sub> = 5.5V | V <sub>ss</sub> -0.3 |       | 1.65                 |       |

|                                      |                        |                                                                               | $V_{DD} = 3.6V$        | V <sub>ss</sub> -0.3 |       | 1.08                 |       |

|                                      |                        | Run mode (PD, OE)                                                             | $V_{DD} = 5.5V$        |                      | 2.20  |                      | - V   |

|                                      |                        |                                                                               | $V_{DD} = 3.6V$        |                      | 1.44  |                      |       |

|                                      |                        | V <sub>hys</sub> Register program mode<br>(SDA, SCL)                          | V <sub>DD</sub> = 5.5V |                      | 2.20  |                      |       |

| Hysteresis Voltage                   | V <sub>hys</sub>       |                                                                               | $V_{DD} = 3.6V$        |                      | 1.44  |                      |       |

|                                      |                        | Register program mode                                                         | V <sub>DD</sub> = 5.5V |                      | 0.275 |                      |       |

|                                      |                        | (SDA, SCL)                                                                    | $V_{DD} = 3.6V$        |                      | 0.18  |                      |       |

|                                      |                        | Run/register program mode                                                     | 1                      | -1                   |       | 1                    |       |

| High-Level Input Current             | I <sub>IH</sub>        | EEPROM program mode                                                           |                        | -1                   |       | 1                    | μΑ    |

| Low-Level Input Current (pull-up)    | I <sub>IL</sub>        | $V_{IL} = 0V$                                                                 |                        | -20                  | -36   | -80                  | μA    |

|                                      |                        | Run/register program mode,                                                    | $V_{OL} = 0.4V$        |                      | 26    |                      |       |

| Low-Level Output Sink Current (SDA)  | I <sub>OL</sub>        | EEPROM program mode, Vo                                                       |                        |                      | 3.0   |                      | m/    |

| lode and Frequency Select Inputs (MO | DE, SEL_CD)            |                                                                               |                        | I                    | I     |                      | I     |

|                                      |                        | V <sub>DD</sub> = 5.5 V                                                       |                        | 2.4                  |       | V <sub>DD</sub> +0.3 |       |

| High-Level Input Voltage             | V <sub>IH</sub>        | $V_{DD} = 3.6 \text{ V}$                                                      |                        | 2.0                  |       | V <sub>DD</sub> +0.3 | V     |

|                                      |                        | V <sub>DD</sub> = 5.5 V                                                       |                        | V <sub>SS</sub> -0.3 |       | 0.8                  |       |

| Low-Level Input Voltage              | VIL                    | $V_{DD} = 3.6 \text{ V}$                                                      |                        | V <sub>SS</sub> -0.3 |       | 0.8                  | V     |

| High-Level Input Current             | I <sub>IH</sub>        |                                                                               |                        | -1                   |       | 1                    | μA    |

| Low-Level Input Current (pull-up)    | IL                     |                                                                               |                        | -20                  | -36   | -80                  | μA    |

| Parameter                            | Symbol                 | Conditions/Description                                                        |                        | Min.                 | Туре. | Max.                 | Units |

### Table 12: DC Electrical Specifications (Continued)

| Crystal Oscillator Feedback (XIN)   |                      |                                                                         |     |      |     |    |

|-------------------------------------|----------------------|-------------------------------------------------------------------------|-----|------|-----|----|

| Threshold Bias Voltage              | V <sub>TH</sub>      | $V_{DD} = 5.5 V$                                                        |     | 2.9  |     | V  |

| Theshold blas voltage               | V TH                 | V <sub>DD</sub> = 3.6 V                                                 |     | 1.7  |     | v  |

| High-Level Input Current            | I <sub>IH</sub>      | $V_{DD} = 5.5 V$                                                        |     | 54   |     | mA |

|                                     | ΠΗ                   | $V_{\text{DD}}$ = 5.5 V, oscillator powered down                        | 5   |      | 15  | mA |

| Low-Level Input Current             | IIL                  |                                                                         | -25 | -54  | -75 | μA |

| Crystal Loading Capacitance *       | C <sub>L(xtal)</sub> | As seen by an external crystal connected to XIN and XOUT                |     | 18   |     | pF |

| Input Loading Capacitance *         | C <sub>L(XIN)</sub>  | As seen by an external clock driver on XOUT; XIN unconnected            |     | 36   |     | pF |

| Crystal Oscillator Output (XOUT)    |                      |                                                                         |     |      |     |    |

| High-Level Output Source Current    | I <sub>ОН</sub>      | $V_{DD} = V(XIN) = 5.5 V, V_{O} = 0 V$                                  | 10  | 21   | 30  | mA |

| Low-Level Output Sink Current       | I <sub>OL</sub>      | $V_{DD} = 5.5 \text{ V}, \text{ V}(\text{XIN} = V_{O} = 5.5 \text{ V})$ | -10 | -21  | -30 | mA |

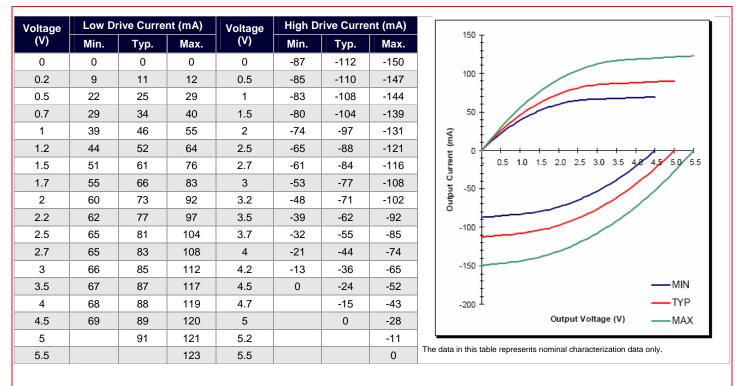

| Clock Outputs (CLK_A, CLK_B, CLK_C, | CLK_D)               |                                                                         |     |      |     |    |

| High-Level Output Source Current    | I <sub>он</sub>      | V <sub>0</sub> = 2.4 V                                                  |     | -125 |     | mA |

| Low-Level Output Sink Current       | I <sub>OL</sub>      | V <sub>0</sub> = 0.4 V                                                  |     | 23   |     | mA |

| Output Impedance                    | Z <sub>OH</sub>      | $V_{\rm O}$ = 0.5 $V_{\rm DD}$ ; output driving high                    |     | 29   |     | Ω  |

| Output impedance                    | Z <sub>OL</sub>      | $V_{\rm O}$ = 0.5 $V_{\rm DD}$ ; output driving low                     |     | 27   |     | 52 |

| Tristate Output Current             | Iz                   |                                                                         | -10 |      | 10  | μA |

| Short Circuit Source Current *      | I <sub>SCH</sub>     | $V_{\text{DD}}$ = 5.5 V , $V_{\text{O}}$ = 0 V; shorted for 30s, max    |     | -150 |     | mA |

| Short Circuit Sink Current *        | I <sub>SCL</sub>     | $V_{DD} = V_O = 5.5 \text{ V}$ ; shorted for 30s, max.                  |     | 123  |     | mA |

Figure 10: CLK\_A, CLK\_B, CLK\_C, CLK\_D Clock Output

Rev. 3 | Page 19 of 28 | www.onsemi.com

V<sub>ID</sub> = 5.0V; Reference Frequency = 27.00MHz; VCO Frequency = 200MHz, C<sub>L</sub> = 17pF except where noted

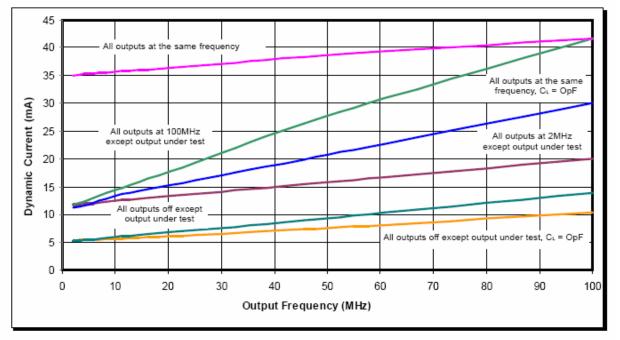

Voo = 3.3V; Reference Frequency = 27.00MHz; VCO Frequency = 100MHz, CL = 17pF except where noted

Figure 11: Dynamic Current vs. Output Frequency

### Table 13: AC Timing Specifications

| Parameter                                | Syn                        | Symbol Conditions/Description Clock (MHz) |                                                                                                                                                                    |        | Min. | Тур. | Max. | Units  |

|------------------------------------------|----------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|--------|

| Overall                                  | I                          |                                           |                                                                                                                                                                    |        |      | 1    |      | 1      |

| EEPROM Write Cycle Time                  | Т                          | wc                                        |                                                                                                                                                                    |        |      |      | 4    | ms     |

| Output Fraguanay *                       |                            |                                           | V <sub>DD</sub> = 5.5 V                                                                                                                                            |        | 0.8  |      | 150  | NAL I- |

| Output Frequency *                       |                            | 0                                         | V <sub>DD</sub> = 3.6 V                                                                                                                                            |        | 0.8  |      | 100  | - MHz  |

|                                          |                            |                                           | V <sub>DD</sub> = 5.5 V                                                                                                                                            |        | 40   |      | 230  |        |

| VCO Frequency *                          | IV                         | со                                        | V <sub>DD</sub> = 3.6 V                                                                                                                                            |        | 40   |      | 170  | MHz    |

| VCO Gain *                               | A                          | /CO                                       |                                                                                                                                                                    |        |      | 400  |      | MHz/   |

| Loop Filter Time Constant *              |                            |                                           | LFTC bit = 0                                                                                                                                                       |        |      | 7    |      |        |

|                                          |                            |                                           | LFTC bit = 1                                                                                                                                                       |        |      | 20   |      | μS     |

| Diao Timo *                              |                            |                                           | $V_{O} = 0.5 \text{ V to } 4.5 \text{ V}; C_{L} = 15 \text{pF}$                                                                                                    |        |      | 2.0  |      |        |

| Rise Time *                              |                            | tr                                        | $V_{O} = 0.3 \text{ V to } 3.0 \text{ V}; C_{L} = 15 \text{pF}$                                                                                                    |        |      | 2.1  |      | - ns   |

| Fall Time *                              |                            |                                           | $V_0 = 4.5 \text{ V to } 0.5 \text{ V}; C_L = 15 \text{pF}$                                                                                                        |        |      | 1.8  |      |        |

| Fall Time *                              |                            | t <sub>f</sub>                            | $V_0 = 3.0 \text{ V}$ to 0.3 V; $C_L = 15 \text{pF}$                                                                                                               |        |      | 1.9  |      | ns     |

| Tristate Enable Delay *                  | t <sub>PZL</sub>           | t <sub>PZH</sub>                          |                                                                                                                                                                    |        | 1    |      | 8    | ns     |

| Tristate Disable Delay *                 | t <sub>PZL</sub>           | t <sub>PZH</sub>                          |                                                                                                                                                                    |        | 1    |      | 8    | ns     |

|                                          |                            |                                           | Output active from power-up, RUN mode via                                                                                                                          | PD pin |      | 100  |      | μs     |

| Clock Stabilization Time *               | on Time * t <sub>STB</sub> |                                           | After last register is written, register program                                                                                                                   | •      |      |      | 1    | ms     |

| Divider Modulus                          |                            |                                           |                                                                                                                                                                    |        |      | I    |      |        |

| Feedback Divider                         | N <sub>F</sub>             | See                                       | also Error! Reference source not found.                                                                                                                            |        | 8    |      | 2047 |        |

| Reference Divider                        | N <sub>R</sub>             |                                           |                                                                                                                                                                    |        | 1    |      | 255  |        |

| Post Divider                             | N <sub>P</sub>             | See                                       | also Error! Reference source not found.                                                                                                                            | 1      |      | 50   |      |        |

| Clock Output (PLL A clock vi             | ia CLK_A pi                | n)                                        |                                                                                                                                                                    |        |      |      |      | ÷      |

| Duty Cycle *                             |                            |                                           | of pulse width (as measured from rising edge to next falling                                                                                                       | 100    | 45   |      | 55   | %      |

|                                          |                            | On ris<br>CL=1                            | at 2.5V) to one clock period<br>ing edges 500µs apart at 2.5V relative to an ideal clock,<br>50F, fXIN=14.318MHz, NF=220, NR=63, NPX=50, no other                  | 100    |      | 45   |      |        |

| Jitter, Long Term ( $\sigma_y(\tau)$ ) * | $T_{j(LT)}$                | On ris<br>CL=1                            | PLLs active On rising edges 500µs apart at 2.5V relative to an ideal clock, CL=15pF, =14.318MHz, NF=220, NR=63, NPX=50, all other 50                               |        |      | 165  |      | ps     |

| Jitter, Period (peak-peak)               |                            | From<br>fXIN=                             | active (B=60MHz, C=40MHz, D=14.318MHz)<br>rising edge to the next rising edge at 2.5V, CL=15pF,<br>14.318MHz, NF=220, NR=63, NPX=50, no other PLLs                 | 100    |      | 110  |      |        |

| *                                        | $t_{j(\Delta P)}$          | fXIN=                                     | rising edge to the next rising edge at 2.5V, CL=15pF,<br>14.318MHz, NF=220, NR=63, NPX=50, all other PLLs<br>(B=60MHz, C=40MHz, D=14.318MHz)                       | 50     |      | 390  |      | - ps   |

| Clock Output (PLL B clock vi             | ia CLK <u>B pi</u>         |                                           |                                                                                                                                                                    |        | I    | I    | I    | 1      |

| Duty Cycle *                             |                            | Ratio                                     | of pulse width (as measured from rising edge to next falling at 2.5V) to one clock period                                                                          | 100    | 45   |      | 55   | %      |

|                                          |                            | On ris<br>CL=1                            | ing edges 500µs apart at 2.5V relative to an ideal clock,<br>5pF, fXIN=14.318MHz, NF=220, NR=63, NPX=50, no other                                                  | 100    |      | 45   |      |        |

| Jitter, Long Term ( $\sigma_y(\tau)$ ) * | T <sub>j(LT)</sub>         | On ris<br>CL=1                            | active<br>ing edges 500µs apart at 2.5V relative to an ideal clock,<br>5pF, =14.318MHz, NF=220, NR=63, NPX=50, all other<br>active (A=50MHz, C=40MHz, D=14.318MHz) | 60     |      | 75   |      | - ps   |

| Jitter, Period (peak-peak)               |                            | From                                      | rising edge to the next rising edge at 2.5V, CL=15pF,<br>14.318MHz, NF=220, NR=63, NPX=50, no other PLLs                                                           | 100    |      | 120  |      |        |

| *                                        | $t_{j(\Delta P)}$          | From<br>fXIN=                             | rising edge to the next rising edge at 2.5V, CL=15pF,<br>14.318MHz, NF=220, NR=63, NPX=50, all other PLLs<br>(A=50MHz, C=40MHz, D=14.318MHz)                       | 60     |      | 400  |      | - ps   |

### Table 13: AC Timing Specifications (Continued)

| Parameter                              |                                                                | Symbol                                                                                                                                         |                      | Conditions/Description                                                                                                                                                                    | Clock<br>(MHz) | Min. | Тур. | Max. | Units |  |