# FS7140-01G-XTD Datasheet

www.digi-electronics.com

| DiGi Electronics Part Number | FS7140-01G-XTD-DG                                                  |

|------------------------------|--------------------------------------------------------------------|

| Manufacturer                 | onsemi                                                             |

| Manufacturer Product Number  | FS7140-01G-XTD                                                     |

| Description                  | IC PLL CLOCK GENERATOR 16SOIC                                      |

| Detailed Description         | PLL Clock Generator IC 400MHz 1 16-SOIC (0.154", 3<br>.90mm Width) |

|                              |                                                                    |

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# Purchase and inquiry

| Manufacturer Product Number:   | Manufacturer:                  |

|--------------------------------|--------------------------------|

| FS7140-01G-XTD                 | onsemi                         |

| Series:                        | Product Status:                |

|                                | Obsolete                       |

| DiGi-Electronics Programmable: | Туре:                          |

| Not Verified                   | PLL Clock Generator            |

| PLL:                           | Input:                         |

| Yes                            | Crystal                        |

| Output:                        | Number of Circuits:            |

| CMOS, PECL                     | -1                             |

| Ratio - Input:Output:          | Differential - Input:Output:   |

| 2:1                            | No/Yes                         |

| Frequency - Max:               | Divider/Multiplier:            |

| 400MHz                         | Yes/No                         |

| Voltage - Supply:              | Operating Temperature:         |

| 3V ~ 3.6V                      | 0°C ~ 70°C                     |

| Mounting Type:                 | Package / Case:                |

| Surface Mount                  | 16-SOIC (0.154", 3.90mm Width) |

| Supplier Device Package:       | Base Product Number:           |

| 16-SOIC                        | FS7140                         |

|                                |                                |

# **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 2 (1 Year)                        |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.39.0001     |                                   |

# Programmable Phase-Locked Loop Clock Generator

#### Description

The FS7140 or FS7145 is a monolithic CMOS clock generator/ regenerator IC designed to minimize cost and component count in a variety of electronic systems. Via the I<sup>2</sup>C-bus interface, the FS7140/45 can be adapted to many clock generation requirements.

The length of the reference and feedback dividers, their fine granularity and the flexibility of the post divider make the FS7140/45 the most flexible stand-alone PLL clock generator available.

#### Features

- Extremely Flexible and Low-jitter Phase Locked Loop (PLL) Frequency Synthesis

- No External Loop Filter Components Needed

- 150 MHz CMOS or 340 MHz PECL Outputs

- Completely Configurable via I<sup>2</sup>C-bus

- Up to Four FS714x can be Used on a Single I<sup>2</sup>C-bus

- 3.3 V Operation

- Independent On-chip Crystal Oscillator and External Reference Input

- Very Low "Cumulative" Jitter

- Pb–Free Packages are Available

#### Applications

- Precision Frequency Synthesis

- Low-frequency Clock Multiplication

- Video Line-locked Clock Generation

- Laser Beam Printers (FS7145)

### **ON Semiconductor®**

http://onsemi.com

01 SUFFIX CASE 751BA

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 17 of this data sheet.

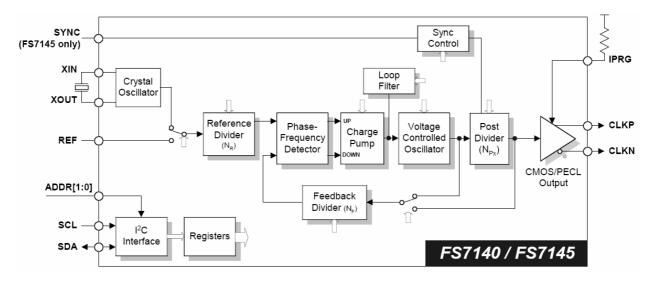

FS7140, FS7145

Figure 1. Device Block Diagram

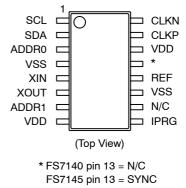

| Pin | Туре                 | Name        | Description                                                       |

|-----|----------------------|-------------|-------------------------------------------------------------------|

| 1   | DI                   | SCL         | Serial interface clock (requires an external pull-up)             |

| 2   | DIO                  | SDA         | Serial interface data input/output (requires an external pull-up) |

| 3   | DI <sub>D</sub>      | ADDR0       | Address select bit "0"                                            |

| 4   | Р                    | VSS         | Ground                                                            |

| 5   | AI                   | XIN         | Crystal oscillator feedback                                       |

| 6   | AO                   | XOUT        | Crystal oscillator drive                                          |

| 7   | DI <sub>D</sub>      | ADDR1       | Address select bit "1"                                            |

| 8   | Р                    | VDD         | Power supply (+3.3 V nominal)                                     |

| 9   | AI                   | IPRG        | PECL current drive programming                                    |

| 10  | -                    | n/c         | No connection                                                     |

| 11  | Р                    | VSS         | Ground                                                            |

| 12  | DIU                  | REF         | Reference frequency input                                         |

| 13  | _<br>DI <sup>U</sup> | n/c<br>SYNC | FS7140 = No connection<br>FS7145 = Synchronization input          |

| 14  | Р                    | VDD         | Power supply (+3.3 V nominal)                                     |

| 15  | DO                   | CLKP        | Clock output                                                      |

| 16  | DO                   | CLKN        | Inverted clock output                                             |

Table 1. PIN DESCRIPTIONS\*

\*Key: Al: Analog Input; AO = Analog Output; DI = Digital Input; DI<sup>U</sup> = Input with Internal Pull–up; DI<sub>D</sub> = Input with Internal Pull–down; DIO = Digital Input/Output; DI–3 = Three–Level Digital Input; DO = Digital Output; P = Power/Ground; # = Active Low Pin

#### **ELECTRICAL SPECIFICATIONS**

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Symbol          | Parameter                                                                         | Min                      | Тур | Мах                   | Units |

|-----------------|-----------------------------------------------------------------------------------|--------------------------|-----|-----------------------|-------|

| $V_{DD}$        | Supply voltage, dc (V <sub>SS</sub> = ground)                                     | V <sub>SS</sub> – 0.5    |     | 4.5                   | V     |

| V <sub>1</sub>  | Input voltage, dc                                                                 | V <sub>SS</sub> – 0.5    |     | V <sub>DD</sub> + 0.5 | V     |

| Vo              | Output voltage, dc                                                                | V <sub>SS</sub> – 0.5    |     | V <sub>DD</sub> + 0.5 | V     |

| I <sub>IK</sub> | Input clamp current, dc (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DD</sub> ) | -50                      |     | 50                    | mA    |

| I <sub>OK</sub> | Output clamp current, dc ( $V_I < 0$ or $V_I > V_{DD}$ )                          | -50                      |     | 50                    | mA    |

| Τ <sub>S</sub>  | Storage temperature range (non-condensing)                                        | -65                      |     | 150                   | °C    |

| T <sub>A</sub>  | Ambient temperature range, under bias                                             | -55                      |     | 125                   | °C    |

| TJ              | Junction temperature                                                              |                          |     | 150                   | °C    |

|                 | Re-flow solder profile                                                            | Per IPC/JEDEC J-STD-020B |     |                       |       |

|                 | Input static discharge voltage protection<br>(MIL-STD 883E, Method 3015.7)        |                          |     | 2                     | kV    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### WARNING: ELECTROSTATIC SENSITIVE DEVICE

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high-energy electrostatic discharge.

#### **Table 3. OPERATING CONDITIONS**

| Symbol          | Parameter                           | Min | Тур | Max | Units |

|-----------------|-------------------------------------|-----|-----|-----|-------|

| V <sub>DD</sub> | Supply voltage                      | 3.0 | 3.3 | 3.6 | V     |

| T <sub>A</sub>  | Ambient operating temperature range | 0   |     | 70  | °C    |

#### FS7140-01G-XTD onsemi IC PLL CLOCK GENERATOR 16SOIC

#### FS7140, FS7145

#### Table 4. DC ELECTRICAL SPECIFICATIONS (Note 1)

| Parameter                             | Symbol               | Conditions/Description                                                                                        | Min                  | Тур                  | Max                 | Units |

|---------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|----------------------|----------------------|---------------------|-------|

| OVERALL                               |                      |                                                                                                               |                      |                      |                     |       |

| Supply current, dynamic               | I <sub>DD</sub>      | CMOS mode; $F_{XTAL}$ = 15 MHz; $F_{VCO}$<br>= 400 MHz; $F_{CLK}$ = 200 MHz; does<br>not include load current |                      | 35                   |                     | mA    |

| Supply current, static                | I <sub>DDL</sub>     | SHUT1, SHUT2 bit both "1"                                                                                     |                      | 400                  | 700                 | μA    |

| SERIAL COMMUNICATION I/O (SDA,        | SCL)                 |                                                                                                               |                      |                      |                     |       |

| High-level input voltage              | V <sub>IH</sub>      |                                                                                                               | 0.8*V <sub>DD</sub>  |                      |                     | V     |

| Low-level input voltage               | V <sub>IL</sub>      |                                                                                                               |                      |                      | 0.2*V <sub>DD</sub> | V     |

| Hysteresis voltage                    | V <sub>hys</sub>     |                                                                                                               |                      | 0.33*V <sub>DD</sub> |                     | V     |

| Input leakage current                 | lı                   | SDA, SCL in read condition                                                                                    | -10                  |                      | +10                 | μΑ    |

| Low-level output sink current (SDA)   | I <sub>OL</sub>      | SDA in acknowledge condition; $V_{SDA} = 0.4 V$                                                               | 5                    | 14                   |                     | mA    |

| ADDRESS SELECT INPUT (ADDRo, ,        | ADDR1)               |                                                                                                               |                      |                      |                     |       |

| High-level input voltage              | V <sub>IH</sub>      |                                                                                                               | V <sub>DD</sub> -1.0 |                      |                     | V     |

| Low-level input voltage               | V <sub>IL</sub>      |                                                                                                               |                      |                      | 0.8                 | V     |

| High-level input current (pull-down)  | I <sub>IH</sub>      | V <sub>ADDRx</sub> = V <sub>DD</sub>                                                                          | 1                    | 30                   |                     | μA    |

| Low-level input current               | ١ <sub>١L</sub>      | V <sub>ADDRx</sub> = 0 V                                                                                      | -1                   |                      | 1                   | μA    |

| REFERENCE FREQUENCY INPUT (F          | IEF)                 |                                                                                                               |                      |                      |                     |       |

| High-level input voltage              | V <sub>IH</sub>      |                                                                                                               | V <sub>DD</sub> -1.0 |                      |                     | V     |

| Low-level input voltage               | V <sub>IL</sub>      |                                                                                                               |                      |                      | 0.8                 | V     |

| High-level input current              | I <sub>IH</sub>      | V <sub>REF</sub> = V <sub>DD</sub>                                                                            | -1                   |                      | 1                   | μΑ    |

| Low-level input current (pull-down)   | Ι <sub>ΙL</sub>      | V <sub>REF</sub> = 0 V                                                                                        |                      | -30                  |                     | μΑ    |

| SYNC CONTROL INPUT (SYNC)             |                      |                                                                                                               |                      |                      |                     |       |

| High-level input voltage              | V <sub>IH</sub>      |                                                                                                               | V <sub>DD</sub> -1.0 |                      |                     | V     |

| Low-level input voltage               | V <sub>IL</sub>      |                                                                                                               |                      |                      | 0.8                 | V     |

| High-level input current              | Ι <sub>ΙΗ</sub>      | V <sub>REF</sub> = V <sub>DD</sub>                                                                            | -1                   |                      | 1                   | μΑ    |

| Low-level input current (pull-down)   | ۱ <sub>IL</sub>      | V <sub>REF</sub> = 0 V                                                                                        |                      | -30                  |                     | μΑ    |

| CRYSTAL OSCILLATOR INPUT (XIN)        |                      |                                                                                                               |                      |                      |                     |       |

| Threshold bias voltage                | V <sub>TH</sub>      |                                                                                                               |                      | V <sub>DD</sub> /2   |                     | V     |

| High-level input current              | Ι <sub>ΙΗ</sub>      | $V_{XIN} = V_{DD}$                                                                                            |                      | 40                   |                     | μA    |

| Low-level input current               | ١ <sub>IL</sub>      | V <sub>XIN</sub> = GND                                                                                        |                      | -40                  |                     | μA    |

| Crystal frequency                     | F <sub>X</sub>       | Fundamental mode                                                                                              |                      |                      | 35                  | MHz   |

| Recommended crystal load capacitance* | C <sub>L(XTAL)</sub> | For best matching with internal crystal oscillator load                                                       |                      | 16–18                |                     | pF    |

| CRYSTAL OSCILLATOR OUTPUT (X          | OUT)                 |                                                                                                               |                      |                      |                     |       |

| High-level output source current      | I <sub>OH</sub>      | V <sub>XOUT</sub> = 0                                                                                         |                      | -8.5                 |                     | mA    |

| Low-level output sink current         | I <sub>OL</sub>      | V <sub>XOUT</sub> = V <sub>DD</sub>                                                                           |                      | 11                   |                     | mA    |

| PECL CURRENT PROGRAM I/O (IPR         | G)                   |                                                                                                               |                      |                      |                     |       |

| Low-level input current               | ۱ <sub>۱L</sub>      | V <sub>IPRG</sub> = 0 V; PECL mode                                                                            | -10                  |                      | 10                  | μΑ    |

| CLOCK OUTPUTS, CMOS MODE (CI          | KN, CLKP)            |                                                                                                               |                      |                      |                     |       |

| High-level output source current      | I <sub>ОН</sub>      | V <sub>O</sub> = 2.0 V                                                                                        |                      | 19                   |                     | mA    |

Unless otherwise stated, V<sub>DD</sub> = 3.3 V ± 10%, no load on any output, and ambient temperature range T<sub>A</sub> = 0°C to 70°C. Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits. MIN and MAX characterization data are ± 3σ from typical. Negative currents indicate flows out of the device.

#### FS7140-01G-XTD onsemi IC PLL CLOCK GENERATOR 16SOIC

#### FS7140, FS7145

#### Table 4. DC ELECTRICAL SPECIFICATIONS (Note 1)

| Parameter                          | Symbol            | <b>Conditions/Description</b>                                                                       | Min | Тур                | Max | Units |

|------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|-----|--------------------|-----|-------|

| CLOCK OUTPUTS, CMOS MODE (C        | CLKN, CLKP)       | -                                                                                                   |     |                    |     |       |

| Low-level output sink current      | I <sub>OL</sub>   | V <sub>O</sub> = 0.4 V                                                                              |     | -35                |     | mA    |

| CLOCK OUTPUTS, PECL MODE (C        | LKN, CLKP)        |                                                                                                     |     |                    |     | -     |

| IPRG bias voltage                  | V <sub>IPRG</sub> | V <sub>IPRG</sub> will be clamped to this level<br>when a resistor is connected from<br>VDD to IPRG |     | V <sub>DD</sub> /3 |     | V     |

| IPRG bias current                  | I <sub>IPRG</sub> | I <sub>IPRG</sub> – (V <sub>VDD</sub> – V <sub>IPRG</sub> ) / R <sub>SET</sub>                      |     |                    | 3.5 | mA    |

| Sink current to IPRG current ratio |                   |                                                                                                     |     | 13                 |     |       |

| Tristate output current            | Ι <sub>Ζ</sub>    |                                                                                                     | -10 |                    | 10  | μA    |

1. Unless otherwise stated,  $V_{DD} = 3.3 V \pm 10\%$ , no load on any output, and ambient temperature range  $T_A = 0^{\circ}C$  to 70°C. Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical. Negative currents indicate flows out of the device.

#### Table 5. AC TIMING SPECIFICATIONS (Note 2)

| Parameter                              | Symbol              | Conditions/Description                                                                                                                                                                   | Min                          | Тур                            | Max                    | Units            |

|----------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------|------------------------|------------------|

| OVERALL                                |                     | -                                                                                                                                                                                        |                              |                                |                        |                  |

| Output frequency*                      | f <sub>o(max)</sub> | CMOS outputs                                                                                                                                                                             | 0                            |                                | 150                    | MHz              |

|                                        |                     | PECL outputs                                                                                                                                                                             | 0                            |                                | 300                    | 1                |

| VCO frequency*                         | f <sub>VCO</sub>    |                                                                                                                                                                                          | 40                           |                                | 400                    | MHz              |

| CMOS mode rise time*                   | t <sub>r</sub>      | C <sub>L</sub> = 7 pF                                                                                                                                                                    |                              | 1                              |                        | ns               |

| CMOS mode fall time*                   | t <sub>f</sub>      | C <sub>L</sub> = 7 pF                                                                                                                                                                    |                              | 1                              |                        | ns               |

| PECL mode rise time*                   | t <sub>r</sub>      | $C_{L} = 7 \text{ pF}; R_{L} = 65 \text{ ohm}$                                                                                                                                           |                              | 1                              |                        | ns               |

| PECL mode fall time*                   | t <sub>f</sub>      | $C_{L} = 7 \text{ pF}; R_{L} = 65 \text{ ohm}$                                                                                                                                           |                              | 1                              |                        | ns               |

| REFERENCE FREQUENCY IN                 | PUT (REF)           |                                                                                                                                                                                          |                              |                                |                        |                  |

| Input frequency                        | F <sub>REF</sub>    |                                                                                                                                                                                          |                              |                                | 80                     | MHz              |

| Reference high time                    | t <sub>REHF</sub>   |                                                                                                                                                                                          | 3                            |                                |                        | ns               |

| Reference low time                     | t <sub>REFL</sub>   |                                                                                                                                                                                          | 3                            |                                |                        | ns               |

| SYNC CONTROL INPUT (SYN                | C)                  |                                                                                                                                                                                          |                              |                                |                        |                  |

| Sync high time                         | t <sub>SYNCH</sub>  | For orderly CLK stop/start                                                                                                                                                               | 3                            |                                |                        | T <sub>CLK</sub> |

| Sync low time t <sub>SYNCL</sub>       |                     | For orderly CLK stop/start                                                                                                                                                               | 3                            |                                |                        |                  |

| CLOCK OUTPUT (CLKN, CLK                | P)                  |                                                                                                                                                                                          |                              |                                |                        |                  |

| Duty cycle (CMOS mode)*                |                     | Measured at 1.4 V                                                                                                                                                                        |                              | 50                             |                        | %                |

| Duty cycle (PECL mode)*                |                     | Measured at zero crossings of<br>(V <sub>CLKP</sub> - V <sub>CLKN</sub> )                                                                                                                |                              | 50                             |                        | %                |

| Jitter, long term $(\sigma_y(\tau))^*$ | t <sub>j(LT)</sub>  | For valid programming solutions. Long-term<br>RMS position error of any edge compared wi<br>the same reference frequency. It is measured<br>ing a 500 microsecond window, using statisti | th an ideal<br>d with a time | clock genera<br>e interval ana | ted from<br>alyzer us- | ps               |

|                                        |                     | FREF/NREF > 1000 kHz                                                                                                                                                                     |                              | 25                             |                        | ps               |

|                                        |                     | FREF/NREF ≅ 500 kHz                                                                                                                                                                      |                              | 50                             |                        | ps               |

|                                        |                     | FREF/NREF ≅ 250 kHz                                                                                                                                                                      |                              | 100                            |                        | ps               |

|                                        |                     | FREF/NREF ≅ 125 kHz                                                                                                                                                                      |                              | 190                            |                        | ps               |

|                                        |                     | FREF/NREF ≅ 62.5 kHz                                                                                                                                                                     |                              | 240                            |                        | ps               |

|                                        |                     | FREF/NREF ≅ 31.5 kHz                                                                                                                                                                     |                              | 300                            |                        | ps               |

| Jitter, period (peak-peak)*            | t <sub>j(ΔP)</sub>  | 40 MHz < VCO frequency < 100 MHz                                                                                                                                                         |                              | 75                             |                        | ps               |

|                                        |                     | VCO frequency > 100 MHz                                                                                                                                                                  |                              | 50                             |                        | ps               |

2. Unless otherwise stated,  $V_{DD} = 3.3 V \pm 10\%$ , no load on any output, and ambient temperature range  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ . Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits. MIN and MAX characterization data are  $\pm 3\sigma$  from typical.

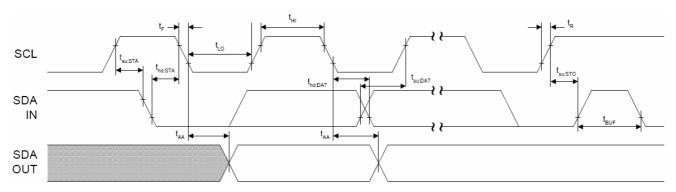

#### Table 6. SERIAL INTERFACE TIMING SPECIFICATIONS (Note 3)

|                                      |                     |                        | Fast Mode |     |       |

|--------------------------------------|---------------------|------------------------|-----------|-----|-------|

| Parameter                            | Symbol              | Conditions/Description | Min       | Max | Units |

| Clock frequency                      | f <sub>SCL</sub>    | SCL                    | 0         | 400 | kHz   |

| Bus free time between STOP and START | t <sub>BUF</sub>    |                        | 1300      |     | ns    |

| Set-up time, START (repeated)        | T <sub>su:STA</sub> |                        | 600       |     | ns    |

| Hold time, START                     | t <sub>hd:STA</sub> |                        | 600       |     | ns    |

| Set-up time, data input              | T <sub>su:DAT</sub> | SDA                    | 100       |     | ns    |

| Hold time, data input                | t <sub>hd:DAT</sub> | SDA                    | 0         |     | ns    |

| Output data valid from clock         | t <sub>AA</sub>     |                        |           | 900 | ns    |

| Rise time, data and clock            | t <sub>R</sub>      | SDA, SCL               |           | 300 | ns    |

| Fall time, data and clock            | t <sub>F</sub>      | SDA, SCL               |           | 300 | ns    |

| High time, clock                     | t <sub>HI</sub>     | SCL                    | 600       |     | ns    |

| Low time, clock                      | t <sub>LO</sub>     | SCL                    | 1300      |     | ns    |

| Set-up time, STOP                    | t <sub>su:STO</sub> |                        | 600       |     | ns    |

Unless otherwise stated, V<sub>DD</sub> = 3.3 V ± 10%, no load on any output, and ambient temperature range T<sub>A</sub> = 0°C to 70°C. Parameters denoted with an asterisk (\*) represent nominal characterization data and are not production tested to any specific limits. MIN and MAX characterization data are ± 3σ from typical.

#### FUNCTIONAL BLOCK DIAGRAM

#### Phase Locked Loop (PLL)

The PLL is a standard phase– and frequency–locked loop architecture. The PLL consists of a reference divider, a phase–frequency detector (PFD), a charge pump, an internal loop filter, a voltage–controlled oscillator (VCO), a feedback divider, and a post divider.

The reference frequency (generated by either the on-board crystal oscillator or an external frequency source), is first reduced by the reference divider. The integer value that the frequency is divided by is called the modulus and is denoted as NR for the reference divider. This divided reference is then fed into the PFD.

The VCO frequency is fed back to the PFD through the feedback divider (the modulus is denoted by NF).

The PFD will drive the VCO up or down in frequency until the divided reference frequency and the divided VCO frequency appearing at the inputs of the PFD are equal. The input/output relationship between the reference frequency and the VCO frequency is then:

$$\frac{f_{\rm VCO}}{\rm N_{\rm F}} = \frac{f_{\rm REF}}{\rm N_{\rm R}}$$

This basic PLL equation can be rewritten as

$$f_{\rm VCO} = f_{\rm REF} \left( \frac{\rm N_F}{\rm N_R} \right)$$

A post divider (actually a series combination of three post dividers) follows the PLL and the final equation for device output frequency is:

$$f_{\mathsf{CLK}} = f_{\mathsf{REF}} \left( \frac{\mathsf{N}_{\mathsf{F}}}{\mathsf{N}_{\mathsf{R}}} \right) \left( \frac{1}{\mathsf{N}_{\mathsf{Px}}} \right)$$

#### **Reference Divider**

The reference divider is designed for low phase jitter. The divider accepts the output of either the crystal oscillator circuit or an external reference frequency. The reference divider is a 12 bit divider, and can be programmed for any modulus from 1 to 4095 (divide by 1 not available on date codes prior to 0108).

#### **Feedback Divider**

The feedback divider is based on a dual-modulus divider (also called dual-modulus prescaler) technique. It permits division by any integer value between 12 and 16383. Simply program the FBKDIV register with the binary equivalent of the desired modulus. Selected moduli below 12 are also permitted. Moduli of: 4, 5, 8, 9, and 10 are also allowed (4 and 5 are not available on date codes prior to 0108).

#### **Post Divider**

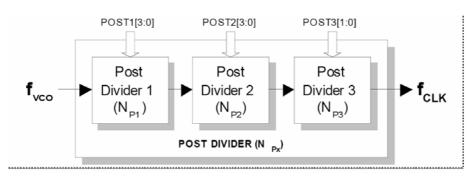

The post divider consists of three individually programmable dividers, as shown in Figure 2.

Figure 2. Post Divider

The moduli of the individual dividers are denoted as  $N_{P1}$ ,  $N_{P2}$  and  $N_{P3}$ , and together they make up the array modulus  $N_{PX}$ .

$N_{PX} = N_{P1} \times N_{P2} \times N_{P3}$

The post divider performs several useful functions. First, it allows the VCO to be operated in a narrower range of speeds compared to the variety of output clock speeds that the device is required to generate. Second, the extra integer in the denominator permits more flexibility in the programming of the loop for many applications where frequencies must be achieved exactly.

Note that a nominal 50/50 duty factor is always preserved (even for selections which have an odd modulus).

See Table 12 for additional information.

#### **Crystal Oscillator**

The FS7140 is equipped with a Pierce-type crystal oscillator. The crystal is operated in parallel resonant mode. Internal load capacitance is provided for the crystal. While a recommended load capacitance for the crystal is specified, crystals for other standard load capacitances may be used if great precision of the reference frequency (100 ppm or less) is not required.

#### **Reference Divider Source MUX**

The source of frequency for the reference divider can be chosen to be the device crystal oscillator or the REF pin by the REFDSRC bit.

When not using the crystal oscillator, it is preferred to connect XIN to VSS. Do not connect to XOUT.

When not using the REF input, it is preferred to leave it floating or connected to  $V_{\text{DD}}$ .

#### Feedback Divider Source MUX

The source of frequency for the feedback divider may be selected to be either the output of the post divider or the output of the VCO by the FBKDSRC bit.

Ordinarily, for frequency synthesis, the output of the VCO is used. Use the output of the post divider only where a deterministic phase relationship between the output clock and reference clock are desired (line–locked mode, for example).

#### **Device Shutdown**

Two bits are provided to effect shutdown of the device if desired, when it is not active. SHUT1 disables most externally observable device functions. SHUT2 reduces device quiescent current to absolute minimum values. Normally, both bits should be set or cleared together.

Serial communications capability is not disabled by either SHUT1 or SHUT2.

#### **Differential Output Stage**

The differential output stage supports both CMOS and pseudo-ECL (PECL) signals. The desired output interface is chosen via the programming registers.

If a PECL interface is used, the transmission line is usually terminated using a Thévenin termination. The output stage can only sink current in the PECL mode, and the amount of sink current is set by a programming resistor on the LOCK/IPRG pin. The ratio of output sink current to IPRG current is 13:1. Source current for the CLKx pins is provided by the pull-up resistors that are part of the Thévenin termination.

#### Example

Assume that it is desired to connect a PECL-type fanout buffer right next to the FS7140.

Further assume:

- V<sub>DD</sub> = 3.3 V

- Desired V<sub>HI</sub> = 2.4 V

- Desired  $V_{LO} = 1.6 V$

- Equivalent  $R_{LOAD} = 75$  ohms

Then:

R1 (from CLKP and CLKN output to VDD) =

$R_{LOAD} * V_{DD} / V_{HI} =$ 75 \* 3.3 / 2.4 = 103 ohms

R2 (from CLKP and CLKN output to GND) =

$R_{LOAD} * V_{DD} / (V_{DD} - V_{HI}) =$ 75 \* 3.3 / (3.3 - 2.4) = 275 ohms

Rprgm (from VDD to IPRG pin) =

26 \* (V<sub>DD</sub> \* R<sub>LOAD</sub>) / (V<sub>HI</sub> - V<sub>LO</sub>) / 3 = 26 \* (3.3 \* 75) / (2.4 - 1.6) / 3 = 2.68 Kohms

#### SYNC Circuitry

The FS7145 supports nearly instantaneous adjustment of the output CLK phase by the SYNC input. Either edge direction of SYNC (positive–going or negative–going) is supported.

Example (positive-going SYNC selected): Upon the negative edge of SYNC input, a sequence begins to stop the CLK output. Upon the positive edge, CLK resumes operation, synchronized to the phase of the SYNC input (plus a deterministic delay). This is performed by control of the device post-divider. Phase resolution equal to 1/2 of the VCO period can be achieved (approximately down to 2 ns).

#### I<sup>2</sup>C-bus Control Interface

This device is a read/write slave device meeting all Philips  $I^2C$ -bus specifications except a "general call." The bus has to be controlled by a master device that generates the serial clock SCL, controls bus access and generates the START and STOP conditions while the device works as a slave. Both master and slave can operate as a transmitter or receiver, but the master device determines which mode is activated. A device that sends data onto the bus is defined as the transmitter, and a device receiving data as the receiver.

I<sup>2</sup>C-bus logic levels noted herein are based on a percentage of the power supply ( $V_{DD}$ ). A logic-one corresponds to a nominal voltage of  $V_{DD}$ , while a logic-zero corresponds to ground ( $V_{SS}$ ).

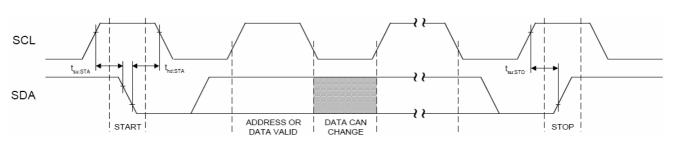

#### **Bus Conditions**

Data transfer on the bus can only be initiated when the bus is not busy. During the data transfer, the data line (SDA) must remain stable whenever the clock line (SCL) is high. Changes in the data line while the clock line is high will be interpreted by the device as a START or STOP condition. The following bus conditions are defined by the I<sup>2</sup>C-bus protocol.

#### Not Busy

Both the data (SDA) and clock (SCL) lines remain high to indicate the bus is not busy.

#### **START Data Transfer**

A high to low transition of the SDA line while the SCL input is high indicates a START condition. All commands to the device must be preceded by a START condition.

#### **STOP Data Transfer**

A low to high transition of the SDA line while SCL input is high indicates a STOP condition. All commands to the device must be followed by a STOP condition.

#### Data Valid

The state of the SDA line represents valid data if the SDA line is stable for the duration of the high period of the SCL line after a START condition occurs. The data on the SDA line must be changed only during the low period of the SCL signal. There is one clock pulse per data bit. Each data transfer is initiated by a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is determined by the master device, and can continue indefinitely. However, data that is overwritten to the device after the first eight bytes will overflow into the first register, then the second, and so on, in a first–in, first–overwritten fashion.

#### Acknowledge

When addressed, the receiving device is required to generate an acknowledge after each byte is received. The master device must generate an extra clock pulse to coincide with the acknowledge bit. The acknowledging device must pull the SDA line low during the high period of the master acknowledge clock pulse. Setup and hold times must be taken into account.

The master must signal an end of data to the slave by not generating and acknowledge bit on the last byte that has been read (clocked) out of the slave. In this case, the slave must leave the SDA line high to enable the master to generate a STOP condition.

#### I<sup>2</sup>C-bus Operation

All programmable registers can be accessed randomly or sequentially via this bi-directional two wire digital interface. The crystal oscillator does not have to run for communication to occur.

The device accepts the following I<sup>2</sup>C–bus commands:

#### **Slave Address**

After generating a START condition, the bus master broadcasts a seven-bit slave address followed by a R/W bit. The address of the device is:

| A6 | A5 | A4 | A3 | A2 | A1 | A0 |

|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 1  | 0  | Х  | х  |

where X is controlled by the logic level at the ADDR pins. The selectable ADDR bits allow four different FS7140 devices to exist on the same bus. Note that every device on an  $I^2C$ -bus must have a unique address to avoid possible bus conflicts.

#### **Random Register Write Procedure**

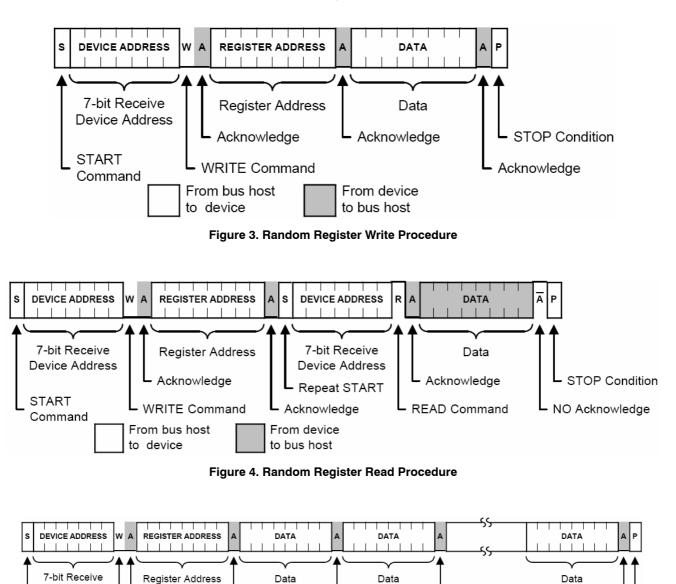

Random write operations allow the master to directly write to any register. To initiate a write procedure, the R/W bit that is transmitted after the seven-bit device address is a logic-low. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is written into the slave's address pointer. Following an acknowledge by the slave, the master is allowed to write eight bits of data into the addressed register. A final acknowledge is returned by the device, and the master generates a STOP condition.

If either a STOP or a repeated START condition occurs during a register write, the data that has been transferred is ignored.

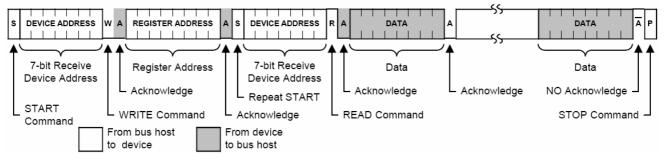

#### **Random Register Read Procedure**

Random read operations allow the master to directly read from any register. To perform a read procedure, the R/W bit that is transmitted after the seven-bit address is a logic-low, as in the register write procedure. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is then written into the slave's address pointer.

Following an acknowledge by the slave, the master generates a repeated START condition. The repeated START terminates the write procedure, but not until after the slave's address pointer is set. The slave address is then resent, with the R/W bit set this time to a logic-high, indicating to the slave that data will be read. The slave will acknowledge the device address, and then transmits the eight-bit word. The master does not acknowledge the transfer but does generate a STOP condition.

#### **Sequential Register Write Procedure**

Sequential write operations allow the master to write to each register in order. The register pointer is automatically incremented after each write. This procedure is more efficient than the random register write if several registers must be written.

To initiate a write procedure, the R/W bit that is transmitted after the seven-bit device address is a logic-low. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is written into the slave's address pointer. Following an acknowledge by the slave, the master is allowed to write up to eight bytes of data into the addressed register before the register address pointer overflows back to the beginning address.

An acknowledge by the device between each byte of data must occur before the next data byte is sent.

Registers are updated every time the device sends an acknowledge to the host. The register update does not wait for the STOP condition to occur. Registers are therefore updated at different times during a sequential register write.

#### Sequential Register Read Procedure

Sequential read operations allow the master to read from each register in order. The register pointer is automatically incremented by one after each read. This procedure is more efficient than the random register read if several registers must be read.

To perform a read procedure, the R/W bit that is transmitted after the seven-bit address is a logic-low, as in the register write procedure. This indicates to the addressed slave device that a register address will follow after the slave device acknowledges its device address. The register address is then written into the slave's address pointer.

Following an acknowledge by the slave, the master generates a repeated START condition. The repeated START terminates the write procedure, but not until after the slave's address pointer is set. The slave address is then resent, with the R/W bit set this time to a logic–high, indicating to the slave that data will be read. The slave will acknowledge the device address, and then transmits all eight bytes of data starting with the initial addressed register. The register address pointer will overflow if the initial register address is larger than zero. After the last byte of data, the master does not acknowledge the transfer but does generate a STOP condition.

FS7140, FS7145

Acknowledge – STOP Command –

Acknowledge

Acknowledge

Acknowledge

From device

to bus host

Device Address

START

Command

Acknowledge

WRITE Command

From bus host

to device

#### **Programming Information**

All register bits are cleared to zero on power-up. All register bits may be read back as written.

#### Table 7. FS7140 REGISTER MAP

| Address | BIT 7                                         | BIT 6                                         | BIT 5                                                  | BIT 4                                                         | BIT 3                                         | BIT 2                                         | BIT 1                                         | BIT 0                                         |

|---------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| Byte 7  | Reserved<br>(Bit 63)<br>Must be set<br>to "0" | Reserved<br>(Bit 62)<br>Must be set<br>to "0" | Reserved<br>(Bit 61)<br>Must be set<br>to "0"          | Reserved<br>(Bit 60)<br>Must be set<br>to "0"                 | Reserved<br>(Bit 59)<br>Must be set<br>to "0" | Reserved<br>(Bit 58)<br>Must be set<br>to "0" | Reserved<br>(Bit 57)<br>Must be set<br>to "0" | Reserved<br>(Bit 56)<br>Must be set<br>to "0" |

| Byte 6  | Reserved<br>(Bit 55)<br>Must be set<br>to "0" | Reserved<br>(Bit 54)<br>Must be set<br>to "0" | SHUT2<br>(Bit 53)<br>0 = Normal<br>1 = Powered<br>down | Reserved<br>(Bit 52)<br>Must be set<br>to "0"                 | Reserved<br>(Bit 51)<br>Must be set<br>to "0" | Reserved<br>(Bit 50)<br>Must be set<br>to "0" | Reserved<br>(Bit 49)<br>Must be set<br>to "0" | Reserved<br>(Bit 48)<br>Must be set<br>to "0" |

| Byte 5  | Reserved<br>(Bit 47)<br>Must be set           | LC<br>(Bit 46)<br>Loop filter                 | LR[1]<br>(Bit 45)                                      | LR[0]<br>(Bit 44)                                             | Reserved<br>(Bit 43)<br>Must be set           | Reserved<br>(Bit 42)<br>Must be set           | CP[1]<br>(Bit 41)                             | CP[0]<br>(Bit 40)                             |

|         | to "0"                                        | cap select                                    | Loop filter re                                         | sistor select                                                 | to "0"                                        | to "0"                                        | Charge pump                                   | current select                                |

| Byte 4  | CMOS<br>(Bit 39)<br>0 = PECL<br>1 = CMOS      | FBKDSRC<br>(Bit 38)<br>0 = VCO<br>output      | FBKDIV[13]<br>(Bit 37)<br>8192                         | FBKDIV[12]<br>(Bit 36)<br>4096                                | FBKDIV[11]<br>(Bit 35)<br>2048                | FBKDIV[10]<br>(Bit 34)<br>1024                | FBKDIV[9]<br>(Bit 33)<br>512                  | FBKDIV[8]<br>(Bit 32)<br>256                  |

|         |                                               | 1 = Post<br>divider output                    | Ş                                                      | See the Feedback Divider section for disallowed FBKDIV values |                                               |                                               |                                               | 3                                             |

| Byte 3  | FBKDIV[7]<br>(Bit 31)<br>128                  | FBKDIV[6]<br>(Bit 30)<br>64                   | FBKDIV[5]<br>(Bit 29)<br>32                            | FBKDIV[4]<br>(Bit 28)<br>16                                   | FBKDIV[3]<br>(Bit 27)<br>8                    | FBKDIV[2]<br>(Bit 26)<br>4                    | FBKDIV[1]<br>(Bit 25)<br>2                    | FBKDIV[0]<br>(Bit 24)<br>1                    |

|         |                                               | Ś                                             | See the Feedba                                         | ck Divider section                                            | on for disallowed                             | FBKDIV values                                 | 6                                             |                                               |

| Byte 2  | POST2[3]<br>(Bit 23)                          | POST2[2]<br>(Bit 22)                          | POST2[1]<br>(Bit 21)                                   | POST2[0]<br>(Bit 20)                                          | POST1[3]<br>(Bit 19)                          | POST1[2]<br>(Bit 18)                          | POST1[1]<br>(Bit 17)                          | POST1[0]<br>(Bit 16)                          |

|         | Modulus = N +                                 | + 1 (N = 0 to 11);                            | See Table 12                                           |                                                               |                                               | Modulus = N +                                 | - 1 (N = 0 to 11);                            | See Table 12                                  |

| Byte 1  | POST3[1]<br>(Bit 15)                          | POST3[0]<br>(Bit 14)                          | SHUT1<br>(Bit 13)<br>0 = Normal                        | REFDSRC<br>(Bit 12)<br>0 = Crystal                            | REFDIV[11]<br>(Bit 11)<br>2048                | REFDIV[10]<br>(Bit 10)<br>1024                | REFDIV[9]<br>(Bit 9)<br>512                   | REFDIV[8]<br>(Bit 8)<br>256                   |

|         |                                               |                                               | 1 = Powered<br>down                                    | oscillator<br>1 = REF pin                                     | 2040                                          | 1024                                          | 512                                           | 230                                           |

| Byte 0  | REFDIV[7]<br>(Bit 7)<br>128                   | REFDIV[6]<br>(Bit 6)<br>64                    | REFDIV[5]<br>(Bit 5)<br>32                             | REFDIV[4]<br>(Bit 4)<br>16                                    | REFDIV[3]<br>(Bit 3)<br>8                     | REFDIV[2]<br>(Bit 2)<br>4                     | REFDIV[1]<br>(Bit 1)<br>2                     | REFDIV[0]<br>(Bit 0)<br>1                     |

#### Table 8. FS7145 REGISTER MAP

| Address | BIT 7                                         | BIT 6                                         | BIT 5                                                  | BIT 4                                                         | BIT 3                                         | BIT 2                                         | BIT 1                                                   | BIT 0                                                  |

|---------|-----------------------------------------------|-----------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| Byte 7  | Reserved<br>(Bit 63)<br>Must be set<br>to "0" | Reserved<br>(Bit 62)<br>Must be set<br>to "0" | Reserved<br>(Bit 61)<br>Must be set<br>to "0"          | Reserved<br>(Bit 60)<br>Must be set<br>to "0"                 | Reserved<br>(Bit 59)<br>Must be set<br>to "0" | Reserved<br>(Bit 58)<br>Must be set<br>to "0" | Reserved<br>(Bit 57)<br>Must be set<br>to "0"           | Reserved<br>(Bit 56)<br>Must be set<br>to "0"          |

| Byte 6  | Reserved<br>(Bit 55)<br>Must be set<br>to "0" | Reserved<br>(Bit 54)<br>Must be set<br>to "0" | SHUT2<br>(Bit 53)<br>0 = Normal<br>1 = Powered<br>down | Reserved<br>(Bit 52)<br>Must be set<br>to "0"                 | Reserved<br>(Bit 51)<br>Must be set<br>to "0" | Reserved<br>(Bit 50)<br>Must be set<br>to "0" | SYNCPOL<br>(Bit 49)<br>"0" = negative<br>"1" = positive | SYNCEN<br>(Bit 48)<br>"0" = negative<br>"1" = positive |

| Byte 5  | Reserved<br>(Bit 47)<br>Must be set           | LC<br>(Bit 46)<br>Loop filter                 | LR[1]<br>(Bit 45)                                      | LR[0]<br>(Bit 44)                                             | Reserved<br>(Bit 43)<br>Must be set           | Reserved<br>(Bit 42)<br>Must be set           | CP[1]<br>(Bit 41)                                       | CP[0]<br>(Bit 40)                                      |

|         | to "0"                                        | cap select                                    | Loop filter re                                         | sistor select                                                 | to "0"                                        | to "0"                                        | Charge pump current select                              |                                                        |

| Byte 4  | CMOS<br>(Bit 39)<br>0 = PECL<br>1 = CMOS      | FBKDSRC<br>(Bit 38)<br>0 = VCO<br>output      | FBKDIV[13]<br>(Bit 37)<br>8192                         | FBKDIV[12]<br>(Bit 36)<br>4096                                | FBKDIV[11]<br>(Bit 35)<br>2048                | FBKDIV[10]<br>(Bit 34)<br>1024                | FBKDIV[9]<br>(Bit 33)<br>512                            | FBKDIV[8]<br>(Bit 32)<br>256                           |

|         |                                               | 1 = Post<br>divider output                    | ŝ                                                      | See the Feedback Divider section for disallowed FBKDIV values |                                               |                                               |                                                         |                                                        |

| Byte 3  | FBKDIV[7]<br>(Bit 31)<br>128                  | FBKDIV[6]<br>(Bit 30)<br>64                   | FBKDIV[5]<br>(Bit 29)<br>32                            | FBKDIV[4]<br>(Bit 28)<br>16                                   | FBKDIV[3]<br>(Bit 27)<br>8                    | FBKDIV[2]<br>(Bit 26)<br>4                    | FBKDIV[1]<br>(Bit 25)<br>2                              | FBKDIV[0]<br>(Bit 24)<br>1                             |

|         |                                               | ę                                             | See the Feedba                                         | ck Divider section                                            | on for disallowed                             | FBKDIV values                                 | 6                                                       |                                                        |

| Byte 2  | POST2[3]<br>(Bit 23)                          | POST2[2]<br>(Bit 22)                          | POST2[1]<br>(Bit 21)                                   | POST2[0]<br>(Bit 20)                                          | POST1[3]<br>(Bit 19)                          | POST1[2]<br>(Bit 18)                          | POST1[1]<br>(Bit 17)                                    | POST1[0]<br>(Bit 16)                                   |

|         | Modulus = N +                                 | + 1 (N = 0 to 11);                            | See Table 12                                           |                                                               |                                               | Modulus = N +                                 | - 1 (N = 0 to 11)                                       | ; See Table 12                                         |

| Byte 1  | POST3[1]<br>(Bit 15)                          | POST3[0]<br>(Bit 14)                          | SHUT1<br>(Bit 13)<br>0 = Normal                        | REFDSRC<br>(Bit 12)<br>0 = Crystal                            | REFDIV[11]<br>(Bit 11)<br>2048                | REFDIV[10]<br>(Bit 10)<br>1024                | REFDIV[9]<br>(Bit 9)<br>512                             | REFDIV[8]<br>(Bit 8)<br>256                            |

|         |                                               | 1, 2, 4 or 8;<br>able 12                      | 1 = Powered<br>down                                    | oscillator<br>1 = REF pin                                     | 2040                                          | 1024                                          | 512                                                     | 230                                                    |

| Byte 0  | REFDIV[7]<br>(Bit 7)<br>128                   | REFDIV[6]<br>(Bit 6)<br>64                    | REFDIV[5]<br>(Bit 5)<br>32                             | REFDIV[4]<br>(Bit 4)<br>16                                    | REFDIV[3]<br>(Bit 3)<br>8                     | REFDIV[2]<br>(Bit 2)<br>4                     | REFDIV[1]<br>(Bit 1)<br>2                               | REFDIV[0]<br>(Bit 0)<br>1                              |

#### Table 9. DEVICE CONFIGURATION BITS

| Name    | Description                                  |  |

|---------|----------------------------------------------|--|

| REFDSRC | Reference divider source                     |  |

|         | [0] = crystal oscillator / [1] = REF pin     |  |

| FBKDSRC | Feedback divider source                      |  |

|         | [0] = VCO output / [1] = post divider output |  |

| SHUT1   | Shutdown1                                    |  |

|         | [0] = normal / [1] = powered down            |  |

| SHUT2   | Shutdown2                                    |  |

|         | [0] = normal / [1] = powered down            |  |

| CMOS    | CLKP/CLKN output mode                        |  |

|         | [0] = PECL output / [1] CMOS output          |  |

#### Table 10. MAIN LOOP TUNING BITS

| Name    | Description                  |         |  |

|---------|------------------------------|---------|--|

| CP[1:0] | Charge pump current          |         |  |

|         | [00]                         | 2.0 μΑ  |  |

|         | [01]                         | 4.5 μΑ  |  |

|         | [10]                         | 11.0 μA |  |

|         | [11]                         | 22.5 μΑ |  |

| LR[1:0] | Loop filter resistor select  |         |  |

|         | [00]                         | 400 ΚΩ  |  |

|         | [01]                         | 133 ΚΩ  |  |

|         | [10]                         | 30 KΩ   |  |

|         | [11]                         | 12 KΩ   |  |

| LC      | Loop filter capacitor select |         |  |

|         | [0]                          | 185 pF  |  |

|         | [1]                          | 500 pF  |  |

#### Table 11. PLL DIVIDER CONTROL BITS

| Name         | Description                         |

|--------------|-------------------------------------|

| REFDIV[11:0] | Reference divider (N <sub>R</sub> ) |

| FBKDIV[13:0] | Feedback divider (N <sub>R</sub> )  |

#### Table 12. SYNC CONTROL BITS (FS7145 only)

| Name                  | Description                               |  |  |

|-----------------------|-------------------------------------------|--|--|

| SYNCEN                | Sync enable                               |  |  |

|                       | [0] = disabled / [1] = enabled            |  |  |

| SYNCPOL Sync polarity |                                           |  |  |

|                       | [0] = negative edge / [1] = positive edge |  |  |

#### Table 13. POST DIVIDER CONTROL BITS

| Name       | Description                                |            |  |  |

|------------|--------------------------------------------|------------|--|--|

| POST1[3:0] | Post divider #1 (N <sub>P1</sub> ) modulus |            |  |  |

|            | [0000]                                     | 1          |  |  |

|            | [0001]                                     | 2          |  |  |

|            | [0010]                                     | 3          |  |  |

|            | [0011]                                     | 4          |  |  |

|            | [0100]                                     | 5          |  |  |

|            | [0101]                                     | 6          |  |  |

|            | [0110]                                     | 7          |  |  |

|            | [0111]                                     | 8          |  |  |

|            | [1000]                                     | 9          |  |  |

|            | [1001]                                     | 10         |  |  |

|            | [1010]                                     | 11         |  |  |

|            | [1011]                                     | 12         |  |  |

|            | [1100]                                     | Do not use |  |  |

|            | [1101]                                     |            |  |  |

|            | [1110]                                     |            |  |  |

|            | [1111]                                     |            |  |  |

| POST2[3:0] | Post divider #2 (N <sub>P2</sub> ) modulus |            |  |  |

|            | [0000]                                     | 1          |  |  |

|            | [0001]                                     | 2          |  |  |

|            | [0010]                                     | 3          |  |  |

|            | [0011]                                     | 4          |  |  |

|            | [0100]                                     | 5          |  |  |

|            | [0101]                                     | 6          |  |  |

|            | [0110]                                     | 7          |  |  |

|            | [0111]                                     | 8          |  |  |

|            | [1000]                                     | 9          |  |  |

|            | [1001]                                     | 10         |  |  |

|            | [1010]                                     | 11         |  |  |

|            | [1011]                                     | 12         |  |  |

|            | [1100]                                     | Do not use |  |  |

|            | [1101]                                     |            |  |  |

|            | [1110]                                     |            |  |  |

|            | [1111]                                     |            |  |  |

| POST3[1:0] | Post divider #3 (N <sub>P3</sub> ) m       | nodulus    |  |  |

|            | [00]                                       | 1          |  |  |

|            | [01]                                       | 2          |  |  |

|            | [10]                                       | 4          |  |  |

|            | [11]                                       | 8          |  |  |

Figure 7. Bus Timing Data

Figure 8. Data Transfer Sequence

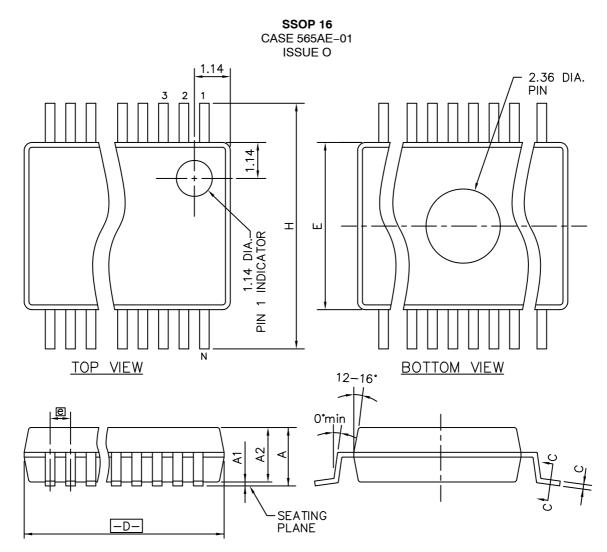

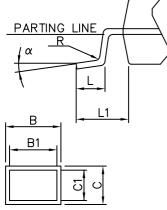

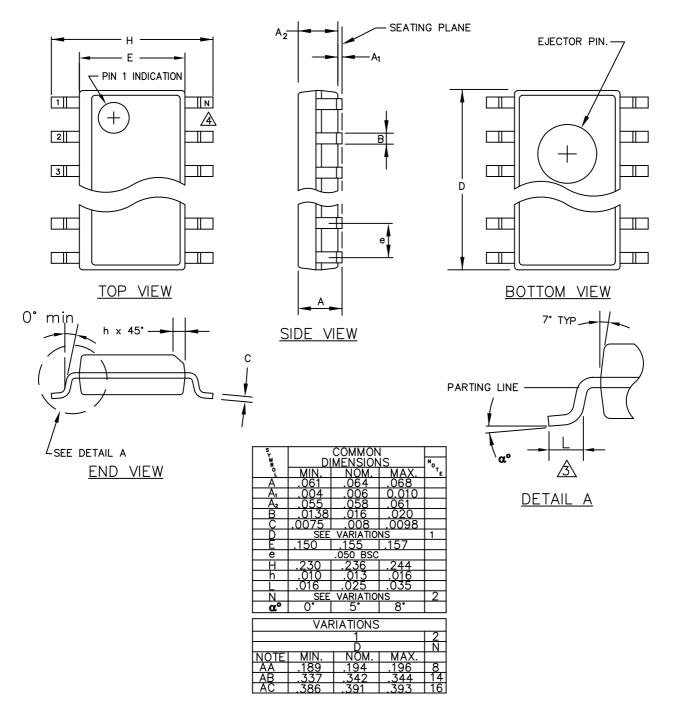

#### PACKAGE DIMENSIONS

SECTION C-C

|             |              |          | TABLI | E IN             | MILL     |

|-------------|--------------|----------|-------|------------------|----------|

| S<br>Y MBOL |              | COMMON   |       |                  | NO.      |

| N.          | D            | MENSION  | IS    | No <sub>te</sub> | VAF      |

| Ľ           | MIN.         | NOM.     | MAX.  | 'ε               |          |

| Α           | 1.73         | 1.86     | 1.99  |                  |          |

| Aı          | 0.05         | 0.13     | 0.21  |                  | A        |

| A₂          | 1.68         | 1.73     | 1.78  |                  | A        |

| В           | 0.25         |          | 0.38  |                  | A<br>A   |

| B1          | 0.25         | 0.30     | 0.33  |                  | A        |

| С           | 0.09         |          | 0.20  |                  | A        |

| C1          | 0.09         | 0.15     | 0.16  |                  | A        |

| D           | SEE          | VARIATIO |       | 1                |          |

| E           | 5.20         | 5.30     | 5.38  |                  |          |

| е           |              | 0.65 BSC |       |                  |          |

| Н           | 7.65<br>0.63 | 7.80     | 7.90  |                  |          |

| L           | 0.63         | 0.75     | 0.95  |                  |          |

| L1          |              | 1.25 R   | EF.   |                  | <u>N</u> |

| Ν           | SEE          | VARIATIO |       | 2                |          |

| α           | 0.           | 4°       | 8.    |                  |          |

| R           | 0.09         | 0.15     | -     |                  |          |

|             |              |          |       |                  |          |

#### LIMETERS

| NOTE   |                                            | 1     |                                       | 2                                          |

|--------|--------------------------------------------|-------|---------------------------------------|--------------------------------------------|

| VARI-  |                                            | D     |                                       | N                                          |

| ATIONS | MIN.                                       | NOM.  | MAX.                                  |                                            |

|        | 2.87                                       | 3.00  | 3.13                                  | 8                                          |

| AA     | 6.07                                       | 6.20  | 6.33                                  | 14                                         |

| AB     | 6.07                                       | 6.20  | 6.33                                  | 16                                         |

| AC     | 7.07                                       | 7.20  | 7.33                                  | 20                                         |

| AD     | 8.07                                       | 8.20  | 8.33                                  | 24                                         |

| AĒ     | 10.07                                      | 10.20 | 10.33                                 | 28                                         |

| AF     | 10.07                                      | 10.20 | 10.33                                 | 30                                         |

|        | ATIONS<br>AA<br>AB<br>AC<br>AD<br>AE<br>AF |       | NOTE 1<br>VARI- D<br>ATIONS MIN. NOM. | NOTE 1<br>VARI- D<br>ATIONS MIN. NOM. MAX. |

#### NOTE: MOLD FLASH OR PROTRUSIONS SHALL

NOT EXCEED 0.20mm on D PER SIDE.

#### PACKAGE DIMENSIONS

SOIC 16 CASE 751BA-01 ISSUE O

#### FS7140-01G-XTD onsemi IC PLL CLOCK GENERATOR 16SOIC

#### FS7140, FS7145

| Part Number    | Package                                                | Shipping Configuration | Temperature Range        |

|----------------|--------------------------------------------------------|------------------------|--------------------------|

| FS7145-01-XTD  | 16-pin (0.150") SOIC                                   | Tube/Tray              | 0°C to 70°C (commercial) |

| FS7145-01-XTP  | 16-pin (0.150") SOIC                                   | Tape & Reel            | 0°C to 70°C (commercial) |

| FS7140-02G-XTD | 16-pin (5.3 mm) SSOP<br>'Green' or lead-free packaging | Tube/Tray              | 0°C to 70°C (commercial) |

| FS7140-02G-XTP | 16-pin (5.3 mm) SSOP<br>'Green' or lead-free packaging | Tape & Reel            | 0°C to 70°C (commercial) |

| FS7140-01G-XTD | 16-pin (0.150") SOIC<br>'Green' or lead-free packaging | Tube/Tray              | 0°C to 70°C (commercial) |

| FS7140-01G-XTP | 16-pin (0.150") SOIC<br>'Green' or lead-free packaging | Tape & Reel            | 0°C to 70°C (commercial) |

| FS7145-02G-XTD | 16-pin (5.3 mm) SSOP<br>'Green' or lead-free packaging | Tube/Tray              | 0°C to 70°C (commercial) |

| FS7145-02G-XTP | 16-pin (5.3 mm) SSOP<br>'Green' or lead-free packaging | Tape & Reel            | 0°C to 70°C (commercial) |

#### **Table 14. ORDERING INFORMATION**

ON Semiconductor is licensed by Philips Corporation to carry the I<sup>2</sup>C protocol.

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agsociated with such unintended or unauthorized use payers that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit//Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

#### ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com