# MCK12140DR2G Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number MCK12140DR2G-DG

Manufacturer onsemi

Manufacturer Product Number MCK12140DR2G

Description IC FREQUENCY DETECTOR 8SOIC

Detailed Description Phase Frequency Detector IC 800MHz 1 8-SOIC (0.1

54", 3.90mm Width)

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# **Purchase and inquiry**

| Manufacturer Product Number:   | Manufacturer:                 |

|--------------------------------|-------------------------------|

| MCK12140DR2G                   | onsemi                        |

| Series:                        | Product Status:               |

|                                | Active                        |

| DiGi-Electronics Programmable: | Type:                         |

| Not Verified                   | Phase Frequency Detector      |

| PLL:                           | Input:                        |

| No                             | ECL                           |

| Output:                        | Number of Circuits:           |

| ECL                            | 1                             |

| Ratio - Input:Output:          | Differential - Input:Output:  |

| 2:2                            | No/Yes                        |

| Frequency - Max:               | Divider/Multiplier:           |

| 800MHz                         | No/No                         |

| Voltage - Supply:              | Operating Temperature:        |

| 4.75V ~ 5.5V                   | -40°C ~ 70°C                  |

| Mounting Type:                 | Package / Case:               |

| Surface Mount                  | 8-SOIC (0.154", 3.90mm Width) |

| Supplier Device Package:       | Base Product Number:          |

| 8-SOIC                         | MCK12140                      |

# **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

8542.39.0001

# **Phase-Frequency Detector** MCH12140, MCK12140

#### Description

The MCH/K12140 is a phase frequency-detector intended for phase-locked loop applications which require a minimum amount of phase and frequency difference at lock. When used in conjunction with high performance VCO such as the MC100EL1648, a high bandwidth PLL can be realized. The device is functionally compatible with the MC12040 phase-frequency detector with the maximum frequency extending to 800 MHz.

When the Reference (R) and VCO (V) inputs are unequal in frequency and/or phase, the differential UP (U) and DOWN (D) outputs will provide pulse streams which when subtracted and integrated provide an error voltage for control of a VCO. See AND8040 for further information. The device is packaged in a small outline, surface mount 8-lead SOIC package. There are two versions of the device to provide I/O compatibility to the two existing ECL standards. The MCH12140 is compatible with MECL™ 10H logic levels while the MCK12140 is compatible to 100 K ECL logic levels. This device can also be used in +5.0 V systems. See AND8020 for termination information

#### **Features**

- 800 MHz Typical Bandwidth

- Small Outline 8-Lead SOIC Package

- 75 kΩ Internal Input Pulldown Resistors

- >1000 V ESD Protection

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant

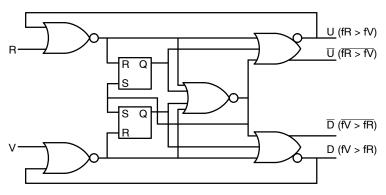

Figure 1. Logic Diagram

For proper operation, the input edge rate of the R and V inputs should be less than 5.0 ns.

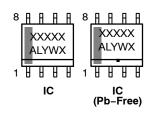

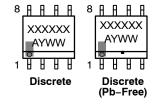

#### **MARKING DIAGRAM**

Х = H or K

= Assembly Location Α

= Wafer Lot = Year W = Work Week

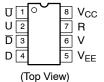

#### **PIN CONNECTIONS**

= Pb-Free Package

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| MCK12140DG   | SOIC-8<br>(Pb-Free) | 98 Units / Tube       |

| MCK12140DR2G | SOIC-8<br>(Pb-Free) | 2500 /<br>Tape & Reel |

#### **DISCONTINUED** (Note 1)

| MCH12140DG |           | 98 Units / Tube |

|------------|-----------|-----------------|

|            | (Pb-Free) |                 |

- †For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

- 1. DISCONTINUED: This device is not recommended for new design. Please contact your **onsemi** representative for information. The most current information on this device may be available on www.onsemi.com.

1

#### MCH12140, MCK12140

Table 1. TRUTH TABLE\*

| Inj              | out              |                  | Out              | put              |             | Inp         | out              | Output      |                  |             |                  |

|------------------|------------------|------------------|------------------|------------------|-------------|-------------|------------------|-------------|------------------|-------------|------------------|

| R                | V                | U                | D                | U                | D           | R           | V                | U           | D                | U           | D                |

| 0<br>0<br>1<br>0 | 0<br>1<br>1      | X<br>X<br>X      | X<br>X<br>X      | X<br>X<br>X      | X<br>X<br>X | 1<br>1<br>1 | 1<br>0<br>1<br>0 | 0<br>0<br>0 | 0<br>0<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>0<br>0 |

| 1<br>0<br>1<br>1 | 1<br>1<br>1<br>0 | 1<br>1<br>1<br>1 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 1<br>1<br>1 | 1<br>0<br>1 | 1<br>1<br>1      | 0<br>0<br>0 | 1<br>1<br>0      | 1<br>1<br>1 | 0<br>0<br>1      |

<sup>\*</sup>This is not strictly a functional table; i.e., it does not cover all possible modes of operation. However, it gives a sufficient number of tests to ensure that the device will function properly.

$\textbf{Table 2. H-SERIES DC CHARACTERISTICS} \ (V_{EE} = V_{EE}(min) - V_{EE}(max); \ V_{CC} = GND \ (Note \ 2), \ unless \ otherwise \ noted.)$

|                 |                     | −40°C |       | 0°C   |       | 25°C  |       | 70    |       |      |

|-----------------|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic      | Min   | Max   | Min   | Max   | Min   | Max   | Min   | Max   | Unit |

| V <sub>OH</sub> | Output HIGH Voltage | -1080 | -890  | -1020 | -840  | -980  | -810  | -910  | -720  | mV   |

| V <sub>OL</sub> | Output LOW Voltage  | -1950 | -1650 | -1950 | -1630 | -1950 | -1630 | -1950 | -1595 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage  | -1230 | -890  | -1170 | -840  | -1130 | -810  | -1060 | -720  | mV   |

| V <sub>IL</sub> | Input LOW Voltage   | -1950 | -1500 | -1950 | -1480 | -1950 | -1480 | -1950 | -1445 | mV   |

| I <sub>IL</sub> | Input LOW Current   | 0.5   | -     | 0.5   | _     | 0.5   | -     | 0.3   | _     | μΑ   |

$\textbf{Table 3. K-SERIES DC CHARACTERISTICS} \ (V_{EE} = V_{EE}(min) - V_{EE}(max); \ V_{CC} = GND \ (Note \ 3), \ unless \ otherwise \ noted.)$

|                  |                     | −40°C |       |       | (     | )°C to 70°C | ;     |                                         |      |

|------------------|---------------------|-------|-------|-------|-------|-------------|-------|-----------------------------------------|------|

| Symbol           | Characteristic      | Min   | Тур   | Max   | Min   | Тур         | Max   | Condition                               | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage | -1085 | -1005 | -880  | -1025 | -955        | -880  | V <sub>IN</sub> = V <sub>IH</sub> (max) | mV   |

| V <sub>OL</sub>  | Output LOW Voltage  | -1830 | -1695 | -1555 | -1810 | -1705       | -1620 | or V <sub>IL</sub> (min)                | mV   |

| V <sub>OHA</sub> | Output HIGH Voltage | -1095 | _     | _     | -1035 | _           | -     | $V_{IN} = V_{IH}(min)$                  | mV   |

| V <sub>OLA</sub> | Output LOW Voltage  | _     | _     | -1555 | _     | _           | -1610 | or V <sub>IL</sub> (max)                | mV   |

| V <sub>IH</sub>  | Input HIGH Voltage  | -1165 | _     | -880  | -1165 | _           | -880  | -                                       | mV   |

| V <sub>IL</sub>  | Input LOW Voltage   | -1810 | _     | -1475 | -1810 | _           | -1475 | -                                       | mV   |

| I <sub>IL</sub>  | Input LOW Current   | 0.5   | -     | _     | 0.5   | -           | -     | $V_{IN} = V_{IL}(max)$                  | μΑ   |

#### MCH12140, MCK12140

**Table 4. MAXIMUM RATINGS**

| Symbol           | Rating                                |                     | Value        | Unit |

|------------------|---------------------------------------|---------------------|--------------|------|

| $V_{EE}$         | Power Supply (V <sub>CC</sub> = 0 V)  |                     | -8.0 to 0    | VDC  |

| V <sub>I</sub>   | Input Voltage (V <sub>CC</sub> = 0 V) |                     | 0 to −6.0    | VDC  |

| l <sub>out</sub> | Output Current                        | Continuous<br>Surge | 50<br>100    | mA   |

| T <sub>A</sub>   | Operating Temperature Range           |                     | -40 to +70   | °C   |

| V <sub>EE</sub>  | Operating Range (Note 4)              |                     | −5.7 to −4.2 | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

NOTE: ESD data available upon request.

- 2. 10H circuits are designed to meet the DC specifications shown in the table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained. Outputs are terminated through a 50 Ω resistor to -2.0 V except where otherwise specified on the individual data sheets.

- 3. This table replaces the three tables traditionally seen in ECL 100 K data books. The same DC parameter values at V<sub>EE</sub> = -4.5 V now apply across the full V<sub>EE</sub> range of -4.2 V to -5.5 V. Outputs are terminated through a 50 Ω resistor to -2.0 V except where otherwise specified on the individual data sheets.

- 4. Parametric values specified at: H-Series: -4.20 V to -5.50 V

K-Series: -4.94 V to -5.50 V

Table 5. DC CHARACTERISTICS ( $V_{EE} = V_{EE}(min) - V_{EE}(max)$ ;  $V_{CC} = GND$ , unless otherwise noted.)

|                 |                      |        | −40°C          |              | 0°C          |                |              | 25°C         |                |              | 70°C         |                |              |              |      |

|-----------------|----------------------|--------|----------------|--------------|--------------|----------------|--------------|--------------|----------------|--------------|--------------|----------------|--------------|--------------|------|

| Symbol          | Characteristic       |        | Min            | Тур          | Max          | Unit |

| I <sub>EE</sub> | Power Supply Current | H<br>K | 1              | 45<br>45     | -            | 38<br>38       | 45<br>45     | 52<br>52     | 38<br>38       | 45<br>45     | 52<br>52     | 38<br>42       | 45<br>50     | 52<br>58     | mA   |

| V <sub>EE</sub> | Power Supply Voltage | H<br>K | -4.75<br>-4.20 | -5.2<br>-4.5 | -5.5<br>-5.5 | V    |

| I <sub>IH</sub> | Input HIGH Current   |        | -              | -            | 150          | -              | -            | 150          | -              | -            | 150          | -              | -            | 150          | μΑ   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

Table 6. AC CHARACTERISTICS (VEE = VEE(min) - VEE(max); VCC = GND, unless otherwise noted.)

|                                      |                                             | -40°C |     | 0°C |     | 25°C |     |     | 70°C |     |     |     |     |      |

|--------------------------------------|---------------------------------------------|-------|-----|-----|-----|------|-----|-----|------|-----|-----|-----|-----|------|

| Symbol                               | Characteristic                              | Min   | Тур | Max | Min | Тур  | Max | Min | Тур  | Max | Min | Тур | Max | Unit |

| F <sub>MAX</sub>                     | Maximum Toggle Frequency                    | _     | 800 | -   | 650 | 800  | _   | 650 | 800  | -   | 650 | 800 | _   | -    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay-to-Output<br>R, V to D, U | 250   | 375 | 500 | 250 | 375  | 500 | 250 | 375  | 500 | 250 | 375 | 500 | ps   |

| t <sub>r</sub><br>t <sub>f</sub>     | Output Rise/Fall Times<br>Q (20 to 80%)     | -     | 225 | -   | 100 | 225  | 350 | 100 | 225  | 350 | 100 | 225 | 350 | ps   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

#### MCH12140, MCK12140

#### **APPLICATIONS INFORMATION**

The 12140 is a high speed digital circuit used as a phase comparator in an analog phase-locked loop. The device determines the "lead" or "lag" phase relationship and time difference between the leading edges of a VCO (V) signal and a Reference (R) input. Since these edges occur only once per cycle, the detector has a range of  $\pm 2\pi$  radians.

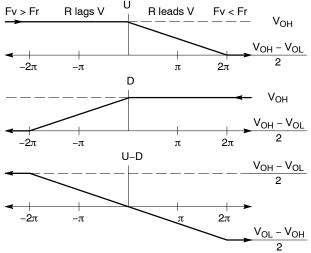

The operation of the 12140 can best be described using the plots of Figure 2. Figure 2 plots the average value of  $\overline{U}$ ,  $\overline{D}$  and the difference between  $\overline{U}$  and  $\overline{D}$  versus the phase difference between the V and R inputs.

There are four potential relationships between V and R: R lags or leads V and the frequency of R is less than or greater than the frequency of V. Under these four conditions the 12140 will function as follows:

Figure 2. Average Output Voltage vs. Phase Difference

#### R lags V in phase

When the R and V inputs are equal in frequency and the phase of R lags that of V the  $\overline{U}$  output will stay HIGH while the  $\overline{D}$  output will pulse from HIGH to LOW. The magnitude of the pulse will be proportional to the phase difference between the V and R inputs reaching a minimum 50% duty cycle under a 180° out of phase condition. The signal on  $\overline{D}$  indicates to the VCO to decrease in frequency to bring the loop into lock.

#### V frequency > R frequency

When the frequency of V is greater than that of R the 12140 behaves in a similar fashion as above. Again the signal on  $\overline{D}$  indicates that the VCO frequency must be decreased to bring the loop into lock.

#### R leads V in phase

When the R and V inputs are equal in frequency and the phase of R leads that of V the  $\overline{D}$  output will stay HIGH while the  $\overline{U}$  output pulses from HIGH to LOW. The magnitude of the pulse will be proportional to the phase difference between the V and R inputs reaching a minimum 50% duty cycle under a 180° out of phase condition. The signal on  $\overline{U}$  indicates to the VCO to increase in frequency to bring the loop into lock.

#### V frequency < R frequency

When the frequency of V is less than that of R the 12140 behaves in a similar fashion as above. Again the signal on  $\overline{U}$  indicates that the VCO frequency must be decreased to bring the loop into lock.

From Figure 2 when V and R are at the same frequency and in phase the value of  $\overline{U}$  –  $\overline{D}$  is zero thus providing a zero error voltage to the VCO. This situation indicates the loop is in lock and the 12140 action will maintain the loop in its locked state.

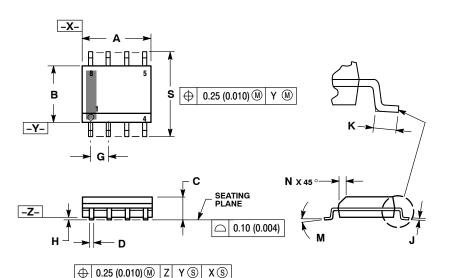

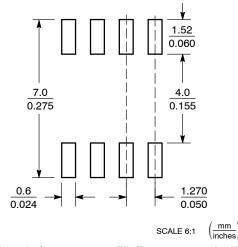

### **MECHANICAL CASE OUTLINE**

PACKAGE DIMENSIONS

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIN | IETERS | INCHES |       |  |  |  |

|-----|--------|--------|--------|-------|--|--|--|

| DIM | MIN    | MAX    | MIN    | MAX   |  |  |  |

| Α   | 4.80   | 5.00   | 0.189  | 0.197 |  |  |  |

| В   | 3.80   | 4.00   | 0.150  | 0.157 |  |  |  |

| C   | 1.35   | 1.75   | 0.053  | 0.069 |  |  |  |

| D   | 0.33   | 0.51   | 0.013  | 0.020 |  |  |  |

| G   | 1.27   | 7 BSC  | 0.05   | 0 BSC |  |  |  |

| Н   | 0.10   | 0.25   | 0.004  | 0.010 |  |  |  |

| J   | 0.19   | 0.25   | 0.007  | 0.010 |  |  |  |

| K   | 0.40   | 1.27   | 0.016  | 0.050 |  |  |  |

| M   | 0 °    | 8 °    | 0 °    | 8 °   |  |  |  |

| N   | 0.25   | 0.50   | 0.010  | 0.020 |  |  |  |

| S   | 5.80   | 6.20   | 0.228  | 0.244 |  |  |  |

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot = Year = Work Week

= Pb-Free Package

XXXXXX = Specific Device Code = Assembly Location Α

ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                 | PAGE 1 OF 2 |  |  |  |  |

onsemi and ONSEMi, are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### SOIC-8 NB CASE 751-07 ISSUE AK

#### **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                        | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1     | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                  | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                                      | 7. BASE, #1 8. EMITTER, #1  STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                              | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd          | STYLE 8:<br>PIN 1. COLLECTOR, DIE #1<br>2. BASE, #1<br>3. BASE, #2                                                                                                       |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON        | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                    | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                     | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                  |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                     | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                           | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON     | STYLE 16:  PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC  STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE STYLE 22:                                             | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1 STYLE 23: PIN 1. LINE 1 IN        | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN STYLE 24:                                                          |

| PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                                         | PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                                 |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                                | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                          | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                  | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                         |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                               | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                 |                                                                                                                                           |                                                                                                                                                                          |

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.  Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                   | PAGE 2 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of the part. onsemi is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales

### **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com