# **DLPC900AZPC** Datasheet

www.digi-electronics.com

M

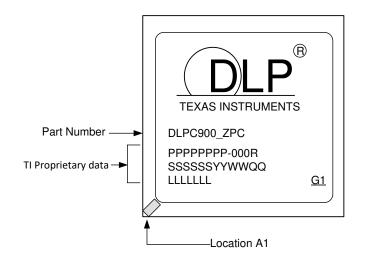

| DiGi Electronics Part Number | DLPC900AZPC-DG     |

|------------------------------|--------------------|

| Manufacturer                 | Texas Instruments  |

| lanufacturer Product Number  | DLPC900AZPC        |

| Description                  | IC DMD CONTROLLER  |

| Detailed Description         | DMD Driver 516-BGA |

516BGA

(27x27)

https://www.DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

## Purchase and inquiry

| Manufacturer Product Number:                              | Manufacturer:          |

|-----------------------------------------------------------|------------------------|

| DLPC900AZPC                                               | Texas Instruments      |

| Series:                                                   | Product Status:        |

|                                                           | Active                 |

| Display Type:                                             | Configuration:         |

| DMD                                                       |                        |

| Interface:                                                | Digits or Characters:  |

| I2C, SPI                                                  |                        |

| Voltage - Supply:                                         | Operating Temperature: |

| 1.09V ~ 1.2V, 1.1V ~ 1.2V, 1.71V ~ 1.89V, 3.135V ~ 3.465V | 0°C ~ 55°C             |

| Mounting Type:                                            | Package / Case:        |

| Surface Mount                                             | 516-BGA                |

| Supplier Device Package:                                  | Base Product Number:   |

| 516-BGA (27x27)                                           | DLPC900                |

|                                                           |                        |

## **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | Not Applicable                    |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

| 8542.31.0001     |                                   |

Texas Instruments

DLPS037H – OCTOBER 2014 – REVISED JUNE 2024

# **DLPC900 Digital Controller for Advanced Light Control**

## 1 Features

- Scalable controller supporting DLP500YX, DLP5500, DLP6500, DLP670S, and DLP9000 digital micromirror devices (DMDs) for highresolution industrial and display applications

- · Supports multiple high-speed pattern rates up to:

- 16129Hz (DLP500YX, 1-bit pre-stored pattern mode)

- 2016Hz (DLP500YX, 8-bit pre-stored pattern mode with illumination modulation)

- 1008Hz (DLP500YX, 16-bit pre-stored pattern mode with illumination modulation)

- Internal DRAM: 128 megabytes

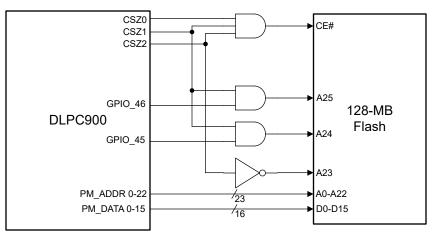

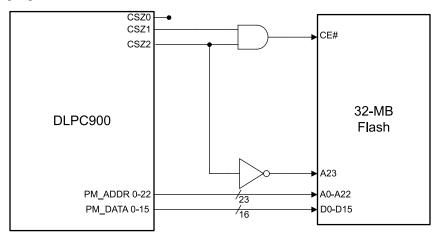

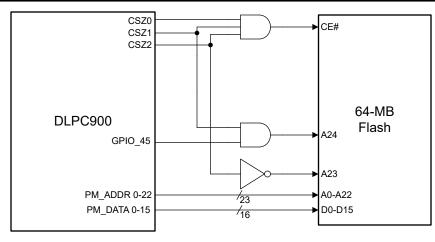

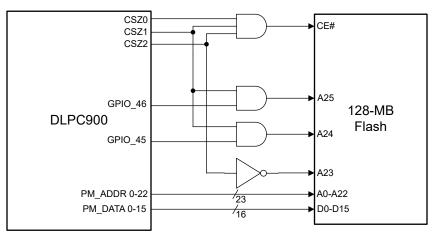

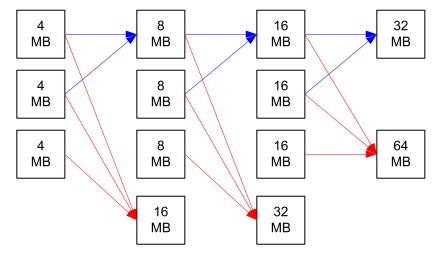

- External flash capability: 128-megabyte external flash capability

- 1-to-1 input mapping to micromirrors

- Easy synchronization with cameras and sensors

Two configurable input and output triggers

- Fully programmable GPIO and PWM signals

- Multiple control interfaces

- One USB 1.1 target port and three I<sup>2</sup>C ports

- LED enable and PWM generators

- Video mode

- Dual 24-bit RGB inputs up to 120Hz

- YUV, YCrCb, or RGB data format

- Standard video from XGA to WQXGA

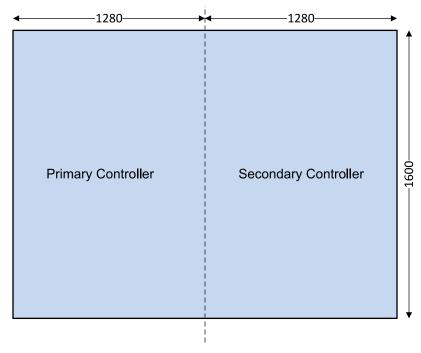

- DLP9000 (WQXGA), DLP500YX (2048 × 1200), and DLP670S (2716 × 1600) require two DLPC900 controllers

## 2 Applications

- 3D machine vision and optical inspection

- 3D printing and additive manufacturing

- Ophthalmology

- 3D scanners for limb and skin measurement

- · Intelligent and adaptive lighting

- 3D imaging microscopes

## **3 Description**

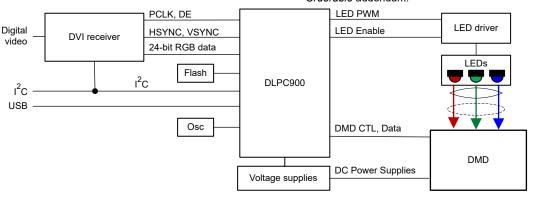

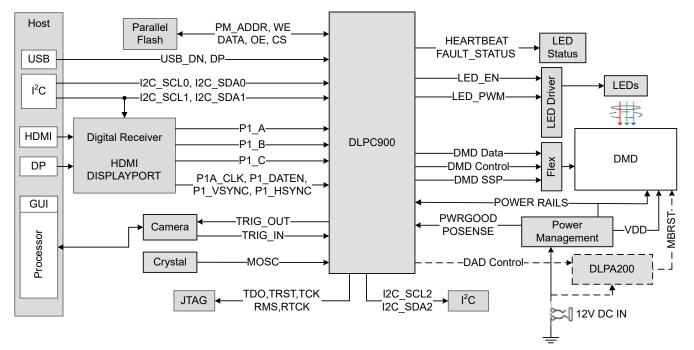

The DLP® DLPC900 is a scalable digital micromirror device (DMD) controller that supports reliable DLP5500, DLP6500, operation of DLP500YX, DLP670S. and DLP9000 DMDs. This highperformance DMD controller enables programmable, high-speed pattern rates for advanced light control, especially in industrial applications. DLPC900 pattern rates enable fast and accurate 3D scanning and 3D printing, as well as support high-resolution and intelligent imaging applications. DLPC900 offers 128 megabytes of embedded internal DRAM for convenient buffering of between 400 to 1024 1-bit patterns depending on DMD. Input and output triggers offer easy connection and synchronization with a variety of cameras, sensors, and other peripherals.

Go to the TI DLP® light-control technology page to learn how to get started. DLP® advanced light control resources include evaluation modules, reference designs, optical module manufacturers, and DLP® design network partners.

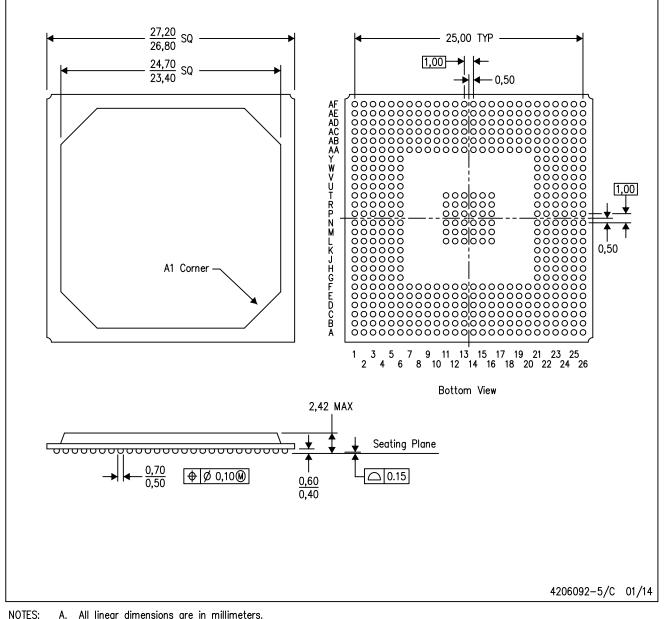

# Device Information PART NUMBER PACKAGE(1) PACKAGE SIZE DLPC900 BGA (516) 27.00mm × 27.00mm

(1) For more information, see the *Mechanical, Packaging, and Orderable* addendum.

## **Simplified Application**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## **Table of Contents**

| 1 Features1                                                  |

|--------------------------------------------------------------|

| 2 Applications1                                              |

| 3 Description                                                |

| 4 Pin Configuration and Functions                            |

| 5 Specifications                                             |

| 5.1 Absolute Maximum Ratings19                               |

| 5.2 ESD Ratings 20                                           |

| 5.3 Recommended Operating Conditions20                       |

| 5.4 Thermal Information21                                    |

| 5.5 Electrical Characteristics21                             |

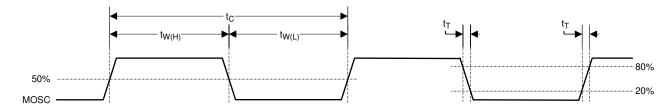

| 5.6 System Oscillators Timing Requirements <sup>(1)</sup> 24 |

| 5.7 Power-Up and Power-Down Timing Requirements 25           |

| 5.8 JTAG Interface: I/O Boundary Scan Application            |

| Timing Requirements                                          |

| 5.9 JTAG Interface: I/O Boundary Scan Application            |

| Switching Characteristics                                    |

| 5.10 Programmable Output Clocks Switching                    |

| Characteristics                                              |

| 5.11 Port 1 and 2 Input Pixel Interface Timing               |

| Requirements                                                 |

| 5.12 Two Pixels Per Clock (48-Bit Bus) Timing                |

| Requirements                                                 |

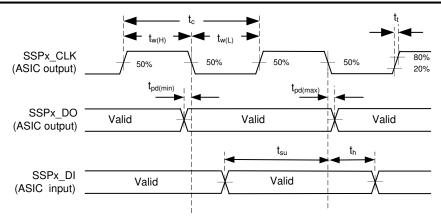

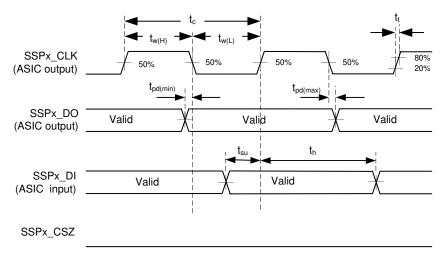

| 5.13 Synchronous Serial Port (SSP) Switching                 |

| Characteristics                                              |

| 5.14 DMD Interface Switching Characteristics                 |

| 5.15 DMD LVDS Interface Switching Characteristics 34         |

| 5.16 Source Input Blanking Requirements                      |

| 6 Detailed Description                                       |

|    | 6.1 Overview                                          | 36  |

|----|-------------------------------------------------------|-----|

|    | 6.2 Functional Block Diagram                          | 36  |

|    | 6.3 Feature Description                               | .37 |

|    | 6.4 Device Functional Modes                           | .47 |

| 7  | Application and Implementation                        |     |

|    | 7.1 Application Information                           |     |

|    | 7.2 Typical Applications                              |     |

| 8  | Power Supply Recommendations                          | .59 |

|    | 8.1 System Power Regulation                           |     |

|    | 8.2 System Environment and Defaults                   |     |

|    | 8.3 System Power-Up Sequence                          |     |

|    | 8.4 System Reset Operation                            |     |

| 9  | Layout                                                |     |

|    | 9.1 Layout Guidelines                                 |     |

|    | 9.2 Layout Example                                    |     |

|    | 9.3 Thermal Considerations                            | .75 |

| 1( | Device and Documentation Support                      |     |

|    | 10.1 Device Support                                   |     |

|    | 10.2 Documentation Support                            |     |

|    | 10.3 Receiving Notification of Documentation Updates. |     |

|    | 10.4 Support Resources                                |     |

|    | 10.5 Trademarks                                       |     |

|    | 10.6 Electrostatic Discharge Caution                  |     |

|    | 10.7 Glossary                                         |     |

| 11 | Revision History                                      |     |

|    | 2 Mechanical, Packaging, and Orderable                |     |

|    | Information                                           | 81  |

|    |                                                       |     |

## **4** Pin Configuration and Functions

|    | 26 | 25 | 24 | 53 | 52 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | ÷ | 10 | 6 | ø | 7 | 9   | сı | 4 | e | 0 | - |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|----|---|---|---|-----|----|---|---|---|---|----|

|    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 | ]. |

| n  | 0  | 0  | 0  | 0  | 0  | õ  | õ  | õ  | õ  | õ  | o  | 0  | õ  | õ  | õ  | õ | õ  | õ | õ | 0 | 0   | 0  | 0 | 0 | 0 | 0 |    |

| 5  | 0  | 0  | 0  | 0  | 0  | 0  | o  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | õ  | 0 | 0 | o | ō |    |

| 5  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 | 4  |

| ш  | 0  | 0  | 0  | 0  | ο  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 | l  |

|    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 |    |

| 5  | 0  | 0  | 0  | 0  | 0  | 0  |    | -  |    | -  | -  |    |    | -  | -  |   |    | - | - |   | ] 0 | 0  | o | 0 | 0 | 0 |    |

| r  | о  | 0  | 0  | 0  | о  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | о | 0 | :  |

| -  | о  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 |    |

| ۷  | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | 1  |

| _  | 0  | 0  | 0  | 0  | ο  | ο  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0 |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 |    |

| Σ  | о  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | ο  | 0  | 0  | 0 |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | :  |

| z  | 0  | 0  | 0  | ο  | о  | ο  |    |    |    |    | 0  | 0  | 0  | ο  | ο  | 0 |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | :  |

| L  | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0 |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 |    |

| r  | 0  | 0  | о  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0 |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | 1  |

| -  | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    | 0  | 0  | 0  | 0  | 0  | 0 |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 |    |

| 5  | 0  | 0  | 0  | 0  | о  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | :  |

| >  | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | :  |

| >  | о  | 0  | 0  | 0  | о  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 |    |

| -  | 0  | 0  | 0  | 0  | 0  | 0  |    |    |    |    |    |    |    |    |    |   |    |   |   |   | 0   | 0  | 0 | 0 | 0 | 0 | :  |

| AA | о  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 |    |

| AB | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | о | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 | 4  |

| Ą  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 |    |

| Ð  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 | 4  |

| ÄE | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | ο   | 0  | 0 | 0 | 0 | 0 | Ļ  |

| Å  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0 | 0 | 0   | 0  | 0 | 0 | 0 | 0 | Ļ  |

| L  | 26 | 25 | 24 | 53 | 53 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | ÷ | 10 | 6 | ø | ~ | 9   | 5  | 4 | ო | 0 | - |    |

#### **DLPC900** DLPS037H - OCTOBER 2014 - REVISED JUNE 2024

| Table 4-1. | Initialization | Pin Functions |

|------------|----------------|---------------|

|            |                |               |

| PIN        |        | I/O   |                         | CLK    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|--------|-------|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NUMBER | POWER | I/O TYPE <sup>(1)</sup> | SYSTEM | DESCRIPTION <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

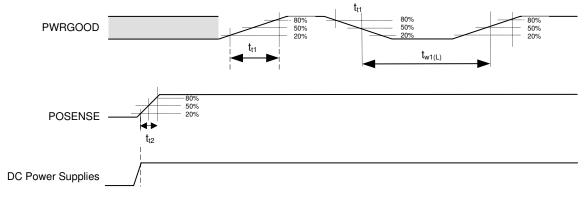

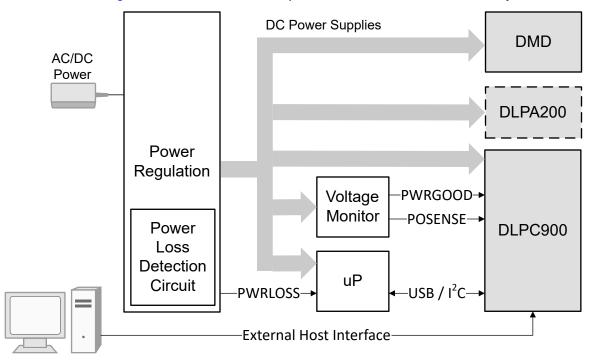

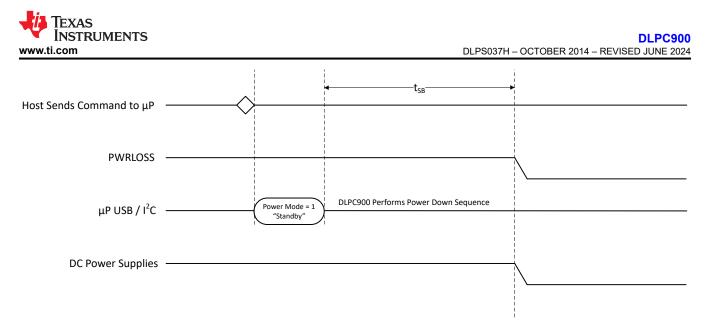

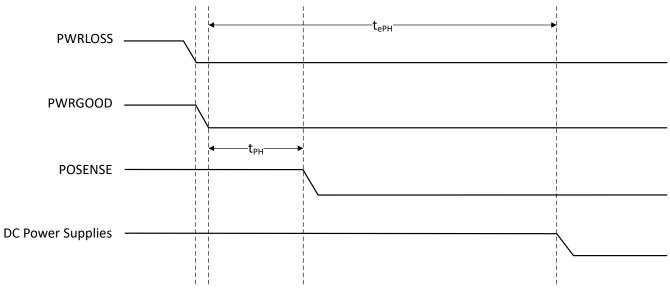

| POSENSE    | P22    | VDD33 | l4<br>H                 | Async  | Power-on sense is an active high signal with hysteresis,<br>generated from an external voltage monitor circuit. This signal<br>is driven active high when all the controller supply voltages<br>have reached 90% of their specified minimum voltage.<br>This signal is driven inactive low after the falling edge of<br>PWRGOOD as shown in Figure 5-4 and Figure 5-5. Refer<br>to Section 5.7 for more details.                                                                                                                                                                                                                                                                                                                                    |

| PWRGOOD    | T26    | VDD33 | l <sub>4</sub><br>H     | Async  | Power Good is an active high signal with hysteresis that is<br>provided from an external voltage monitor circuit. A high value<br>indicates all power is within operating voltage specifications<br>and the system is safe to exit its RESET state. Refer to<br>Section 5.7 for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EXT_ARSTZ  | T24    | VDD33 | 0 <sub>2</sub>          | Async  | General purpose active low reset output signal. This output<br>is driven low immediately after POSENSE is externally<br>driven low, placing the system in RESET and remains low<br>while POSENSE remains low. EXT_ARSTZ will continue to<br>be held low after POSENSE is driven high and released<br>by the controller firmware. EXT_ARSTZ is also driven low<br>approximately 5µs after the detection of a PWRGOOD or any<br>internally generated reset. In all cases, it will remain active for<br>a minimum of 2ms.                                                                                                                                                                                                                              |

| CTRL_ARSTZ | T25    | VDD33 | O <sub>2</sub>          | Async  | Controller active low reset output signal. This output is driven<br>low immediately after POSENSE is externally driven low and<br>remains low while POSENSE remains low. CTRL_ARSTZ will<br>continue to be held low after POSENSE is driven high and<br>released by the controller firmware. CTRL_ARSTZ is also<br>optionally asserted low approximately 5µs after the detection<br>of a PWRGOOD or any internally generated reset. In all<br>cases it will remain active for a minimum of 2ms.                                                                                                                                                                                                                                                     |

| AFE_ARSTZ  | AC12   | VDD33 | O <sub>2</sub>          | Async  | Analog Front End active low reset output signal. This output<br>is driven low immediately upon asserting power-up reset<br>(POSENSE) low and remains low while POSENSE remains<br>low. AFE_ARSTZ continues to be held low after the release<br>of power-up reset (that is, POSENSE set high) until released<br>by software. AFE_ARSTZ is also asserted low approximately<br>5 $\mu$ s after the detection of a PWRGOOD or any internally<br>generated reset. In all cases, it remains active for a minimum<br>of 2ms after the reset condition is released by software. Note<br>that the ASIC contains a software register that can be used to<br>independently drive this output. This pin requires an external<br>4.7 $\kappa$ Ω pullup resistor. |

| AFE_IRQ    | AB13   | VDD33 | I <sub>4</sub>          | Async  | Analog Front End interrupt active high signal. This signal includes an internal pulldown and uses hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Refer to I/O Type and Subscript Definition (Table 4-15).

Refer to the Section 7.2.2 and the Section 7.2.1 for a description between a one controller and a two controller configuration.

| PIN<br>NAME                                      |                          |       | I/O TYPE <sup>(1)</sup> | CLK<br>SYSTEM | DESCRIPTION <sup>(2)</sup>                                                                                                                                                                                                |  |  |  |  |  |

|--------------------------------------------------|--------------------------|-------|-------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

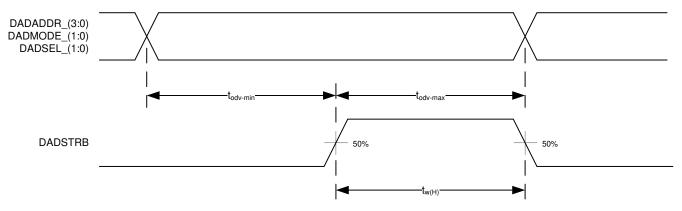

| DADOEZ                                           | AE7                      | VDD33 | O <sub>5</sub>          | Async         | DMD output-enable (active low). This signal does not<br>apply to the secondary controller in a two-controller system<br>configuration. On the secondary controller, this pin is<br>reserved and must be left unconnected. |  |  |  |  |  |

| DADADDR_3<br>DADADDR_2<br>DADADDR_1<br>DADADDR_0 | AD6<br>AE5<br>AF4<br>AB8 | VDD33 | 0 <sub>5</sub>          | Async         | DMD address. This signal does not apply to the secondary controller in a two-controller system configuration. On the secondary controller, this pin is reserved and must be left unconnected.                             |  |  |  |  |  |

## Table 4-2. DMD Control Pin Functions

## Table 4-2. DMD Control Pin Functions (continued)

| PIN                    | PIN        |       | I/O TYPE <sup>(1)</sup> | CLK    | DESCRIPTION <sup>(2)</sup>                                                                                                                                                                   |

|------------------------|------------|-------|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                   | NUMBER     | POWER |                         | SYSTEM | DESCRIPTION                                                                                                                                                                                  |

| DADMODE_1<br>DADMODE_0 | AD7<br>AE6 | VDD33 | O <sub>5</sub>          | Async  | DMD mode. This signal does not apply to the secondary controller in a two-controller system configuration. On the secondary controller, this pin is reserved and must be left unconnected.   |

| DADSEL_1<br>DADSEL_0   | AE4<br>AC7 | VDD33 | O <sub>5</sub>          | Async  | DMD select. This signal does not apply to the secondary controller in a two-controller system configuration. On the secondary controller, this pin is reserved and must be left unconnected. |

| DADSTRB                | AF5        | VDD33 | O <sub>5</sub>          | Async  | DMD strobe. This signal does not apply to the secondary controller in a two-controller system configuration. On the secondary controller, this pin is reserved and must be left unconnected. |

| DAD_INTZ               | AC8        | VDD33 | l <sub>4</sub><br>H     | Async  | DMD interrupt (active low). Requires an external $1k\Omega$ pullup resistor                                                                                                                  |

(1)

Refer to I/O Type and Subscript Definition (Table 4-15). Refer to the Section 7.2.2 and the Section 7.2.1 for a description between a one controller and a two controller configuration. (2)

| PIN <sup>(3) (4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                        |           |                         | CLK              |                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|------------------|------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NUMBER                                                                                                                                                                                                                 | I/O POWER | I/O TYPE <sup>(1)</sup> | SYSTEM           | DESCRIPTION <sup>(2)</sup>                                 |

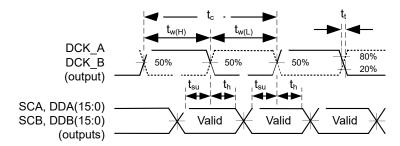

| DCKA_P<br>DCKA_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V4<br>V3                                                                                                                                                                                                               | VDD18     | 0 <sub>7</sub>          | DCKA_P<br>DCKA_N | DMD, LVDS interface channel A, differential clock          |

| SCA_P<br>SCA_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V2<br>V1                                                                                                                                                                                                               | VDD18     | O <sub>7</sub>          | DCKA_P<br>DCKA_N | DMD, LVDS interface channel A, differential serial control |

| DDA_P_15<br>DDA_P_14<br>DDA_P_14<br>DDA_P_14<br>DDA_P_13<br>DDA_P_13<br>DDA_P_12<br>DDA_P_12<br>DDA_P_12<br>DDA_P_11<br>DDA_P_11<br>DDA_P_10<br>DDA_P_9<br>DDA_P_9<br>DDA_P_9<br>DDA_P_9<br>DDA_P_9<br>DDA_P_8<br>DDA_P_9<br>DDA_P_8<br>DDA_N_8<br>DDA_P_7<br>DDA_P_6<br>DDA_P_7<br>DDA_P_6<br>DDA_P_5<br>DDA_N_5<br>DDA_P_5<br>DDA_N_5<br>DDA_P_5<br>DDA_N_5<br>DDA_P_4<br>DDA_P_3<br>DDA_P_3<br>DDA_P_3<br>DDA_P_2<br>DDA_P_1<br>DDA_P_2<br>DDA_P_1<br>DDA_P_1<br>DDA_P_1<br>DDA_P_1<br>DDA_P_1<br>DDA_P_0<br>DDA_P_0<br>DDA_P_0<br>DDA_P_0<br>DDA_P_0<br>DDA_P_0<br>DDA_N_0 | P4<br>P3<br>P2<br>P1<br>R4<br>R3<br>R2<br>R1<br>T4<br>T3<br>T2<br>T1<br>U4<br>U3<br>U2<br>U1<br>W4<br>W3<br>W2<br>W1<br>Y2<br>Y1<br>Y4<br>Y2<br>Y1<br>Y4<br>Y3<br>AA2<br>AA1<br>AA4<br>AA3<br>AB2<br>AB1<br>AC2<br>AC1 | - VDD18   | O <sub>7</sub>          | DCKA_P<br>DCKA_N | DMD, LVDS interface channel A, differential serial data    |

| DCKB_P<br>DCKB_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | J3<br>J4                                                                                                                                                                                                               | VDD18     | O <sub>7</sub>          | DCKB_P<br>DCKB_N | DMD, LVDS interface channel B, differential clock          |

#### Table 4-3. DMD LVDS Interface Pin Functions

## Table 4-3. DMD LVDS Interface Pin Functions (continued)

| PIN <sup>(3) (4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                              | I/O POWER | I/O TYPE <sup>(1)</sup> | CLK              | DESCRIPTION <sup>(2)</sup>                                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------|------------------|------------------------------------------------------------|--|--|--|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NUMBER                                                                                                                                                                                       | 10 POWER  | NOTTPE()                | SYSTEM           | DESCRIPTION                                                |  |  |  |

| SCB_P<br>SCB_N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | J1<br>J2                                                                                                                                                                                     | VDD18     | O <sub>7</sub>          | DCKB_P<br>DCKB_N | DMD, LVDS interface channel B, differential serial control |  |  |  |

| DDB_P_15<br>DDB_P_14<br>DDB_P_14<br>DDB_N_14<br>DDB_P_13<br>DDB_P_13<br>DDB_P_12<br>DDB_N_12<br>DDB_P_11<br>DDB_P_10<br>DDB_P_10<br>DDB_P_10<br>DDB_P_9<br>DDB_N_9<br>DDB_P_9<br>DDB_P_9<br>DDB_P_8<br>DDB_P_8<br>DDB_P_8<br>DDB_P_7<br>DDB_P_7<br>DDB_P_6<br>DDB_N_5<br>DDB_N_5<br>DDB_N_5<br>DDB_N_5<br>DDB_N_5<br>DDB_N_5<br>DDB_N_5<br>DDB_N_5<br>DDB_P_4<br>DDB_P_4<br>DDB_P_3<br>DDB_P_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_1<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_1<br>DDB_P_1<br>DDB_N_1<br>DDB_P_2<br>DDB_N_1<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_2<br>DDB_N_3<br>DDB_P_3<br>DDB_N_3<br>DDB_P_3<br>DDB_N_3<br>DDB_P_4<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1 DDB_N_1<br>DDB_N_1 DDB_N_1 | N1<br>N2<br>N3<br>N4<br>M2<br>M1<br>M3<br>M4<br>L1<br>L2<br>L3<br>L4<br>K1<br>K2<br>K3<br>K4<br>H1<br>H2<br>H3<br>H4<br>G1<br>G2<br>G3<br>G4<br>F1<br>F2<br>F3<br>F4<br>E1<br>E2<br>D1<br>D2 | VDD18     | O <sub>7</sub>          | DCKB_P<br>DCKB_N | DMD, LVDS interface channel B, differential serial data    |  |  |  |

Refer to I/O Type and Subscript Definition (Table 4-15). (1)

(2) Refer to the Section 7.2.2 and the Section 7.2.1 for a description between a one controller and a two controller configuration.

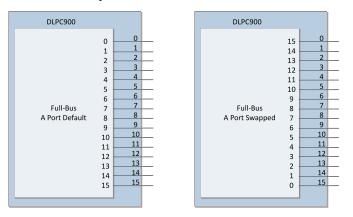

Several options allow reconfiguration of the DMD interface in order to better optimize board layout. The DLPC900 can swap channel A (3) with channel B. The DLPC900 can also swap the data bit order within each channel independent of swapping the A and B channels.

(4) The DLPC900 is a full-bus DMD signaling interface. Figure 6-4 shows the controller connections for this configuration.

|                           | Table 4-4. Program Memory Flash Interface Pin Functions |              |                         |            |                                        |                                                          |                                        |  |  |

|---------------------------|---------------------------------------------------------|--------------|-------------------------|------------|----------------------------------------|----------------------------------------------------------|----------------------------------------|--|--|

| PIN <sup>(3)</sup>        |                                                         |              |                         |            | DESCRIPTION                            |                                                          |                                        |  |  |

| NAME                      | NUMBER                                                  | I/O<br>POWER | I/O TYPE <sup>(1)</sup> | CLK SYSTEM | CHIP SELECT 0<br>(ADDITIONAL<br>FLASH) | CHIP SELECT 1<br>(BOOT FLASH<br>ONLY) <sup>(2) (3)</sup> | CHIP SELECT 2<br>(ADDITIONAL<br>FLASH) |  |  |

| PM_CSZ_0 <sup>(4)</sup>   | D13                                                     | VDD33        | O <sub>5</sub>          | Async      | Chip select<br>(active low)            | N/A                                                      | N/A                                    |  |  |

| PM_CSZ_1 (4)              | E12                                                     | VDD33        | 0 <sub>5</sub>          | Async      | N/A                                    | Boot flash chip<br>select<br>(active low)                | N/A                                    |  |  |

| PM_CSZ_2 (4)              | A13                                                     | VDD33        | O <sub>5</sub>          | Async      | N/A                                    | N/A                                                      | Chip select<br>(active low)            |  |  |

| PM_ADDR_22 <sup>(5)</sup> | A12                                                     | VDD33        | В <sub>5</sub>          | Async      | Address bit (MSB)                      | Address bit<br>(MSB)                                     | Address bit (MSB)                      |  |  |

| PM_ADDR_21 (5)            | E11                                                     | VDD33        | B <sub>5</sub>          | Async      | Address bit                            | Address bit                                              | Address bit                            |  |  |

| PM_ADDR_20                | D12                                                     | VDD33        | O <sub>5</sub>          | Async      | Address bit                            | Address bit                                              | Address bit                            |  |  |

| PM_ADDR_19                | C12                                                     | VDD33        | O <sub>5</sub>          | Async      | Address bit                            | Address bit                                              | Address bit                            |  |  |

| PM_ADDR_18                | B11                                                     | VDD33        | O <sub>5</sub>          | Async      | Address bit                            | Address bit                                              | Address bit                            |  |  |

#### \_ . . . . . \_ \_ . .

6 Submit Document Feedback

DLPS037H – OCTOBER 2014 – REVISED JUNE 2024

## Table 4-4. Program Memory Flash Interface Pin Functions (continued)

| PIN <sup>(3</sup> |        |              | <b>_</b>                |            | ce Pin Function                           | DESCRIPTION                                              |                                           |

|-------------------|--------|--------------|-------------------------|------------|-------------------------------------------|----------------------------------------------------------|-------------------------------------------|

| NAME              | NUMBER | I/O<br>POWER | I/O TYPE <sup>(1)</sup> | CLK SYSTEM | CHIP SELECT 0<br>(ADDITIONAL<br>FLASH)    | CHIP SELECT 1<br>(BOOT FLASH<br>ONLY) <sup>(2) (3)</sup> | CHIP SELECT 2<br>(ADDITIONAL<br>FLASH)    |

| PM_ADDR_17        | A11    | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_16        | D11    | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_15        | C11    | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_14        | E10    | VDD33        | O5                      | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_13        | D10    | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_12        | C10    | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_11        | B9     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_10        | A9     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_9         | E9     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_8         | D9     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_7         | C9     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_6         | B8     | VDD33        | O5                      | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_5         | A8     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_4         | D8     | VDD33        | O <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_3         | C8     | VDD33        | 0 <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_2         | B7     | VDD33        | 0 <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_1         | A7     | VDD33        | 0 <sub>5</sub>          | Async      | Address bit                               | Address bit                                              | Address bit                               |

| PM_ADDR_0         | C7     | VDD33        | 0 <sub>5</sub>          | Async      | Address bit (LSB)                         | Address bit (LSB)                                        | Address bit (LSB)                         |

| PM_WEZ            | B12    | VDD33        | 0 <sub>5</sub>          | Async      | Write-enable<br>(active low)              | Write-enable<br>(active low)                             | Write-enable<br>(active low)              |

| PM_OEZ            | C13    | VDD33        | O <sub>5</sub>          | Async      | Output-enable<br>(active low)             | Output-enable<br>(active low)                            | Output-enable<br>(active low)             |

| PM_BLSZ_1         | B6     | VDD33        | O <sub>5</sub>          | Async      | UpperByte(15:8)<br>enable<br>(active low) | N/A                                                      | UpperByte(15:8)<br>Enable<br>(active low) |

| PM_BLSZ_0         | A6     | VDD33        | O <sub>5</sub>          | Async      | LowerByte(7:0)<br>enable<br>(active low)  | N/A                                                      | LowerByte(7:0)<br>Enable<br>(active low)  |

| PM_DATA_15        | C17    | VDD33        | B <sub>5</sub>          | Async      | Data bit (15)                             | Data bit (15)                                            | Data bit (15)                             |

| PM_DATA_14        | B16    | VDD33        | B <sub>5</sub>          | Async      | Data bit (14)                             | Data bit (14)                                            | Data bit (14)                             |

| PM_DATA_13        | A16    | VDD33        | B <sub>5</sub>          | Async      | Data bit (13)                             | Data bit (13)                                            | Data bit (13)                             |

| PM_DATA_12        | A15    | VDD33        | B <sub>5</sub>          | Async      | Data bit (12)                             | Data bit (12)                                            | Data bit (12)                             |

| PM_DATA_11        | B15    | VDD33        | B <sub>5</sub>          | Async      | Data bit (11)                             | Data bit (11)                                            | Data bit (11)                             |

| PM_DATA_10        | D16    | VDD33        | B <sub>5</sub>          | Async      | Data bit (10)                             | Data bit (10)                                            | Data bit (10)                             |

| PM_DATA_9         | C16    | VDD33        | B <sub>5</sub>          | Async      | Data bit (9)                              | Data bit (9)                                             | Data bit (9)                              |

| PM_DATA_8         | E14    | VDD33        | B <sub>5</sub>          | Async      | Data bit (8)                              | Data bit (8)                                             | Data bit (8)                              |

| PM_DATA_7         | D15    | VDD33        | B <sub>5</sub>          | Async      | Data bit (7)                              | Data bit (7)                                             | Data bit (7)                              |

| PM_DATA_6         | C15    | VDD33        | B <sub>5</sub>          | Async      | Data bit (6)                              | Data bit (6)                                             | Data bit (6)                              |

| PM_DATA_5         | B14    | VDD33        | B <sub>5</sub>          | Async      | Data bit (5)                              | Data bit (5)                                             | Data bit (5)                              |

| PM_DATA_4         | A14    | VDD33        | B <sub>5</sub>          | Async      | Data bit (4)                              | Data bit (4)                                             | Data bit (4)                              |

| PM_DATA_3         | E13    | VDD33        | B <sub>5</sub>          | Async      | Data bit (3)                              | Data bit (3)                                             | Data bit (3)                              |

| PM_DATA_2         | D14    | VDD33        | B <sub>5</sub>          | Async      | Data bit (2)                              | Data bit (2)                                             | Data bit (2)                              |

| PM_DATA_1         | C14    | VDD33        | B <sub>5</sub>          | Async      | Data bit (1)                              | Data bit (1)                                             | Data bit (1)                              |

DLPC900 DLPS037H – OCTOBER 2014 – REVISED JUNE 2024

## Table 4-4. Program Memory Flash Interface Pin Functions (continued)

|                    |        |              | ,                       |            |                                        | - (                                                      |                                        |

|--------------------|--------|--------------|-------------------------|------------|----------------------------------------|----------------------------------------------------------|----------------------------------------|

| PIN <sup>(3)</sup> |        |              |                         |            | DESCRIPTION                            |                                                          |                                        |

| NAME               | NUMBER | I/O<br>POWER | I/O TYPE <sup>(1)</sup> | CLK SYSTEM | CHIP SELECT 0<br>(ADDITIONAL<br>FLASH) | CHIP SELECT 1<br>(BOOT FLASH<br>ONLY) <sup>(2) (3)</sup> | CHIP SELECT 2<br>(ADDITIONAL<br>FLASH) |

| PM_DATA_0          | B13    | VDD33        | B <sub>5</sub>          | Async      | Data bit (0)                           | Data bit (0)                                             | Data bit (0)                           |

(1) Refer to I/O Type and Subscript Definition (Table 4-15).

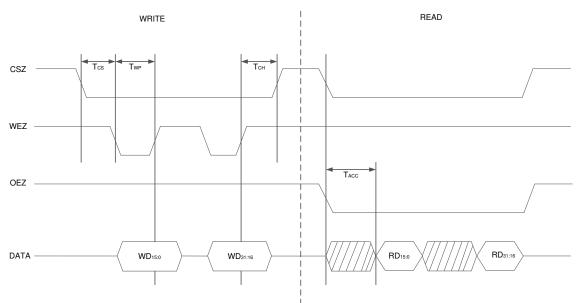

(2) The default wait-state is set for a flash device of 120ns access time. Therefore, the slowest flash access time supported is 120ns. Refer to the Section 7.2.1.2.1.4.2 on how to program new wait-state values.

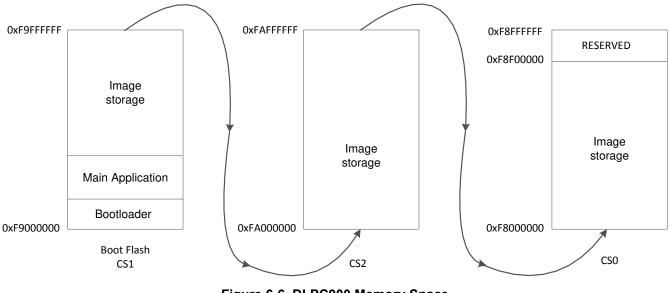

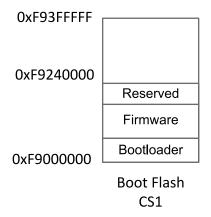

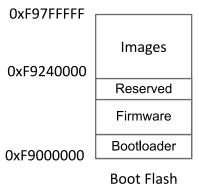

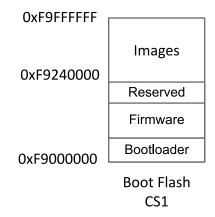

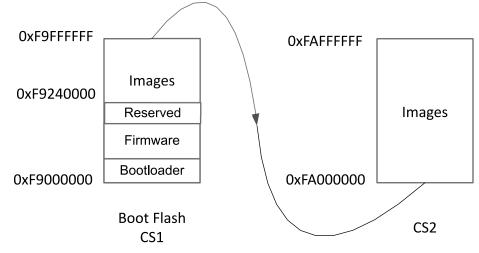

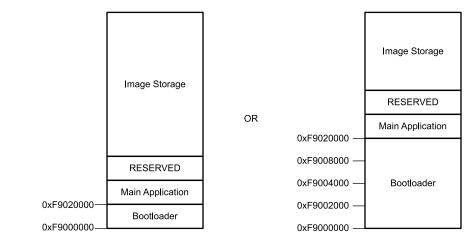

(3) Refer to the Figure 7-2 for the memory layout of the boot flash.

(4) Requires an external  $10k\Omega$  pullup resistor

(5) Requires an external  $10k\Omega$  pulldown resistor

#### Table 4-5. Port 1 and Port 2 Channel Data and Control Pin Functions

| PIN <sup>(3) (4) (5)</sup>                                                                                           |                                                                              | I/O   | I/O                 |                                 | DESCRIPTION(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|---------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                 | NUMBER                                                                       | POWER | TYPE <sup>(1)</sup> | CLK SYSTEM                      | DESCRIPTION <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P_CLK1                                                                                                               | AE22                                                                         | VDD33 | l <sub>4</sub><br>D | N/A                             | Input port data pixel write clock (selectable as rising or falling edge triggered, and with which port it is associated [Port 1 or Port 2 or [Port 1 and Port 2]]).                                                                                                                                                                                                                                                                                                        |

| P_CLK2                                                                                                               | W25                                                                          | VDD33 | l <sub>4</sub><br>D | N/A                             | Input port data pixel write clock (selectable as rising or falling edge triggered, and with which port it is associated [Port 1 or Port 2 or [Port 1 and Port 2]]).                                                                                                                                                                                                                                                                                                        |

| P_CLK3                                                                                                               | AF23                                                                         | VDD33 | l <sub>4</sub><br>D | N/A                             | Input port data pixel write clock (selectable as rising or falling edge triggered, and with which port it is associated [Port 1 or Port 2 or [Port 1 and Port 2]]).                                                                                                                                                                                                                                                                                                        |

| P_DATAEN1                                                                                                            | AF22                                                                         | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Active high data enable. Selectable as to which port it is associated with (Port 1 or Port 2 or [Port 1 and Port 2]).                                                                                                                                                                                                                                                                                                                                                      |

| P_DATAEN2                                                                                                            | W24                                                                          | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Active high data enable. Selectable as to which port it is associated with (Port 1 or Port 2 or [Port 1 and Port 2]).                                                                                                                                                                                                                                                                                                                                                      |

| P1_A9<br>P1_A8<br>P1_A7<br>P1_A6<br>P1_A5<br>P1_A4<br>P1_A3<br>P1_A2<br>P1_A1 <sup>(3)</sup><br>P1_A0 <sup>(3)</sup> | AD15<br>AE15<br>AE14<br>AD13<br>AC13<br>AF14<br>AF13<br>AF12<br>AE12         | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 1 A channel input pixel data (bit weight 128)<br>Port 1 A channel input pixel data (bit weight 64)<br>Port 1 A channel input pixel data (bit weight 32)<br>Port 1 A channel input pixel data (bit weight 16)<br>Port 1 A channel input pixel data (bit weight 8)<br>Port 1 A channel input pixel data (bit weight 4)<br>Port 1 A channel input pixel data (bit weight 2)<br>Port 1 A channel input pixel data (bit weight 1)<br>Unused, tie to 0<br>Unused, tie to 0. |

| P1_B9<br>P1_B8<br>P1_B7<br>P1_B6<br>P1_B5<br>P1_B4<br>P1_B3<br>P1_B2<br>P1_B1 <sup>(3)</sup><br>P1_B0 <sup>(3)</sup> | AF18<br>AB18<br>AC15<br>AC16<br>AD16<br>AE16<br>AF16<br>AF15<br>AC14<br>AD14 | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 1 B channel input pixel data (bit weight 128)<br>Port 1 B channel input pixel data (bit weight 64)<br>Port 1 B channel input pixel data (bit weight 32)<br>Port 1 B channel input pixel data (bit weight 16)<br>Port 1 B channel input pixel data (bit weight 8)<br>Port 1 B channel input pixel data (bit weight 4)<br>Port 1 B channel input pixel data (bit weight 2)<br>Port 1 B channel input pixel data (bit weight 1)<br>Unused, tie to 0<br>Unused, tie to 0. |

| P1_C9<br>P1_C8<br>P1_C7<br>P1_C6<br>P1_C5<br>P1_C4<br>P1_C3<br>P1_C2<br>P1_C2<br>P1_C1 (3)<br>P1_C0 (3)              | AD20<br>AE20<br>AE21<br>AF21<br>AD19<br>AE19<br>AF19<br>AF20<br>AC19<br>AE18 | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 1 C channel input pixel data (bit weight 128)<br>Port 1 C channel input pixel data (bit weight 64)<br>Port 1 C channel input pixel data (bit weight 32)<br>Port 1 C channel input pixel data (bit weight 16)<br>Port 1 C channel input pixel data (bit weight 8)<br>Port 1 C channel input pixel data (bit weight 4)<br>Port 1 C channel input pixel data (bit weight 2)<br>Port 1 C channel input pixel data (bit weight 1)<br>Unused, tie to 0<br>Unused, tie to 0. |

#### Table 4-5. Port 1 and Port 2 Channel Data and Control Pin Functions (continued)

| PIN <sup>(3)</sup> <sup>(4)</sup> <sup>(4)</sup>                                                                                       | 5)                                                                           | 1/0   | I/O                 |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|---------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                                                                                                   | NUMBER                                                                       | POWER | TYPE <sup>(1)</sup> | CLK SYSTEM                      | DESCRIPTION <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| P1_VSYNC                                                                                                                               | AC20                                                                         | VDD33 | B <sub>2</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 1 vertical sync. While intended to be associated with port 1, it can be programmed for use with port 2.                                                                                                                                                                                                                                                                                                                                                               |  |

| P1_HSYNC                                                                                                                               | AD21                                                                         | VDD33 | B <sub>2</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 1 horizontal sync. While intended to be associated with port 1, it can be programmed for use with port 2.                                                                                                                                                                                                                                                                                                                                                             |  |

| P2_A9<br>P2_A8<br>P2_A7<br>P2_A6<br>P2_A5<br>P2_A4<br>P2_A3<br>P2_A4<br>P2_A3<br>P2_A2<br>P2_A1 <sup>(3)</sup><br>P2_A0 <sup>(3)</sup> | AD26<br>AD25<br>AB21<br>AC22<br>AD23<br>AB20<br>AC21<br>AD22<br>AE23<br>AB19 | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 2 A channel input pixel data (bit weight 128)<br>Port 2 A channel input pixel data (bit weight 64)<br>Port 2 A channel input pixel data (bit weight 32)<br>Port 2 A channel input pixel data (bit weight 16)<br>Port 2 A channel input pixel data (bit weight 8)<br>Port 2 A channel input pixel data (bit weight 4)<br>Port 2 A channel input pixel data (bit weight 2)<br>Port 2 A channel input pixel data (bit weight 1)<br>Unused, tie to 0<br>Unused, tie to 0. |  |

| P2_B9<br>P2_B8<br>P2_B7<br>P2_B6<br>P2_B5<br>P2_B4<br>P2_B3<br>P2_B2<br>P2_B2<br>P2_B1 <sup>(3)</sup><br>P2_B0 <sup>(3)</sup>          | Y22<br>AB26<br>AA23<br>AB25<br>AA22<br>AB24<br>AC26<br>AB23<br>AC25<br>AC24  | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 2 B channel input pixel data (bit weight 128)<br>Port 2 B channel input pixel data (bit weight 64)<br>Port 2 B channel input pixel data (bit weight 32)<br>Port 2 B channel input pixel data (bit weight 16)<br>Port 2 B channel input pixel data (bit weight 8)<br>Port 2 B channel input pixel data (bit weight 4)<br>Port 2 B channel input pixel data (bit weight 2)<br>Port 2 B channel input pixel data (bit weight 1)<br>Unused, tie to 0<br>Unused, tie to 0. |  |

| P2_C9<br>P2_C8<br>P2_C7<br>P2_C6<br>P2_C5<br>P2_C4<br>P2_C3<br>P2_C4<br>P2_C3<br>P2_C2<br>P2_C1 <sup>(3)</sup><br>P2_C0 <sup>(3)</sup> | W23<br>V22<br>Y26<br>Y25<br>Y24<br>Y23<br>W22<br>AA26<br>AA25<br>AA24        | VDD33 | l <sub>4</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 2 C channel input pixel data (bit weight 128)<br>Port 2 C channel input pixel data (bit weight 64)<br>Port 2 C channel input pixel data (bit weight 32)<br>Port 2 C channel input pixel data (bit weight 16)<br>Port 2 C channel input pixel data (bit weight 8)<br>Port 2 C channel input pixel data (bit weight 4)<br>Port 2 C channel input pixel data (bit weight 2)<br>Port 2 C channel input pixel data (bit weight 1)<br>Unused, tie to 0<br>Unused, tie to 0. |  |

| P2_VSYNC                                                                                                                               | U22                                                                          | VDD33 | B <sub>2</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 2 vertical sync. While intended to be associated with port 2, it can be programmed for use with port 1.                                                                                                                                                                                                                                                                                                                                                               |  |

| P2_HSYNC                                                                                                                               | W26                                                                          | VDD33 | B <sub>2</sub><br>D | P_CLK1,<br>P_CLK2, or<br>P_CLK3 | Port 2 horizontal sync. While intended to be associated with port 2, it can be programmed for use with port 1.                                                                                                                                                                                                                                                                                                                                                             |  |

| RESERVED_H23                                                                                                                           | H23                                                                          | VDD33 | B <sub>2</sub>      | N/A                             | Connects to BUS_SELECT signal on Primary Controller, must<br>be left unconnected for Secondary Controller                                                                                                                                                                                                                                                                                                                                                                  |  |

| RESERVED_G23                                                                                                                           | G23                                                                          | VDD33 | B <sub>2</sub>      | N/A                             | Connects to HDMI_CEC signal on Primary Controller, must be left unconnected for Secondary Controller                                                                                                                                                                                                                                                                                                                                                                       |  |

(1) Refer to I/O Type and Subscript Definition (Table 4-15).

(2) Refer to the Section 7.2.2 and the Section 7.2.1 for a description between a one controller and a two controller configuration.

(3) Port 1 and Port 2 are capable of 24 bits each. A maximum of 8-bits is available in each of the A, B, and C channels. The 8-bit color inputs are connected to bits [9:2] of the corresponding A, B, C input channels. Sources feeding 8 bits or less per color component channel are MSB justified when connected to the DLPC900, and the LSBs tied to ground along with the data lines 0 and 1 from every channel. Three port clocks options (1, 2, and 3) are provided to improve the signal integrity.

(4) Ports 1 and 2 can be used separately as two 24-bit ports, or can be combined into one 48-bit port (typically, for high data rate sources) for transmission of two pixels per clock.

(5) The A, B, C input data channels of ports 1 and 2 can be internally reconfigured or remapped for optimum board layout. Specifically, each channel can individually remapped to the internal GBR channels. For example, G data can be connected to channel A, B, or C and remapped to be appropriate channel internally. Port configuration and channel multiplexing is handled in the API software.

DLPC900 DLPS037H – OCTOBER 2014 – REVISED JUNE 2024

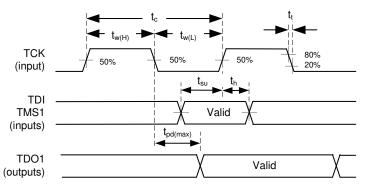

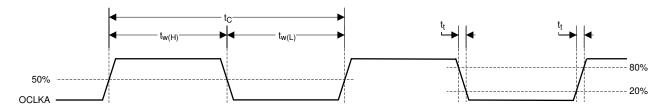

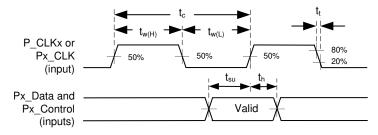

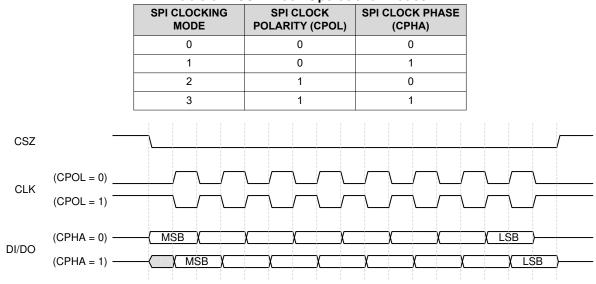

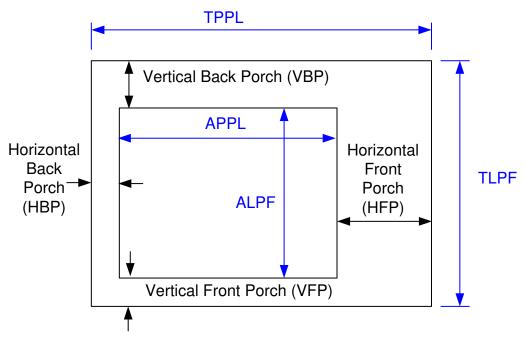

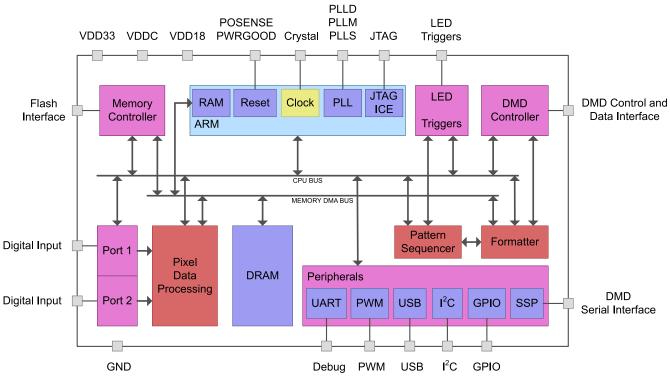

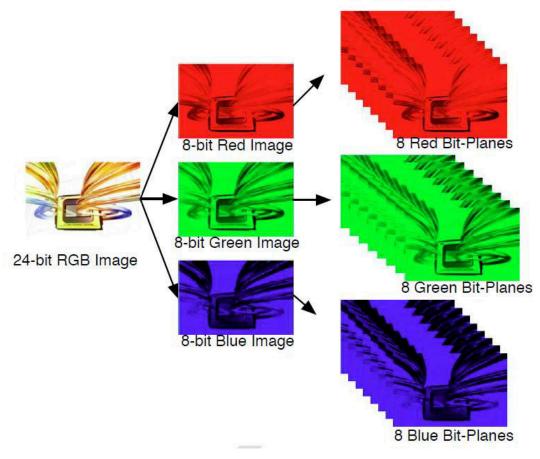

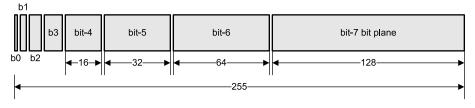

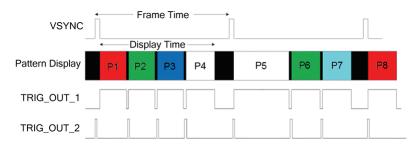

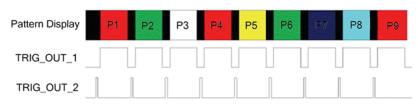

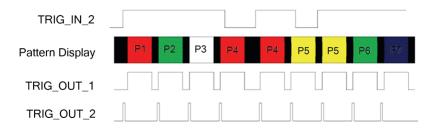

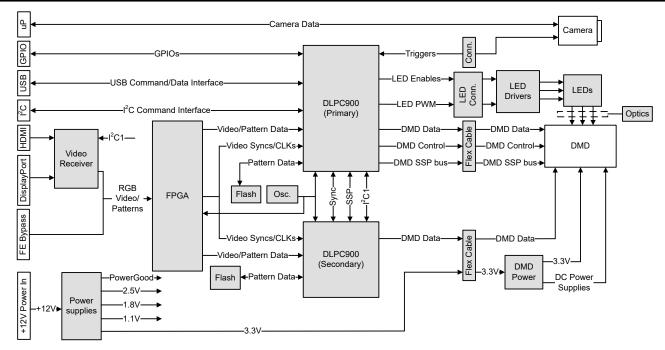

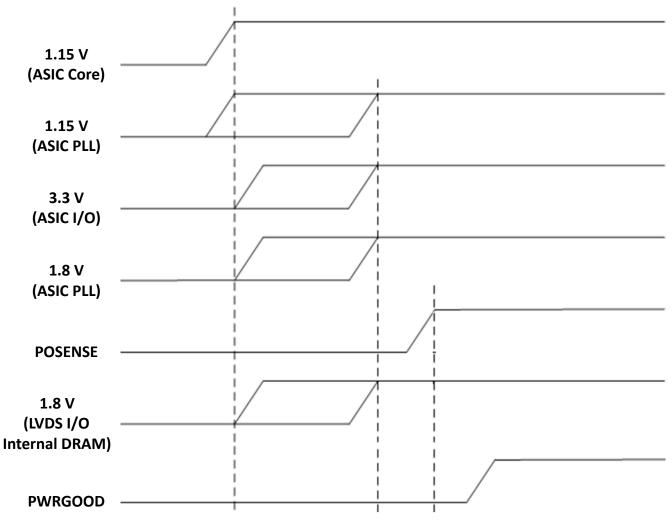

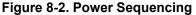

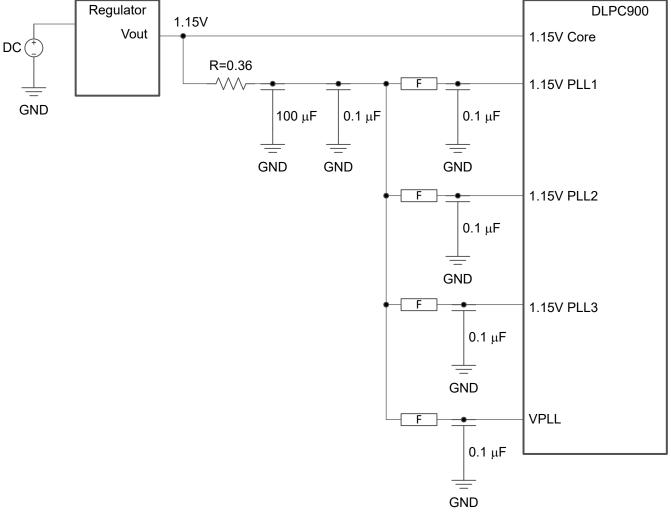

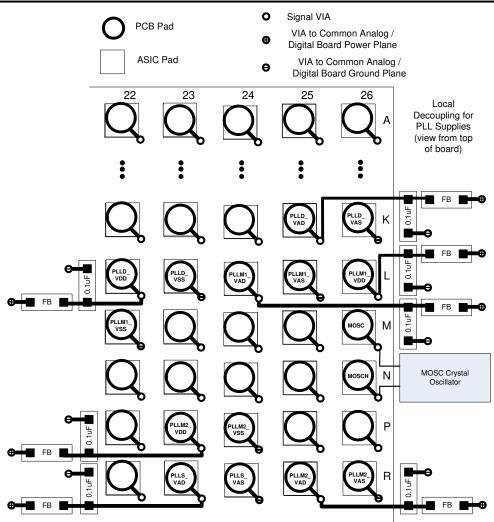

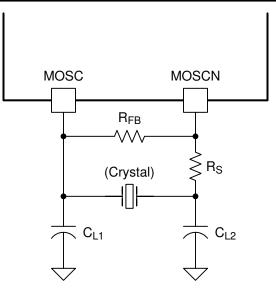

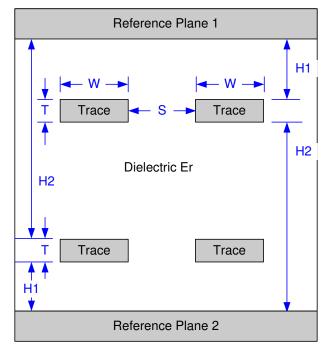

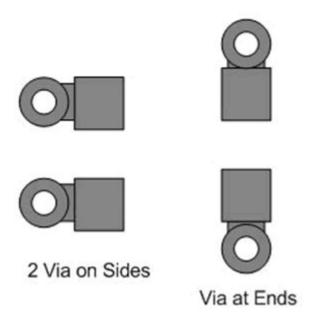

## Table 4-6. Clock and PLL Support Pin Functions