# **THCV2911B-B Datasheet**

www.digi-electronics.com

https://www.DiGi-Electronics.com

DiGi Electronics Part Number THCV2911B-B-DG

Manufacturer THine Solutions, Inc.

Manufacturer Product Number THCV2911B-B

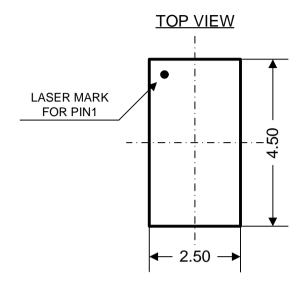

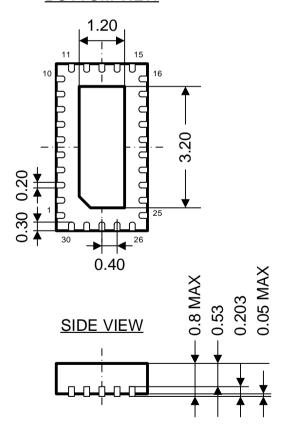

Description 2LANE V-BY-ONEHS REPEATER 30QFN

Detailed Description 4Gbps Serializer/Deserializer 2 Input 2 Output 30-Q

FN (2.5x4.5)

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

## **Purchase and inquiry**

| Manufacturer Product Number: | Manufacturer:          |

|------------------------------|------------------------|

| THCV2911B-B                  | THine Solutions, Inc.  |

| Series:                      | Product Status:        |

| V-by-One® HS                 | Active                 |

| Function:                    | Data Rate:             |

| Serializer/Deserializer      | 4Gbps                  |

| Input Type:                  | Output Type:           |

| V-by-One®HS                  | V-by-One®HS            |

| Number of Inputs:            | Number of Outputs:     |

| 2                            | 2                      |

| Voltage - Supply:            | Operating Temperature: |

| 3V ~ 3.6V                    | -40°C ~ 105°C          |

| Mounting Type:               | Package / Case:        |

| Surface Mount                | 30-WFQFN Exposed Pad   |

| Supplier Device Package:     |                        |

| 30-QFN (2.5x4.5)             |                        |

## **Environmental & Export classification**

| RoHS Status:   | Moisture Sensitivity Level (MSL): |

|----------------|-----------------------------------|

| RoHS Compliant | 3 (168 Hours)                     |

| ECCN:          | HTSUS:                            |

| EAR99          | 8542.90.0000                      |

## THCV2911B

V-by-One® HS Redriver with Linear Equalization

#### General Description

The THCV2911B is low power, high performance active redriver for V-by-One® HS with data rates up to 4Gbps. The THCV2911B pinout is configured as a forward and sub channels.

The THCV2911B features a powerful 18-stages continuous time linear equalizer (CTLE) to provide a boost of up to +10.6dB at 2GHz and open an input eye that is completely closed due to inter-symbol interference (ISI) induced by the inter-connect mediums such as cable or FR-4.

The programmable settings can be applied via pin configurations which eliminates the needs for an external microprocessor and software driver.

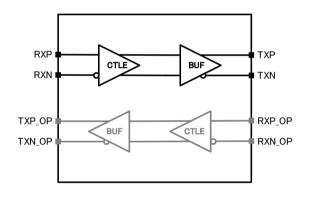

#### **Block Diagram**

#### **Features**

- Signal Conditioning with Linear Equalizer

- A forward and optional lane Redriver for up to 4 Gbps

- Linear Equalization up to +10.6dB@2GHz

- Adjustable Receiver Equalization and DC Gain

- Programmable via Pin Selection

- Flow-Thru Pinout

- Single Supply Voltage (3.3V)

- ESD HBM  $< \pm 4kV$

- Package: QFN30 (2.5mm x 4.5mm)

- -40 to 105°C Operating Temperature

#### **Applications**

All V-by-One® HS applications for reach extension such as

- Digital Signage

- Digital blackboard

- Multi-Function Printer

- Production Printer

- Medical imaging

- Machine vision

- Image Sensor

- Camera

- Active Cable

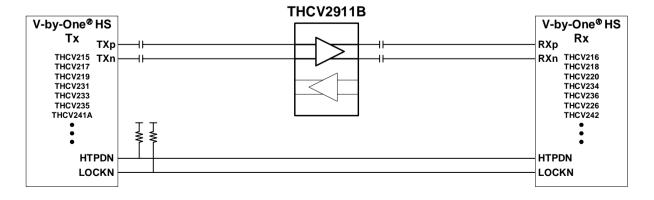

### **Typical Application**

Copyright(C)2020 THine Electronics, Inc.

THine Electronics, Inc.

SC: E

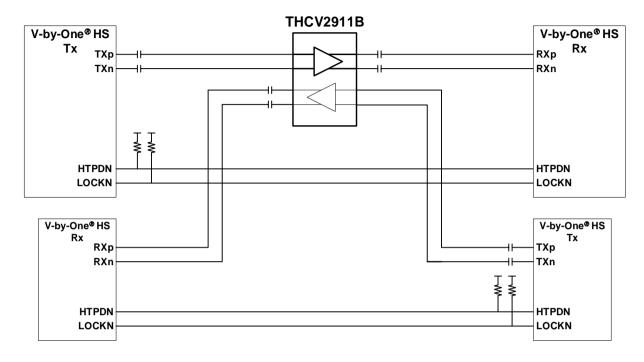

## **Optional Application**

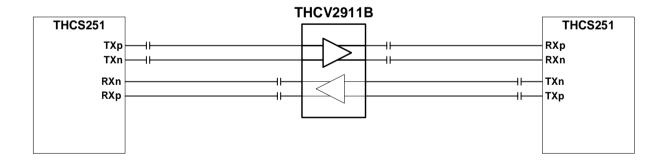

## Optional Application with THCS251

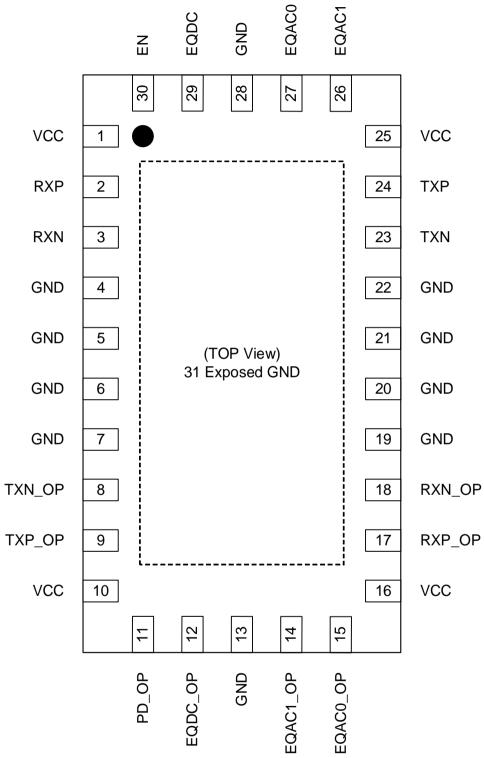

## **Pin Configuration**

## **Pin Description**

| Pin Name  | Pin No        | Туре        | Description                                                      |

|-----------|---------------|-------------|------------------------------------------------------------------|

| RXP       | 2             | CI          | High-Speed CML Signal Input of Main-Lane                         |

| RXN       | 3             | CI          | High-Speed CML Signal Input of Main-Lane                         |

| TXP       | 24            | CO          | High-Speed CML Signal Output of Main-Lane                        |

| TXN       | 23            | CO          | High-Speed CML Signal Output of Main-Lane                        |

| RXP_OP    | 17            | CI          | High-Speed CML Signal Input of Optional-Lane(OP)                 |

| RXN_OP    | 18            | CI          | High-Speed CML Signal Input of OP                                |

| TXP_OP    | 9             | CO          | High-Speed CML Signal Output of OP                               |

| TXN_OP    | 8             | CO          | High-Speed CML Signal Output of OP                               |

| EN        | 30            | I           | Channel Enable. 0 : Power Down 1 : Normal Operation              |

| EQAC1     | 26            | 3LI         | Main Rx Equalizer Peak Gain Setting                              |

| LQACT     | 20            | (*1)        | This pin along with EQAC0 allows for up to 6 settings.           |

| EQAC0     | 27            | 3LI         | Main Rx Equalizer Peak Gain Setting                              |

| LQACO     | 21            | (*1)        | This pin along with EQAC1 allows for up to 6 settings.           |

| EQAC1 OP  | 14            | 3LI         | OP Rx Equalizer Peak Gain Setting                                |

| LQACI_OI  | 14            | (*1)        | This pin along with EQAC0_OP allows for up to 6 settings.        |

| EQAC0 OP  | 15            | 3LI         | OP Rx Equalizer Peak Gain Setting                                |

| EQ/100_01 | 10            | (*1)        | This pin along with EQAC1_OP allows for up to 6 settings.        |

| EQDC      | 29            | 3LI<br>(*1) | Main Equalizer DC Gain Setting                                   |

| EQDC_OP   | 12            | 3LI<br>(*1) | OP Equalizer DC Gain Setting                                     |

| PD_OP     | 11            | 3LI<br>(*1) | Chip Operation Mode Select, if EN=1 F: OP Enable, 1: OP Disable, |

| VCC       | 1, 10, 16, 25 | PWR         | Power Supply Pin for On-chip Regulator.                          |

|           | 4,5,6,7,13,   |             | Ground. Must be tied to the PCB ground plane through an          |

| GND       | 19,20,21,     | GND         | array of vias.                                                   |

|           | 22,28,31      |             | Pin#31 is exposed pad ground.                                    |

CI: CML Input Buffer, CO: CML Output Buffer

I: LVCMOS Input Buffer, 3LI: 3-Level LVCMOS Input Buffer,

PWR: Power Supply, GND: Ground

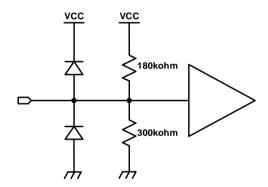

<sup>\*1 : 3-</sup>Level Input Buffer. With internal  $180k\Omega$  pull-up resistor and  $300k\Omega$  pull-down resistor.

## **Operation Mode Settings**

**Table 1. Operation Mode Settings**

| Pin | Settings | Operation Made   |

|-----|----------|------------------|

| EN  | PD_OP    | Operation Mode   |

|     | 0(*1)    | Reserved         |

| 1   | F(*2)    | OP Enable        |

|     | 1(*3)    | OP Disable       |

| 0   | Ignore   | Chip Power Down. |

<sup>\*1</sup> Tie  $0\Omega$  to GND

### **Linear Equalizer Settings**

**Table 2. Linear Equalizer Settings**

|            |            |           |                 | Equ                | alizer Setting     | s (dB)             |                    |     |   |   |   |   |     |     |     |     |     |

|------------|------------|-----------|-----------------|--------------------|--------------------|--------------------|--------------------|-----|---|---|---|---|-----|-----|-----|-----|-----|

| EQAC1(_OP) | EQAC0(_OP) | EQDC(_OP) | Up to<br>0.1GHz | @0.5GHz<br>(1Gbps) | @1.0GHz<br>(2Gbps) | @1.5GHz<br>(3Gbps) | @2.0GHz<br>(4Gbps) |     |   |   |   |   |     |     |     |     |     |

| 0          | *          | *         |                 |                    | Reserved           |                    |                    |     |   |   |   |   |     |     |     |     |     |

| F          | 0          |           |                 | 0.2                | 0.8                | 1.2                | 1.6                |     |   |   |   |   |     |     |     |     |     |

| F          | F          |           |                 | 0.5                | 1.7                | 2.7                | 3.7                |     |   |   |   |   |     |     |     |     |     |

| F          | 1          | 0         | -0.9            | 0.6                | 2.1                | 3.5                | 4.8                |     |   |   |   |   |     |     |     |     |     |

| 1          | 0          | U         | -0.9            | 0.8                | 2.4                | 4.0                | 5.5                |     |   |   |   |   |     |     |     |     |     |

| 1          | F          |           |                 | 1.3                | 3.7                | 5.9                | 7.9                |     |   |   |   |   |     |     |     |     |     |

| 1          | 1          |           |                 | 1.5                | 4.2                | 6.6                | 8.8                |     |   |   |   |   |     |     |     |     |     |

| F          | 0          | F         |                 |                    | 2.6                | 3.1                | 3.4                | 3.5 |   |   |   |   |     |     |     |     |     |

| F          | F          |           |                 | 2.8                | 3.7                | 4.4                | 5.1                |     |   |   |   |   |     |     |     |     |     |

| F          | 1          |           | F               | F                  | F                  | F                  | F                  | F   | F | F | F | F | 1.6 | 2.9 | 4.1 | 5.0 | 6.0 |

| 1          | 0          |           |                 |                    |                    |                    |                    |     |   |   |   |   | 1.0 | 3.0 | 4.3 | 5.4 | 6.6 |

| 1          | F          |           |                 |                    |                    |                    |                    |     |   |   |   |   |     |     |     | 3.4 | 5.2 |

| 1          | 1          |           |                 | 3.5                | 5.6                | 7.5                | 9.4                |     |   |   |   |   |     |     |     |     |     |

| F          | 0          |           |                 | 6.5                | 6.8                | 6.9                | 6.8                |     |   |   |   |   |     |     |     |     |     |

| F          | F          |           |                 | 6.6                | 7.2                | 7.5                | 7.9                |     |   |   |   |   |     |     |     |     |     |

| F          | 1          | 1 5.7     | <i>5</i> 7      | 6.7                | 7.4                | 7.8                | 8.3                |     |   |   |   |   |     |     |     |     |     |

| 1          | 0          |           | 5.7             | 6.7                | 7.5                | 8.1                | 8.7                |     |   |   |   |   |     |     |     |     |     |

| 1          | F          |           |                 | 6.9                | 8.0                | 9.1                | 10.2               |     |   |   |   |   |     |     |     |     |     |

| 1          | 1          |           |                 | 7.0                | 8.2                | 9.5                | 10.6               |     |   |   |   |   |     |     |     |     |     |

Average of all channels in typical condition

<sup>\*2</sup> Leave pin Open

<sup>\*3</sup> Tie  $0\Omega$  to VCC

## **Absolute Maximum Ratings**

**Table 3. Absolute Maximum Ratings**

| Pai          | ameter                         | Min  | Тур | Max     | Unit   |

|--------------|--------------------------------|------|-----|---------|--------|

| Supply \     | oltage(VCC)                    | -0.3 | -   | 4.0     | V      |

| LVCMOS Inp   | ut/Output Voltage              | -0.3 | -   | VCC+0.3 | V      |

| 3-Level LVCM | IOS Input Voltage              | -0.3 | -   | VCC+0.3 | V      |

| CML Receiv   | CML Receiver Input Voltage     |      |     | VCC+0.3 | V      |

| CML Transmit | CML Transmitter Output Voltage |      | -   | VCC+0.3 | V      |

| ESD Boting   | HBM                            | -    | -   | ±4      | kV     |

| ESD Rating   | CDM                            | -    | -   | ±1000   | V      |

| Storage      | Storage Temperature            |      | -   | 125     | °C     |

| Junction     | Junction Temperature           |      | -   | 125     | °C     |

| Reflow Peak  | Temperature/Time               | -    | -   | 260/10  | °C/sec |

## **Recommended Operating Conditions**

**Table 4. Recommended Operating Conditions**

| Parameter               | Min | Тур | Max           | Unit |

|-------------------------|-----|-----|---------------|------|

| Supply Voltage(VCC)     | 3.0 | 3.3 | 3.6           | V    |

| Supply Ramp Requirement | 0.1 | -   | 50            | ms   |

| Operating Temperature   | -40 | -   | 105<br>85(*1) | °C   |

(\*1) PD\_OP=F

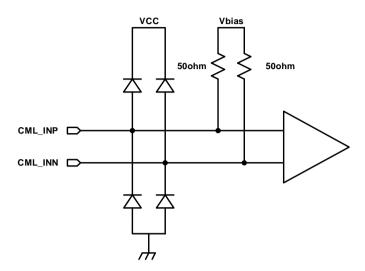

## **Equivalent CML Input Schematic Diagram**

Figure 1. CML Input Schematic Diagram

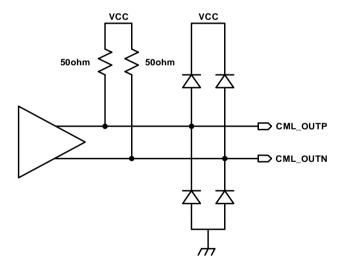

### **Equivalent CML Output Schematic Diagram**

Figure 2. CML Output Schematic Diagram

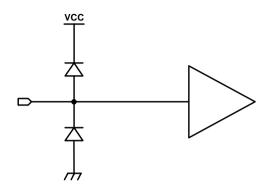

## **Equivalent LVCMOS Input Schematic Diagram**

Figure 3. LVCMOS Input Schematics Diagram

## **Equivalent 3-Level LVCMOS Input Schematic Diagram**

Figure 4. 3-Level Input Schematics Diagram

## **Electrical Specification**

Supply Current

#### **Table 5. Supply Current**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol                          | Parameter                  | Condition | Min | Тур | Max | Unit |

|---------------------------------|----------------------------|-----------|-----|-----|-----|------|

| ICCW Active Mode Supply Current | Active Made Supply Current | PD_OP=1   | -   | 58  | 84  | mA   |

|                                 | Active Mode Supply Current | PD_OP=F   | -   | 84  | 106 | mΑ   |

| ICCS                            | Power Down Supply Current  | -         | -   | 120 | 180 | uA   |

#### LVCMOS DC Specification

#### **Table 6. LVCMOS DC Specification**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol | Parameter                | Condition | Min | Тур | Max | Unit |

|--------|--------------------------|-----------|-----|-----|-----|------|

| VIH    | High Level Input Voltage | -         | 2.0 | -   | VCC | V    |

| VIL    | Low Level Input Voltage  | -         | 0   | -   | 0.7 | V    |

#### 3-Level LVCMOS DC Specification

#### Table 7. 3-Level LVCMOS DC Specification

Over recommended operating supply and temperature range unless otherwise specified

| Symbol             | Parameter                        | Condition | Min            | Тур | Max            | Unit |

|--------------------|----------------------------------|-----------|----------------|-----|----------------|------|

| VTHL               | Low Level Input<br>Voltage       | 0(*1)     | 0              | -   | VCC*0.25 - 0.3 | ٧    |

| VTHF               | F-Level Input Voltage            | F(*2)     | VCC*0.5 + 0.3  | -   | VCC*0.75 - 0.3 | V    |

| V <sub>THH</sub>   | High Level Input<br>Voltage      | 1(*3)     | VCC*0.75 + 0.3 | -   | VCC            | ٧    |

| I <sub>IH_3L</sub> | High level Input Leak<br>Current | VIN=VCC   | -100           | -   | 100            | uA   |

| I <sub>IL_3L</sub> | Low Level Input Leak<br>Current  | VIN=GND   | -100           | -   | 100            | uA   |

### Receiver DC Specification

### **Table 8. Receiver DC Specification**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol | Parameter                                | Condition      | Min | Тур | Max | Unit |

|--------|------------------------------------------|----------------|-----|-----|-----|------|

| VRTH   | CML Differential Input High<br>Threshold | -              | -   | -   | 50  | mV   |

| VRTL   | CML Differential Input Low<br>Threshold  | -              | -50 | -   | -   | mV   |

| IRIH   | CML Input Leak Current High              | EN=0,RXP/N=VCC | -10 | -   | 10  | uA   |

| IRIL   | CML Input Leak Current Low               | EN=0,RXP/N=GND | -10 | -   | 10  | uA   |

| RRIN   | CML Differential Input Resistance        | -              | •   | 100 | -   | Ω    |

#### Transmitter DC Specifications

#### **Table 9.Transmitter DC Specifications**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol | Parameter                       | Condition | Min | Тур      | Max | Unit |

|--------|---------------------------------|-----------|-----|----------|-----|------|

| VTOC   | CML Common mode Output Voltage  | -         | -   | VCC-0.75 | -   | V    |

| ITOH   | CML Output Leak Current<br>High | EN=0      | -   | -        | 50  | uA   |

#### **AC Specifications**

#### **Table 10. AC Specification**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol                | Parameter                      | Condition | Min | Тур | Max | Unit |

|-----------------------|--------------------------------|-----------|-----|-----|-----|------|

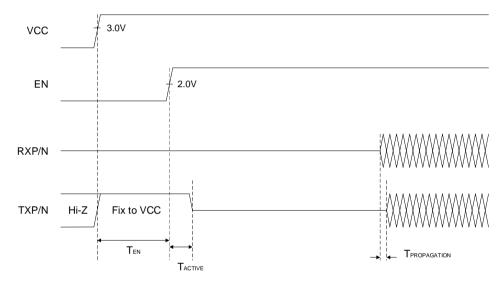

| T <sub>EN</sub>       | Power On to EN High Delay      | -         | 0   | -   | -   | ns   |

| TACTIVE               | EN High to Active Delay        | -         | -   | -   | 200 | us   |

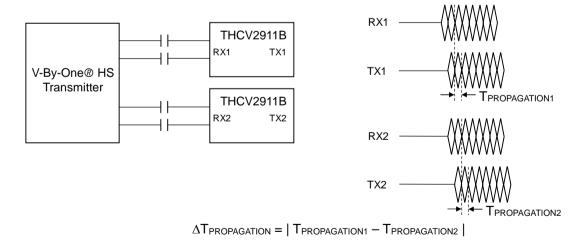

| TPROPAGATION          | Differential Propagation Delay | -         | -   | 150 | -   | ps   |

| $\DeltaT_PROPAGATION$ | Delta Propagation Delay        | -         | -   | -   | 40  | ps   |

Figure 5. Power on Sequence

Figure 6. CML Propagation Delay Timing

Copyright(C)2020 THine Electronics,Inc.

THine Electronics, Inc.

**Table 11. Transmitter AC Specification**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol | Parameter         | Condition   | Min | Тур | Max | Unit |

|--------|-------------------|-------------|-----|-----|-----|------|

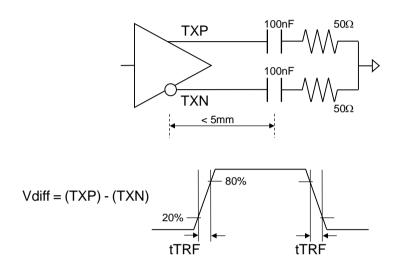

| tTRF   | Tx Rise/Fall Time | 20% to 80 % | 50  | -   | 150 | ps   |

Figure 7. CML Output Switching Timing and Test Circuit

## **Package**

## **BOTTOM VIEW**

Unit: mm

THCV2911B Rev.1.10 E

#### **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note even if errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without THine's prior permission is prohibited.

- 4. Note that even if infringement of any third party's industrial ownership should occur by using this product, THine will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

- 5. Product Application

- 5.1 Application of this product is intended for and limited to the following applications: audio-video device, office automation device, communication device, consumer electronics, smartphone, feature phone, and amusement machine device. This product must not be used for applications that require extremely high-reliability/safety such as aerospace device, traffic device, transportation device, nuclear power control device, combustion chamber device, medical device related to critical care, or any kind of safety device.

- 5.2 This product is not intended to be used as an automotive part, unless the product is specified as a product conforming to the demands and specifications of IATF16949 ("the Specified Product") in this data sheet. Thine accepts no liability whatsoever for any product other than the Specified Product for it not conforming to the aforementioned demands and specifications.

- 5.3 THine accepts liability for demands and specifications of the Specified Product only to the extent that the user and THine have been previously and explicitly agreed to each other.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 9. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Act.

- 10. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses.

## THine Electronics, Inc.

https://www.thine.co.jp

## **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935