# PI6LC48S25BZBBIEX Datasheet

https://www.DiGi-Electronics.com

DiGi Electronics Part Number PI6LC48S25BZBBIEX-DG

Manufacturer Diodes Incorporated

Manufacturer Product Number PI6LC48S25BZBBIEX

Description IC CLOCK GENERATOR 56TQFN

Detailed Description Clock Generator IC 312.5MHz 1 56-VFQFN Exposed

Pad

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com

DiGi is a global authorized distributor of electronic components.

# **Purchase and inquiry**

| Manufacturer Draduct Number    | Manufacturer                 |

|--------------------------------|------------------------------|

| Manufacturer Product Number:   | Manufacturer:                |

| PI6LC48S25BZBBIEX              | Diodes Incorporated          |

| Series:                        | Product Status:              |

| HiFlex™                        | Active                       |

| DiGi-Electronics Programmable: | Type:                        |

| Not Verified                   | Clock Generator              |

| PLL:                           | Input:                       |

| Yes with Bypass                | CMOS, Crystal                |

| Output:                        | Number of Circuits:          |

| LVDS, LVPECL                   | 1                            |

| Ratio - Input:Output:          | Differential - Input:Output: |

| 3:11                           | Yes/Yes                      |

| Frequency - Max:               | Divider/Multiplier:          |

| 312.5MHz                       | Yes/No                       |

| Voltage - Supply:              | Operating Temperature:       |

| 2.375V ~ 3.63V                 | -40°C ~ 85°C (TA)            |

| Mounting Type:                 | Package / Case:              |

| Surface Mount                  | 56-VFQFN Exposed Pad         |

| Supplier Device Package:       | Base Product Number:         |

| 56-TQFN (8x8)                  | PI6LC48                      |

|                                |                              |

# **Environmental & Export classification**

| RoHS Status:     | Moisture Sensitivity Level (MSL): |

|------------------|-----------------------------------|

| ROHS3 Compliant  | 1 (Unlimited)                     |

| REACH Status:    | ECCN:                             |

| REACH Unaffected | EAR99                             |

| HTSUS:           |                                   |

8542.39.0001

Next Generation HiFlex<sup>TM</sup> Ethernet Network Clock Generator

#### **Features**

- → 3.3V & 2.5V supply voltage

- → Crystal/CMOS input: 25 MHz

- → Differential input: 25MHz, 125MHz, and 156.25 MHz

- → Output frequencies: 312.5, 156.25, 125, 100, 50, 25MHz

- → 4 Output banks with selectable output signaling: LVPECL or LVDS

- → Low 0.3ps typical integrated phase noise design: 156.25MHz (12kHz to 20MHz)

- → PLL Bypass mode for test

- → Power supply noise rejection: -52 dBc typical @ VDD

- → Packaging (Pb-free & Green): 56-lead 8×8mm TQFN

- → Industrial temperature support: -40C to 85C

### **Description**

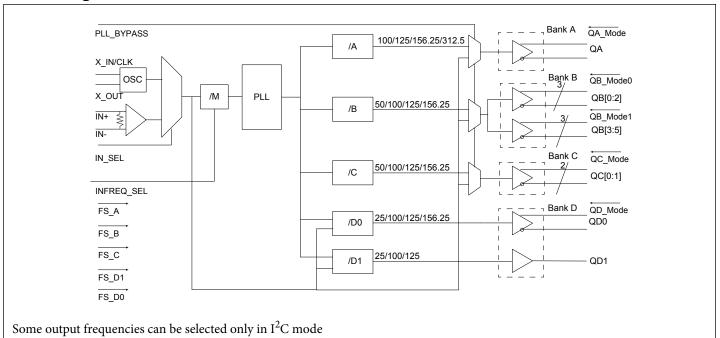

The PI6LC48S25B is an LC VCO based low phase noise design intended for 10GbE applications. Typical 10GbE usage assumes a 25MHz crystal input, while the PLL loop is used to generate the 156.25MHz and other Ethernet clock frequencies. An additional buffered crystal oscillator output is provided to serve as a low noise reference for other circuitry.

For Ethernet applications other than 10GbE, programmable dividers allow for simultaneous output of 312.5, 156.25, 125, 100, 50, and 25MHz. This device offers both pin selection and  $I^2C$  interface to give more options to meet various system needs.

### **Block Diagram**

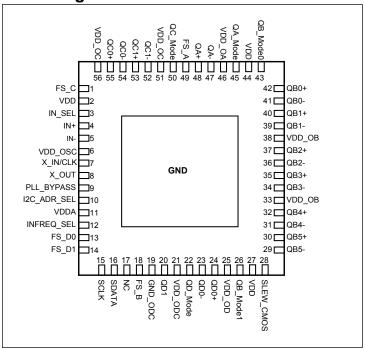

# **Pin Configuration**

### **Pin Description**

| Pin #     | Pin Name    | Туре             |           | Description                                                              |

|-----------|-------------|------------------|-----------|--------------------------------------------------------------------------|

| 1         | FS_C        | Input            | Tri-level | Output frequency select for Bank C output                                |

| 2, 27, 44 | VDD         | Power            | -         | Core supply                                                              |

| 3         | IN_SEL      | Input            | CMOS      | Input select between Xtal and differential input                         |

| 4         | IN+         | Input            | LVPECL    | Differential reference input, also accepts AC-coupled LVDS, CML, HCSL or |

| 5         | IN-         | Input            | LVPECL    | LVPECL. Differential inputs have an internal $100\Omega$ cross resistor. |

| 6         | VDD_OSC     | Power            | -         | Power supply for Xtal Oscillator circuit                                 |

| 7         | X_IN/CLK    | Input            |           | Xtal or clock input, connect to a 25MHz Xtal or single-ended clock       |

| 8         | X_OUT       | Output           |           | Xtal output                                                              |

| 9         | PLL_BYPASS  | Input            | CMOS      | PLL bypass, provide input frequency to Bank A, BankB, and Bank C         |

| 10        | I2C_ADR_SEL | Input            | CMOS      | I2C address selection.                                                   |

| 11        | VDDA        | Power            | -         | Analog supply                                                            |

| 12        | INFREQ_SEL  | Input            | Tri-level | Input frequency selection for reference input                            |

| 13        | FS_D0       | Input            | Tri-level | Output frequency select for Bank D differential output                   |

| 14        | FS_D1       | Input            | Tri-level | Output frequency select for Bank D CMOS output                           |

| 15        | SCLK        | Input            |           | I <sup>2</sup> C clock input                                             |

| 16        | SDATA       | Input/<br>Output |           | I <sup>2</sup> C Data line                                               |

# Pin Description Cont.

| Pin #  | Pin Name Type |        | pe              | Description                                  |  |

|--------|---------------|--------|-----------------|----------------------------------------------|--|

| 17     | NC            |        |                 | Reserved pin. Do not connect this pin        |  |

| 18     | FS_B          | Input  | Tri-level       | Output frequency select for Bank B           |  |

| 19     | GND_ODC       | Power  |                 | Ground for bank D CMOS output                |  |

| 20     | QD1           | Output | CMOS            | Bank D output 1                              |  |

| 21     | VDD_ODC       | Power  |                 | Power supply for bank D CMOS output          |  |

| 22     | QD_Mode       | Input  | Tri-level       | Bank D differential output control           |  |

| 23, 24 | QD0-, QD0+    | Output | LVPECL/<br>LVDS | Bank D differential output                   |  |

| 25     | VDD_OD        | Power  |                 | Power supply for bank D differential outputs |  |

| 26     | QB_Mode1      | Input  | Tri-level       | Bank B QB3 ~ QB5 differential output control |  |

| 28     | SLEW_CMOS     | Input  | CMOS            | Output slew rate control for the CMOS output |  |

| 29, 30 | QB5-, QB5+    | Output | LVPECL/<br>LVDS | Bank B differential output                   |  |

| 31, 32 | QB4-, QB4+    | Output | LVPECL/<br>LVDS | Bank B differential output                   |  |

| 33, 38 | VDD_OB        | Power  |                 | Power supply for bank B differential outputs |  |

| 34, 35 | QB3-, QB3+    | Output | LVPECL/<br>LVDS | Bank B differential output                   |  |

| 36, 37 | QB2-, QB2+    | Output | LVPECL/<br>LVDS | Bank B differential output                   |  |

| 39, 40 | QB1-, QB1+    | Output | LVPECL/<br>LVDS | Bank B differential output                   |  |

| 41, 42 | QB0-, QB0+    | Output | LVPECL/<br>LVDS | Bank B differential output                   |  |

| 43     | QB_Mode0      | Input  | Tri-level       | Bank B QB0 ~ QB2 differential output control |  |

| 45     | QA_Mode       | Input  | Tri-level       | Bank A differential output control           |  |

| 46     | VDD_OA        | Power  |                 | Power supply for bank A differential outputs |  |

| 47, 48 | QA-, QA+      | Output | LVPECL/<br>LVDS | Bank A differential output                   |  |

| 49     | FS_A          | Input  | Tri-level       | Output frequency select for Bank A           |  |

| 50     | QC_Mode       | Input  | Tri-level       | Bank C differential output control           |  |

| 51, 56 | VDD_OC        | Power  |                 | Power supply for bank A differential outputs |  |

| 52, 53 | QC1-, QC1+    | Output | LVPECL/<br>LVDS | Bank C differential output                   |  |

| 54, 55 | QC0-, QC0+    | Output | LVPECL/<br>LVDS | Bank C differential output                   |  |

| E-pad  | GND           | Power  |                 | Connect to ground, use thermal vias          |  |

# **Input MUX Selection**

| IN_SEL | Input Source                    |  |

|--------|---------------------------------|--|

| 0      | Crystal Input (X_IN/CLK, X_OUT) |  |

| 1      | Differential Input (IN+, IN-)   |  |

| NC     | Crystal Input (X_IN/CLK, X_OUT) |  |

# **Reference Input Frequency Select Table**

| INFREQ_SEL | Reference Input |

|------------|-----------------|

| 0          | 25MHz           |

| 1          | 125MHz          |

| NC         | 156.25MHz       |

# **PLL Bypass Control Function**

| PLL_BYPASS | PLL operation |

|------------|---------------|

| 0          | PLL enabled   |

| 1          | PLL bypassed  |

# Bank A/B/C/D Differential Output Control

| QA_<br>Mode | QA     | QB_<br>Mode0 | QB[2:0] | QB_<br>Mode1 | QB[5:3] | QC_<br>Mode | QC[1:0] | QD_<br>Mode | QD0    |

|-------------|--------|--------------|---------|--------------|---------|-------------|---------|-------------|--------|

| 0           | LVPECL | 0            | LVPECL  | 0            | LVPECL  | 0           | LVPECL  | 0           | LVPECL |

| 1           | LVDS   | 1            | LVDS    | 1            | LVDS    | 1           | LVDS    | 1           | LVDS   |

| NC          | Hi-Z   | NC           | Hi-Z    | NC           | Hi-Z    | NC          | Hi-Z    | NC          | Hi-Z   |

### Bank A/B/C Output Frequency Control Table

| FS_A | Bank A Output<br>Freq. | FS_B | Bank B Output<br>Freq. | FS_C | Bank C Output<br>Freq. |

|------|------------------------|------|------------------------|------|------------------------|

| 0    | 156.25MHz              | 0    | 156.25MHz              | 0    | 156.25MHz              |

| 1    | 125MHz                 | 1    | 125MHz                 | 1    | 125MHz                 |

| NC   | 312.5MHz               | NC   | 50MHz                  | NC   | 100MHz                 |

# **Bank D Output Frequency Control Table**

| FS_D0 | Bank D Diff.<br>Output Freq. | FS_D1 | Bank D CMOS<br>Output Freq. |

|-------|------------------------------|-------|-----------------------------|

| 0     | 156.25MHz                    | 0     | Hi-Z                        |

| 1     | 125MHz                       | 1     | 125MHz                      |

| NC    | $f_{IN}$                     | NC    | $f_{IN}$                    |

# **Output Slew Rate Control Table**

| SLEW_CMOS | Output Slew rate |

|-----------|------------------|

| 0         | Normal mode      |

| 1         | Slow mode        |

# **I2C Address Selection Table**

| I <sup>2</sup> C_ADR_SEL | I2C Address |

|--------------------------|-------------|

| 0                        | DC (h)      |

| 1                        | DE (h)      |

# **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Operating Conditions**

| Symbol            | Parameters                        | Conditions                                   | Min.  | Тур. | Max.  | Units |

|-------------------|-----------------------------------|----------------------------------------------|-------|------|-------|-------|

| V                 | Come Devices Comply Voltage       |                                              | 2.97  | 3.3  | 3.63  | V     |

| $V_{\mathrm{DD}}$ | Core Power Supply Voltage         |                                              | 2.375 | 2.5  | 2.625 | V     |

| 17                | Outmut Davier Cumply Valtage      |                                              | 2.97  | 3.3  | 3.63  | V     |

| $V_{DD\_OX}$      | Output Power Supply Voltage       |                                              | 2.375 | 2.5  | 2.625 | V     |

| 7.7               | A la Daniera Comunica Valta       |                                              | 2.97  | 3.3  | 3.63  | V     |

| $V_{DDA}$         | Analog Power Supply Voltage       |                                              | 2.375 | 2.5  | 2.625 | V     |

| $I_{DD}$          | Power Supply Current              |                                              |       |      | 50    | mA    |

| T                 | Davies Comply Consent for Outputs | All outputs loaded, Diff. outputs are LVPECL |       |      | 525   | mA    |

| $I_{DD\_O}$       | Power Supply Current for Outputs  | All outputs loaded, Diff. outputs are LVDS   |       |      | 242   | mA    |

| I <sub>DDA</sub>  | Analog Power Supply Current       |                                              |       |      | 45    | mA    |

| $T_{A}$           | Ambient Temperature               |                                              | -40   |      | 85    | °C    |

# **Input Electrical Characteristics**

| Symbol          | Parameters                                  | Conditions | Min. | Тур. | Max. | Units |

|-----------------|---------------------------------------------|------------|------|------|------|-------|

| R <sub>pu</sub> | Internal pull up resistance                 |            |      | 51   |      | ΚΩ    |

| R <sub>dn</sub> | Internal pull down resistance               |            |      | 51   |      | ΚΩ    |

| $C_{XTAL}$      | Internal capacitance on X_IN and X_OUT pins |            |      | 12   |      | pF    |

### **LVCMOS DC Electrical Characteristics**

| Symbol           | Parameters            | Conditions                              | Min. | Typ. | Max.                 | Units |

|------------------|-----------------------|-----------------------------------------|------|------|----------------------|-------|

| 37               | T TT' 1 X7 16         | $V_{\rm DD} = 3.3 V \pm 10\%$           | 2    |      | V <sub>DD</sub> +0.3 | V     |

| $V_{IH}$         | Input High Voltage    | $V_{\rm DD} = 2.5 V \pm 5\%$            | 1.7  |      | V <sub>DD</sub> +0.3 | V     |

| 37               | I                     | $V_{\rm DD} = 3.3 V \pm 10\%$           | -0.3 |      | 0.8                  | V     |

| $V_{\rm IL}$     |                       | $V_{\rm DD} = 2.5 V \pm 5\%$            | -0.3 |      | 0.5                  | V     |

| I <sub>IH</sub>  | Input High Current    | $V_{IN} = V_{DD max}$ .                 |      |      | 150                  | μА    |

| I <sub>IL</sub>  | Input Low Current     | $V_{IN} = 0V$                           | -150 |      |                      | μΑ    |

|                  |                       | $V_{DD} = V_{DD\_ODC} = 3.3V \pm 10\%;$ | 2.6  |      |                      | 3.7   |

| 37               | Output High Voltage   | $I_{OH} = -12mA$                        | 2.6  |      |                      | V     |

| V <sub>OH</sub>  |                       | $V_{DD} = V_{DD\_ODC} = 2.5V \pm 5\%;$  | 1.0  |      |                      | V     |

|                  |                       | $I_{OH} = -8mA$                         | 1.8  |      |                      | V     |

|                  |                       | $V_{DD} = V_{DD\_ODC} = 3.3V \pm 10\%;$ |      |      | 0.5                  | V     |

| 3.7              | Octobrill and Walter  | $I_{OH} = 12mA$                         |      |      | 0.5                  | V     |

| $V_{OL}$         | Output Low Voltage    | $V_{DD} = V_{DD\_ODC} = 2.5V \pm 5\%;$  |      |      | 0.5                  | V     |

|                  |                       | $I_{OH} = 8mA$                          |      |      | 0.5                  | V     |

| $T_{DC}$         | Input Duty Cycle      |                                         | 35   |      | 65                   | %     |

| D                | CMOCO + +: 1          | V <sub>DD_ODC</sub> =3.3V               |      | 24   |                      | 0     |

| R <sub>OUT</sub> | CMOS Output impedance | $V_{\rm DD\_ODC}$ =2.5V                 |      | 30   |                      | Ω     |

| C <sub>IN</sub>  | Input Capacitance     |                                         |      | 3.5  |                      | pF    |

# **Differential Input DC Characteristics**

| Symbol             | Parameters                                | Conditions                | Min                   | Тур. | Max.                   | Units |

|--------------------|-------------------------------------------|---------------------------|-----------------------|------|------------------------|-------|

| $V_{\mathrm{IH}}$  | Input High Voltage                        |                           |                       |      | V <sub>DD</sub> - 0.7  | V     |

| $V_{\rm IL}$       | Input Low Voltage                         |                           | V <sub>DD</sub> - 2.0 |      |                        | V     |

| $V_{CM}$           | Input Bias Voltage                        |                           | 0.5                   |      | V <sub>DD</sub> - 0.85 | V     |

| R <sub>IN</sub>    | Input Differential Impedance <sup>1</sup> |                           | 80                    | 100  | 120                    | Ω     |

| V <sub>IN-PP</sub> | Input Differential Swing                  | Differential peak to peak | 0.3                   |      | 2.6                    | V     |

Note: 1. Differential input can be AC or DC coupled.

# **Crystal Characteristic**

| Parameters       | Description                  | Min. | Тур        | Max. | Units |

|------------------|------------------------------|------|------------|------|-------|

| OSCmode          | Mode of Oscillation          |      | Fundamenta | 1    |       |

| FREQ             | Frequency                    | 10   | 25         | 40   | MHz   |

| ESR <sup>1</sup> | Equivalent Series Resistance |      |            | 50   | Ω     |

| Cload            | Load Capacitance             |      | 18         |      | pF    |

| Cshunt           | Shunt Capacitance            |      |            | 7    | pF    |

|                  | Drive Level                  |      |            | 250  | uW    |

$\textbf{Note: 1.} \ ESR \ value \ is \ dependent \ upon \ frequency \ of \ oscillation$

# LVPECL Output DC Characteristics (1)

| Symbol           | Parameters               | Condition                             | Min.                     | Тур. | Max.                     | Units |

|------------------|--------------------------|---------------------------------------|--------------------------|------|--------------------------|-------|

| V <sub>OPP</sub> | Output peak-peak Voltage | Single-ended                          |                          | 0.78 |                          | V     |

| V <sub>OH</sub>  | Output High Voltage      | Outputs terminated with $50\Omega$ to | V <sub>DD_OX</sub> - 1.4 |      | V <sub>DD_OX</sub> - 0.7 | V     |

| V <sub>OL</sub>  | Output Low Voltage       | V <sub>DD_OX</sub> - 2V               | V <sub>DD_OX</sub> - 2.0 |      | V <sub>DD_OX</sub> - 1.3 | V     |

# LVDS Output DC Characteristics (1)

| Symbol            | Parameters                        | Condition    | Min.  | Тур. | Max.  | Units |

|-------------------|-----------------------------------|--------------|-------|------|-------|-------|

| V <sub>OPP</sub>  | Output Peak-peak Voltage          | Single-ended | 0.247 |      | 0.454 | V     |

| DV <sub>OPP</sub> | V <sub>OPP</sub> Magnitude Change |              |       |      | 50    | mV    |

| Vos               | Output Offset Voltage             |              | 1.125 |      | 1.375 | V     |

| DVOS              | V <sub>OS</sub> Magnitude Change  |              |       |      | 50    | mV    |

# AC Output Characteristics (see test configurations) <sup>(1)</sup>

$T_A$ =-40C to 85C;  $V_{DD}$ =3.3V±10%,  $V_{DD}$  O=3.3V±10%

| Symbol              | Parameters                      | Condition                                    |                            | Min. | Тур. | Max.  | Units  |

|---------------------|---------------------------------|----------------------------------------------|----------------------------|------|------|-------|--------|

|                     |                                 | LVCMOS                                       |                            |      |      | 125   | MHz    |

| $f_{OUT}$           | Output Frequency                | LVPECL                                       |                            |      |      | 312.5 | MHz    |

|                     |                                 | LVDS                                         |                            |      |      | 312.5 | MHz    |

|                     | Dia 1 F.11 Tim.                 | LUCMOS                                       | Normal Mode <sup>(2)</sup> | 150  | 400  | 850   | ps     |

| t <sub>R/tF</sub>   | Rise and Fall Time;<br>20% ~80% | LVCMOS                                       | Slow Mode <sup>(3)</sup>   |      |      | 2.0   | ns     |

|                     | 20% ~80%                        | LVPECL, LVDS                                 |                            |      | 250  | 400   | ps     |

|                     |                                 | LVCMOS                                       |                            | 45   |      | 55    | %      |

| $t_{DC}$            | Duty Cycle                      | LVPECL, LVDS                                 |                            | 48   |      | 52    | %      |

|                     |                                 | Bank A at 312.5                              | 47                         |      | 53   | %     |        |

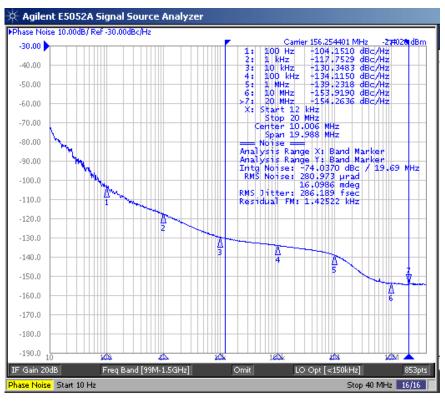

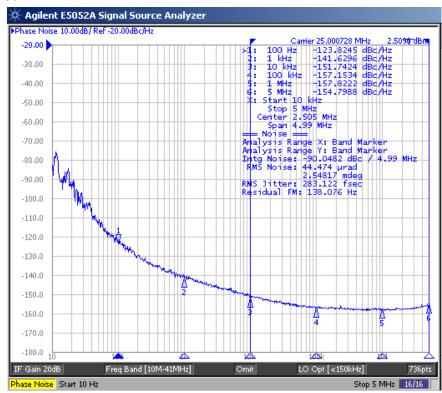

|                     | T                               | 12kHz-20MHz @ 156.25MHz,<br>25MHz Xtal input |                            |      | 0.3  | 0.4   | ps     |

| tjphase             | Integrated phase jitter (RMS)   | 10kHz-5MHz @<br>Xtal input                   | 25MHz, 25MHz               |      | 0.33 | 0.4   | ps     |

| tj <sub>c-c</sub>   | Cycle to cycle jitter           |                                              |                            |      | 28   | 30    | ps     |

| tj <sub>Pk-Pk</sub> | Peak to Peak jitter             |                                              |                            |      | 30   | 35    | ps     |

|                     |                                 |                                              | Offset 1kHz                |      | -117 |       |        |

|                     |                                 | 156.25MHz,                                   | Offset 10kHz               |      | -130 |       |        |

| $f_N$               | Single-Side Band Phase<br>Noise | 25MHz Xtal                                   | Offset 100kHz              |      | -134 |       | dBc/Hz |

|                     | 110130                          | input                                        | Offset 1MHz                |      | -139 |       |        |

|                     |                                 |                                              | Offset 10MHz               |      | -154 |       |        |

# **AC Output Characteristics Cont.**

$T_A$ =-40C to 85C;  $V_{DD}$ =3.3V±10%,  $V_{DD\_O}$ =3.3V±10%

| Symbol               | Parameters                | Condition                               | Min. | Тур. | Max. | Units |

|----------------------|---------------------------|-----------------------------------------|------|------|------|-------|

|                      |                           | V <sub>DD</sub> , 50mVpp, 10k-1.5MHz    |      | -52  |      |       |

|                      | Power Supply Noise Rejec- | V <sub>DDA</sub> , 50mVpp, 10k-1.5MHz   |      | -65  |      |       |

| PSNR                 | tion                      | V <sub>DD_Ox</sub> , 50mVpp, 10k-1.5MHz |      | -50  |      | dBc   |

| t <sub>STARTUP</sub> | Start time                |                                         |      |      | 10   | ms    |

| t <sub>LOCK</sub>    | PLL lock time             |                                         |      |      | 20   | ms    |

#### Note:

- 1.  $V_{DD\_O}$ = 3.3 is not valid with  $V_{DD}$ = 2.5V

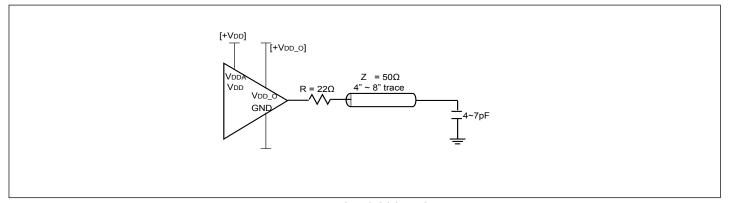

- 2. Normal mode: All measurements are based on 20% to 80% of the single-ended waveform, Load is 4" trace and 4pF.

- 3. Slow mode: All measurements are based on 20% to 80% of the single-ended waveform, Load is 8" trace and 7pF.

# Serial Data Interface (I<sup>2</sup>C compatible)

PI6LC48S25B is a slave only device that supports block read and block write protocol using a single 7-bit address and read/write bit as shown below.

Read and write block transfers can be stopped after any complete byte transfer.

For full electrical I2C compliance, it is recommended to use external pull-up resistors for SDATA and SCLK. The internal pull-up resistors have a size of  $50k\Omega$  typical.

#### **Address Assignment**

| A6 | A5 | A4 | A3 | A2 | A1 | A0                       | R/W |

|----|----|----|----|----|----|--------------------------|-----|

| 1  | 1  | 0  | 1  | 1  | 1  | I <sup>2</sup> C_ADR_SEL | 1/0 |

#### **How to Write**

| 1 bit     | 7 bits  | 1 bit | 1 bit | 8 bits    | 1 bit | 8 bits    | 1 bit | 8 bits    | 1 bit | 1 bit    |

|-----------|---------|-------|-------|-----------|-------|-----------|-------|-----------|-------|----------|

| Start bit | Address | W(0)  | Ack   | Data Byte | A alr | Data Byte | Ack   | Data Byte | Ack   | Stop bit |

| Start bit | Address | W(0)  | ACK   | (D)       | Ack   | (D+1)     | ACK   | <br>(D+N) | ACK   | Stop bit |

#### **How to Read**

| 1 bit     | 7 bits  | 1 bit | 1 bit | 8 bits           | 1 bit | 8 bits             | 1 bit | 8 bits                 | 1 bit | 1 bit    |

|-----------|---------|-------|-------|------------------|-------|--------------------|-------|------------------------|-------|----------|

| Start bit | Address | R(1)  | Ack   | Data Byte<br>(D) | Ack   | Data Byte<br>(D+1) | Ack   | <br>Data Byte<br>(D+N) | Ack   | Stop bit |

# **Output Frequency I2C bit Control Table**

| FS_A (2-bit) | Bank A Freq. |

|--------------|--------------|

| 0 0          | 156.25MHz    |

| 0 1          | 312.5MHz     |

| 1 0          | 125MHz       |

| 1 1          | 100MHz       |

| FS_B (2-bit) | Bank B Freq. |

|--------------|--------------|

| 0 0          | 156.25MHz    |

| 0 1          | 50MHz        |

| 1 0          | 125MHz       |

| 11           | 100MHz       |

| FS_C (2-bit) | Bank C Freq. |

|--------------|--------------|

| 0 0          | 156.25MHz    |

| 0 1          | 100MHz       |

| 1 0          | 125MHz       |

| 1 1          | 50MHz        |

| FS_D0 (2-bit) | Diff Freq. |

|---------------|------------|

| 0 0           | 156.25MHz  |

| 0 1           | $f_{IN}$   |

| 1 0           | 125MHz     |

| 1 1           | 100MHz     |

| FS_D1 (2-bit) | CMOS Freq.      |  |  |  |

|---------------|-----------------|--|--|--|

| 0 0           | Output disabled |  |  |  |

| 0 1           | $f_{IN}$        |  |  |  |

| 1 0           | 125MHz          |  |  |  |

| 1 1           | 100MHz          |  |  |  |

# **Input Frequency I2C bit Control Table**

| INFREQ_SEL (2-bit) | Input Freq. |  |  |

|--------------------|-------------|--|--|

| 0 0                | 25MHz       |  |  |

| 0 1                | 156.25MHz   |  |  |

| 1 0                | 125MHz      |  |  |

| 11                 | 100MHz      |  |  |

# **Byte 0: Output Frequency Selection Register**

| Bit | Control Function | Description              | Туре | Power Up<br>Condition | 0                                       | 1            |

|-----|------------------|--------------------------|------|-----------------------|-----------------------------------------|--------------|

| 7   | FS_C (1)         | David Contract limits    | RW   | 0                     | See FS_C I <sup>2</sup> C co            |              |

| 6   | FS_C (0)         | Bank C output divider    | RW   | 0                     | See FS_C1 Cc                            | ontrol table |

| 5   | FS_B (1)         | D 1 D 4 1 1 1            | RW   | 0                     | 2                                       |              |

| 4   | FS_B (0)         | Bank B output divider    | RW   | 0                     | See FS_B I <sup>2</sup> C co            | ntrol table  |

| 3   | FS_A (1)         | David A antique d'inidia | RW   | 0                     | See FS_A I <sup>2</sup> C control table |              |

| 2   | FS_A (0)         | Bank A output divider    | RW   | 0                     |                                         |              |

| 1   | Vendor ID        |                          | RW   | 0                     |                                         |              |

| 0   | Vendor ID        |                          | RW   | 0                     |                                         |              |

# Byte 1: Output Frequency Selection and Misc. Register

| Bit | Control Function             | Description                                              | Туре | Power Up<br>Condition | 0                                        | 1                |

|-----|------------------------------|----------------------------------------------------------|------|-----------------------|------------------------------------------|------------------|

| 7   | I <sup>2</sup> C pin control | Determine external pins or I <sup>2</sup> C control mode | RW   | 0                     | External pins                            | I <sup>2</sup> C |

| 6   | I2C_ADR_SEL                  | Select I <sup>2</sup> C write address                    | RW   | 0                     | DC(h)                                    | DE(h)            |

| 5   | INFREQ_SEL (1)               | T                                                        | RW   | 0                     | See INFREQ_SEL I <sup>2</sup> C control  |                  |

| 4   | INFREQ_SEL (0)               | Input frequency selection                                | RW   | 0                     | table                                    |                  |

| 3   | FS_D1 (1)                    | Parala D CMOS and and discillate                         | RW   | 1                     | See FS_D1 I <sup>2</sup> C control table |                  |

| 2   | FS_D1 (0)                    | Bank D CMOS output divider                               | RW   | 1                     | See FS_DIT C                             | control table    |

| 1   | FS_D0 (1)                    | Dank D. Diff autment dividen                             | RW   | 1                     | See FS_D0 I <sup>2</sup> C               | aontuol tabla    |

| 0   | FS_D0 (0)                    | Bank D Diff. output divider                              | RW   | 1                     | see rs_D01 C                             | control table    |

10

# Byte 2: Output Enable Selection for Bank A and Bank B Register

| Bit | <b>Control Function</b> | Description               | Туре | Power Up<br>Condition | 0      | 1       |

|-----|-------------------------|---------------------------|------|-----------------------|--------|---------|

| 7   | Reserved                |                           |      |                       |        |         |

| 6   | OE for QB5              | Output enable bit for QB5 | RW   | 0                     | Enable | Disable |

| 5   | OE for QB4              | Output enable bit for QB4 | RW   | 0                     | Enable | Disable |

| 4   | OE for QB3              | Output enable bit for QB3 | RW   | 0                     | Enable | Disable |

| 3   | OE for QB2              | Output enable bit for QB2 | RW   | 0                     | Enable | Disable |

| 2   | OE for QB1              | Output enable bit for QB1 | RW   | 0                     | Enable | Disable |

| 1   | OE for QB0              | Output enable bit for QB0 | RW   | 0                     | Enable | Disable |

| 0   | OE for QA               | Output enable bit for QA  | RW   | 0                     | Enable | Disable |

# Byte 3: Output Enable and Output Type Selection for Bank C and D Register

| Bit | Control Function | Description                        | Туре | Power Up<br>Condition | 0      | 1       |

|-----|------------------|------------------------------------|------|-----------------------|--------|---------|

| 7   | Reserved         |                                    |      |                       |        |         |

| 6   | QD0              | Output Type Select QD Diff. output | RW   | 0                     | LVPECL | LVDS    |

| 5   | QC1              | Output Type Select QC1             | RW   | 0                     | LVPECL | LVDS    |

| 4   | QC0              | Output Type Select QC0             | RW   | 0                     | LVPECL | LVDS    |

| 3   | OE for QD1       | Output enable bit for QD1          | RW   | 0                     | Enable | Disable |

| 2   | OE for QD0       | Output enable bit for QD0          | RW   | 0                     | Enable | Disable |

| 1   | OE for QC1       | Output enable bit for QC1          | RW   | 0                     | Enable | Disable |

| 0   | OE for QC0       | Output enable bit for QC0          | RW   | 0                     | Enable | Disable |

# Byte 4: Output Type Selection for Bank A and Bank B Register

| Bit | Control Function | Description            | Туре | Power Up<br>Condition | 0      | 1    |

|-----|------------------|------------------------|------|-----------------------|--------|------|

| 7   | Reserved         |                        |      |                       |        |      |

| 6   | QB5              | Output Type Select QB5 | RW   | 0                     | LVPECL | LVDS |

| 5   | QB4              | Output Type Select QB4 | RW   | 0                     | LVPECL | LVDS |

| 4   | QB3              | Output Type Select QB3 | RW   | 0                     | LVPECL | LVDS |

| 3   | QB2              | Output Type Select QB2 | RW   | 0                     | LVPECL | LVDS |

| 2   | QB1              | Output Type Select QB1 | RW   | 0                     | LVPECL | LVDS |

| 1   | QB0              | Output Type Select QB0 | RW   | 0                     | LVPECL | LVDS |

| 0   | QA               | Output Type Select QA  | RW   | 0                     | LVPECL | LVDS |

# Byte 5: Misc. Register

| Bit | Control Function | Description                                  | Туре | Power Up<br>Condition | 0              | 1                    |

|-----|------------------|----------------------------------------------|------|-----------------------|----------------|----------------------|

| 7   | Reserved         |                                              |      |                       |                |                      |

| 6   | Reserved         |                                              |      | 0                     |                |                      |

| 5   | Reserved         |                                              |      | 0                     |                |                      |

| 4   | Reserved         |                                              |      | 0                     |                |                      |

| 3   | PLL_BYPASS       | PLL bypass function                          | RW   | 0                     | PLL is enabled | PLL is by-<br>passed |

| 2   | SLEW_CMOS        | Output slew rate control for the CMOS output | RW   | 0                     | Normal mode    | Slow mode            |

| 1   | Reserved         |                                              |      | 0                     |                |                      |

| 0   | IN_SEL           | Input selection                              | RW   | 0                     | Crystal        | Reference            |

12

# **Phase Noise Plots** 156.25MHz LVDS Clock

#### 25MHz LVPECL Clock

13

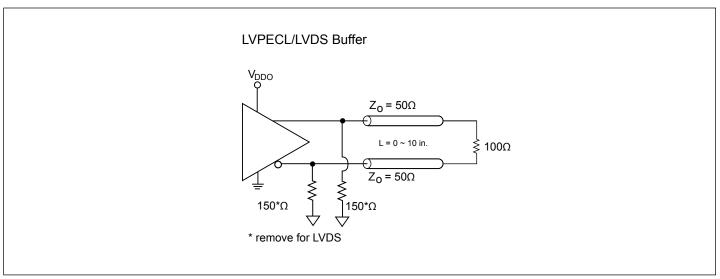

Figure 1. LVPECL and LVDS Test Circuit

Figure 2. CMOS Test Circuit

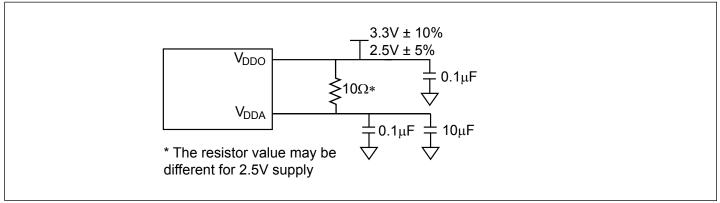

Figure 3. Power Supply Filter

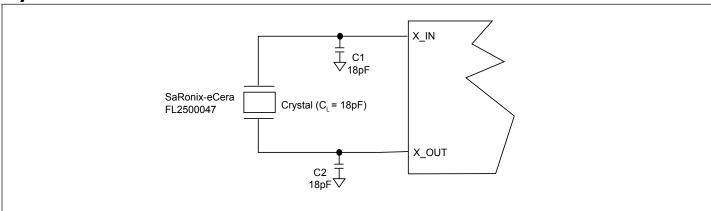

### **Crystal Circuit Connection**

The following diagram shows PI6LC48S25B crystal circuit connection with a parallel crystal. For the CL=18pF crystal, it is suggested to use C1=18pF, C2=18pF. C1 and C2 can be adjusted to fine tune to the target ppm of crystal oscillator according to different board layouts.

**Crystal Oscillator Circuit**

# **Crystal Circuit Oscillator**

### **Recommended Crystal Specification**

#### **Pericom recommends:**

- a) FY2500081, SMD 5x3.2(4P), 25MHz, CL=18pF, +/-30ppm, http://www.pericom.com/pdf/datasheets/se/FY\_F9.pdf

- b) FL2500047, SMD 3.2x2.5(4P), 25MHz, CL=18pF, +/-20ppm, http://www.pericom.com/pdf/datasheets/se/FL.pdf

# **Part Marking**

ZBB Package

YY: Year

WW: Workweek

1st X: Assembly Code

2nd X: Fab Code

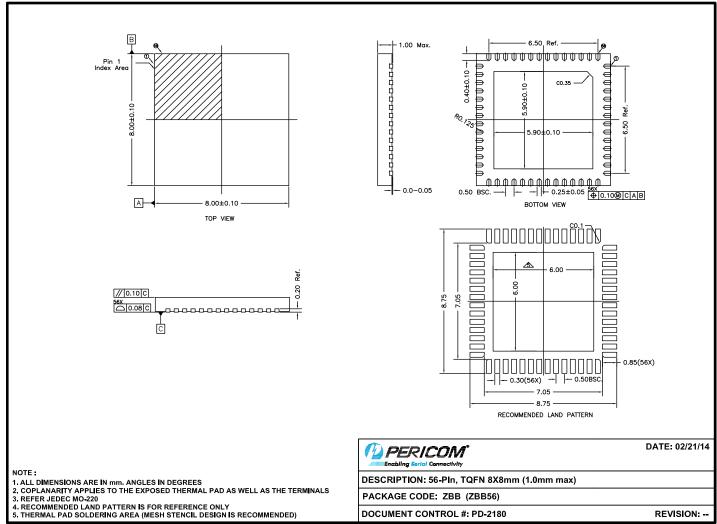

# Packaging Mechanical: 56-TQFN (ZBB)

#### For latest package info.

$please\ check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanicals-and-thermal-characteristics/packaging-mechanical-and-thermal-characteristics/packaging-mecha$

# Ordering Information<sup>(1-3)</sup>

| Ordering Code     | Package Code | Package Description             | <b>Operating Temperature</b> |

|-------------------|--------------|---------------------------------|------------------------------|

| PI6LC48S25BZBBIEX | ZBB          | 56-Pin, 8x8mm, 1.0mm max (TQFN) | Industrial                   |

#### Notes:

- 1. EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. All applicable RoHS exemptions applied.

- 2. See http://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. Thermal characteristics can be found on the company web site at www.diodes.com/design/support/packaging/

- 3. E = Pb-free and Green

- 4. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com

# **OUR CERTIFICATE**

DiGi provide top-quality products and perfect service for customer worldwide through standardization, technological innovation and continuous improvement. DiGi through third-party certification, we striciy control the quality of products and services. Welcome your RFQ to Email: Info@DiGi-Electronics.com

Tel: +00 852-30501935

RFQ Email: Info@DiGi-Electronics.com